为实现DSP与FPGA之间实现交换数据,通常采用DSP的EMIF外部存储器借口与FPGA 片内的BRAM,

BRAM 采用双口BRAM ,一个端口给DSP EMIF接口,另一个端口给 FPGA 片内逻辑。

FPGA 片内逻辑对BRAM 的读写在上一文中以实现,本文主要实现DSP 对 BRAM 的读写。

DSP 片内EMIF 接口信号如下图:

信号说明:

————————————————共用信号——————————————————

ECLKIN EMIF外部输入时钟

ED[63:0] EMIF 数据总线

EA[19:0] ENIF 地址总线

BA[1:0] 当EMIF 配置为8位或是16为时,低两位地址线

BE[7:0] 字节使能

CE2 CE2空间片选使能 ,低有效

CE3 CE3空间片选使能 ,低有效

CE4 CE4空间片选使能 ,低有效

CE5 CE5空间片选使能 ,低有效

————————————————异步信号——————————————————

ARDY 异步Ready输入信号

R/W 异步读写信号

AOE 异步输出使能信号

AWE 异步写选通信号

————————————————同步信号——————————————————

ECLKOUT EMIF输出时钟

SOE 同步输出使能

SADS/SRE 当寄存器CEnCFG中的R_ENABLE为1时,该信号为同步读使能信号

当寄存器CEnCFG中的R_ENABLE为0时,该信号为同步地址选通信号

SWE 同步写使能信号

————————————————保持信号——————————————————

HOLD 总线保持请求信号

HOLDA 应答请求信号

BUSREQ 总线请求信号

对于TMS320C6455的EMIF 存储空间映射图如下:

信号说明:

————————————————共用信号——————————————————

ECLKIN EMIF外部输入时钟

ED[63:0] EMIF 数据总线

EA[19:0] ENIF 地址总线

BA[1:0] 当EMIF 配置为8位或是16为时,低两位地址线

BE[7:0] 字节使能

CE2 CE2空间片选使能 ,低有效

CE3 CE3空间片选使能 ,低有效

CE4 CE4空间片选使能 ,低有效

CE5 CE5空间片选使能 ,低有效

————————————————异步信号——————————————————

ARDY 异步Ready输入信号

R/W 异步读写信号

AOE 异步输出使能信号

AWE 异步写选通信号

————————————————同步信号——————————————————

ECLKOUT EMIF输出时钟

SOE 同步输出使能

SADS/SRE 当寄存器CEnCFG中的R_ENABLE为1时,该信号为同步读使能信号

当寄存器CEnCFG中的R_ENABLE为0时,该信号为同步地址选通信号

SWE 同步写使能信号

————————————————保持信号——————————————————

HOLD 总线保持请求信号

HOLDA 应答请求信号

BUSREQ 总线请求信号

对于TMS320C6455的EMIF 存储空间映射图如下:

从上图可看出,每个存储空间有8M 的空间,都可以配置为同步和异步接口

由于这里FPGA内部的双口RAM 采用了同步模式,并将BRAM挂接在CE4空间下,所以EMIF 的CE4 配置为同步模式

采用同步模式,首先是时钟,将ECLKOUT 与双口RAM 的时钟引脚相连

使能信号与双口RAM 的时钟引脚相连

读写信号与双口RAM 读写相连,地址总线,数据总线。

由上面的分析,FPGA 与DSP 之间的连接如下图:

从上图可看出,每个存储空间有8M 的空间,都可以配置为同步和异步接口

由于这里FPGA内部的双口RAM 采用了同步模式,并将BRAM挂接在CE4空间下,所以EMIF 的CE4 配置为同步模式

采用同步模式,首先是时钟,将ECLKOUT 与双口RAM 的时钟引脚相连

使能信号与双口RAM 的时钟引脚相连

读写信号与双口RAM 读写相连,地址总线,数据总线。

由上面的分析,FPGA 与DSP 之间的连接如下图:

其中,FPGA 对双口RAM 的读写上一篇中一实现,下面实现DSP对RAM 读写的实现

DSP 的配置,以实现EMIF 的CE4空间配置为同步模式,由于BRAM 挂接在CE4空间,所以要配置CE4CFG寄存器

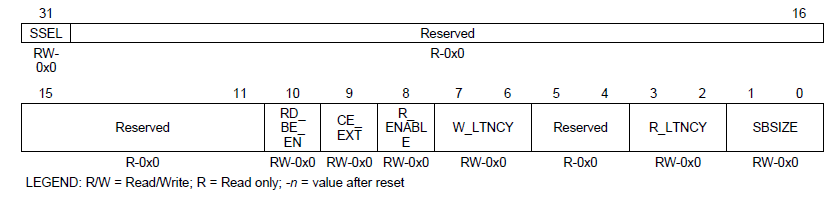

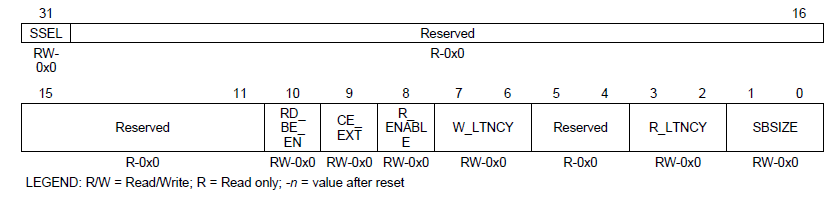

先来看看该寄存器的说明,如下图:

其中,FPGA 对双口RAM 的读写上一篇中一实现,下面实现DSP对RAM 读写的实现

DSP 的配置,以实现EMIF 的CE4空间配置为同步模式,由于BRAM 挂接在CE4空间,所以要配置CE4CFG寄存器

先来看看该寄存器的说明,如下图:

寄存器说明:

——————————————————————————————————

SSEL 寄存器选择,1同步存储器,0异步存储器

RD_BE_EN 为1时在同步存储器读期间被驱动,为0时,在同步存储器读期间一直为高,

这个一般情况下都为0,也就是读取是每个字节都有效

CE_EXT 外部同步存储器片选,为1

R_ENABLE 同步存储器读使能模式,为1时选择ASRE,即同步读使能信号,为0时同步地址选通,所以这里为1

W_LTNCY 为0时,0时钟周期写延时

为1时,1时钟周期写延时

为2时,2时钟周期写延时

为3时,3时钟周期写延时,从上一篇文中FPGA 内部双口RAM 可知写延时为0,这里配置为0

R_LTNCY 为0时,0时钟周期读延时

为1时,1时钟周期读延时

为2时,2时钟周期读延时,从上一篇文中FPGA 内部双口RAM 可知读延时为2,这里配置为2

SBSIZE 为0时,数据位宽为8

为1时,数据位宽为16

为2时,数据位宽为32

为3时,数据位宽为64

——————————————————————————————————

如何实现上述寄存器的配置,在DSP下,通常采用CSL(片上支持库)

使用CSL配置EMIFA模块时,主要的步骤如下:

1. 使能设备EMIFA模块

寄存器说明:

——————————————————————————————————

SSEL 寄存器选择,1同步存储器,0异步存储器

RD_BE_EN 为1时在同步存储器读期间被驱动,为0时,在同步存储器读期间一直为高,

这个一般情况下都为0,也就是读取是每个字节都有效

CE_EXT 外部同步存储器片选,为1

R_ENABLE 同步存储器读使能模式,为1时选择ASRE,即同步读使能信号,为0时同步地址选通,所以这里为1

W_LTNCY 为0时,0时钟周期写延时

为1时,1时钟周期写延时

为2时,2时钟周期写延时

为3时,3时钟周期写延时,从上一篇文中FPGA 内部双口RAM 可知写延时为0,这里配置为0

R_LTNCY 为0时,0时钟周期读延时

为1时,1时钟周期读延时

为2时,2时钟周期读延时,从上一篇文中FPGA 内部双口RAM 可知读延时为2,这里配置为2

SBSIZE 为0时,数据位宽为8

为1时,数据位宽为16

为2时,数据位宽为32

为3时,数据位宽为64

——————————————————————————————————

如何实现上述寄存器的配置,在DSP下,通常采用CSL(片上支持库)

使用CSL配置EMIFA模块时,主要的步骤如下:

1. 使能设备EMIFA模块

2. 配置CEnCFG寄存器

3. 初始化EMIFA模块

4. 打开EMIFA模块

5. 把2中配置的参数设置到打开的EMIFA模块中 所须包含的头文件:

信号说明:

————————————————共用信号——————————————————

ECLKIN EMIF外部输入时钟

ED[63:0] EMIF 数据总线

EA[19:0] ENIF 地址总线

BA[1:0] 当EMIF 配置为8位或是16为时,低两位地址线

BE[7:0] 字节使能

CE2 CE2空间片选使能 ,低有效

CE3 CE3空间片选使能 ,低有效

CE4 CE4空间片选使能 ,低有效

CE5 CE5空间片选使能 ,低有效

————————————————异步信号——————————————————

ARDY 异步Ready输入信号

R/W 异步读写信号

AOE 异步输出使能信号

AWE 异步写选通信号

————————————————同步信号——————————————————

ECLKOUT EMIF输出时钟

SOE 同步输出使能

SADS/SRE 当寄存器CEnCFG中的R_ENABLE为1时,该信号为同步读使能信号

当寄存器CEnCFG中的R_ENABLE为0时,该信号为同步地址选通信号

SWE 同步写使能信号

————————————————保持信号——————————————————

HOLD 总线保持请求信号

HOLDA 应答请求信号

BUSREQ 总线请求信号

对于TMS320C6455的EMIF 存储空间映射图如下:

信号说明:

————————————————共用信号——————————————————

ECLKIN EMIF外部输入时钟

ED[63:0] EMIF 数据总线

EA[19:0] ENIF 地址总线

BA[1:0] 当EMIF 配置为8位或是16为时,低两位地址线

BE[7:0] 字节使能

CE2 CE2空间片选使能 ,低有效

CE3 CE3空间片选使能 ,低有效

CE4 CE4空间片选使能 ,低有效

CE5 CE5空间片选使能 ,低有效

————————————————异步信号——————————————————

ARDY 异步Ready输入信号

R/W 异步读写信号

AOE 异步输出使能信号

AWE 异步写选通信号

————————————————同步信号——————————————————

ECLKOUT EMIF输出时钟

SOE 同步输出使能

SADS/SRE 当寄存器CEnCFG中的R_ENABLE为1时,该信号为同步读使能信号

当寄存器CEnCFG中的R_ENABLE为0时,该信号为同步地址选通信号

SWE 同步写使能信号

————————————————保持信号——————————————————

HOLD 总线保持请求信号

HOLDA 应答请求信号

BUSREQ 总线请求信号

对于TMS320C6455的EMIF 存储空间映射图如下:

从上图可看出,每个存储空间有8M 的空间,都可以配置为同步和异步接口

由于这里FPGA内部的双口RAM 采用了同步模式,并将BRAM挂接在CE4空间下,所以EMIF 的CE4 配置为同步模式

采用同步模式,首先是时钟,将ECLKOUT 与双口RAM 的时钟引脚相连

使能信号与双口RAM 的时钟引脚相连

读写信号与双口RAM 读写相连,地址总线,数据总线。

由上面的分析,FPGA 与DSP 之间的连接如下图:

从上图可看出,每个存储空间有8M 的空间,都可以配置为同步和异步接口

由于这里FPGA内部的双口RAM 采用了同步模式,并将BRAM挂接在CE4空间下,所以EMIF 的CE4 配置为同步模式

采用同步模式,首先是时钟,将ECLKOUT 与双口RAM 的时钟引脚相连

使能信号与双口RAM 的时钟引脚相连

读写信号与双口RAM 读写相连,地址总线,数据总线。

由上面的分析,FPGA 与DSP 之间的连接如下图:

其中,FPGA 对双口RAM 的读写上一篇中一实现,下面实现DSP对RAM 读写的实现

DSP 的配置,以实现EMIF 的CE4空间配置为同步模式,由于BRAM 挂接在CE4空间,所以要配置CE4CFG寄存器

先来看看该寄存器的说明,如下图:

其中,FPGA 对双口RAM 的读写上一篇中一实现,下面实现DSP对RAM 读写的实现

DSP 的配置,以实现EMIF 的CE4空间配置为同步模式,由于BRAM 挂接在CE4空间,所以要配置CE4CFG寄存器

先来看看该寄存器的说明,如下图:

寄存器说明:

——————————————————————————————————

SSEL 寄存器选择,1同步存储器,0异步存储器

RD_BE_EN 为1时在同步存储器读期间被驱动,为0时,在同步存储器读期间一直为高,

这个一般情况下都为0,也就是读取是每个字节都有效

CE_EXT 外部同步存储器片选,为1

R_ENABLE 同步存储器读使能模式,为1时选择ASRE,即同步读使能信号,为0时同步地址选通,所以这里为1

W_LTNCY 为0时,0时钟周期写延时

为1时,1时钟周期写延时

为2时,2时钟周期写延时

为3时,3时钟周期写延时,从上一篇文中FPGA 内部双口RAM 可知写延时为0,这里配置为0

R_LTNCY 为0时,0时钟周期读延时

为1时,1时钟周期读延时

为2时,2时钟周期读延时,从上一篇文中FPGA 内部双口RAM 可知读延时为2,这里配置为2

SBSIZE 为0时,数据位宽为8

为1时,数据位宽为16

为2时,数据位宽为32

为3时,数据位宽为64

——————————————————————————————————

如何实现上述寄存器的配置,在DSP下,通常采用CSL(片上支持库)

使用CSL配置EMIFA模块时,主要的步骤如下:

1. 使能设备EMIFA模块

寄存器说明:

——————————————————————————————————

SSEL 寄存器选择,1同步存储器,0异步存储器

RD_BE_EN 为1时在同步存储器读期间被驱动,为0时,在同步存储器读期间一直为高,

这个一般情况下都为0,也就是读取是每个字节都有效

CE_EXT 外部同步存储器片选,为1

R_ENABLE 同步存储器读使能模式,为1时选择ASRE,即同步读使能信号,为0时同步地址选通,所以这里为1

W_LTNCY 为0时,0时钟周期写延时

为1时,1时钟周期写延时

为2时,2时钟周期写延时

为3时,3时钟周期写延时,从上一篇文中FPGA 内部双口RAM 可知写延时为0,这里配置为0

R_LTNCY 为0时,0时钟周期读延时

为1时,1时钟周期读延时

为2时,2时钟周期读延时,从上一篇文中FPGA 内部双口RAM 可知读延时为2,这里配置为2

SBSIZE 为0时,数据位宽为8

为1时,数据位宽为16

为2时,数据位宽为32

为3时,数据位宽为64

——————————————————————————————————

如何实现上述寄存器的配置,在DSP下,通常采用CSL(片上支持库)

使用CSL配置EMIFA模块时,主要的步骤如下:

1. 使能设备EMIFA模块2. 配置CEnCFG寄存器

3. 初始化EMIFA模块

4. 打开EMIFA模块

5. 把2中配置的参数设置到打开的EMIFA模块中 所须包含的头文件:

#include

#include

CE4空间首地址的定义:

#define EMIFA_CE4_BASE_ADDR (0xC0000000u)

存储器类型的定义:

#define EMIFA_MEMTYPE_ASYNC 0

#define EMIFA_MEMTYPE_SYNC 1

定义EMIF实例句柄:

CSL_EmifaHandle hEmifa;

使能EMIF:

CSL_FINST(((CSL_DevRegs*)CSL_DEV_REGS)->PERCFG1, DEV_PERCFG1_EMIFACTL, ENABLE);

定义同步存储器参数:

#define CSL_EMIFA_SYNCCFG_RLTNCY_PARAMETER 2//读延时2周期

#define CSL_EMIFA_SYNCCFG_SBSIZE_PARAMETER 2//32位数据总线

#define CSL_EMIFA_SYNCCFG_READEN_PARAMETER 1//同步读使能

定义CE4CFG寄存器参数宏:

#define CSL_EMIFA_SYNCCFG_PARAMETER {

(Uint8)CSL_EMIFA_SYNCCFG_READBYTEEN_DEFAULT,

(Uint8)CSL_EMIFA_SYNCCFG_CHIPENEXT_DEFAULT,

(Uint8)CSL_EMIFA_SYNCCFG_READEN_PARAMETER,

(Uint8)CSL_EMIFA_SYNCCFG_WLTNCY_DEFAULT,

(Uint8)CSL_EMIFA_SYNCCFG_RLTNCY_PARAMETER,

(Uint8)CSL_EMIFA_SYNCCFG_SBSIZE_PARAMETER

}

相关变量定义:

CSL_EmifaObj emifaObj;

CSL_Status status;

CSL_EmifaHwSetup hwSetup;

CSL_EmifaHandle hEmifa;

CSL_EmifaMemType syncVal;

CSL_EmifaSync syncMem = CSL_EMIFA_SYNCCFG_PARAMETER;//将上述参数填入存储器变量

配置CE4CFG寄存器:

syncVal.ssel = EMIFA_MEMTYPE_SYNC;

syncVal.async = NULL;

syncVal.sync = &syncMem;

hwSetup.ceCfg[0] = NULL; //对应CE2

hwSetup.ceCfg[1] = NULL; //对应CE3

hwSetup.ceCfg[2] = &syncVal; //对应CE4

hwSetup.ceCfg[3] = NULL; //对应CE5

初始化EMIFA模块:

status = CSL_emifaInit(NULL);

打开EMIFA模块:

hEmifa = CSL_emifaOpen(&emifaObj,CSL_EMIFA,NULL,&status);

将配置的参数设置到打开的EMIFA模块中:

status = CSL_emifaHwSetup(hEmifa,&hwSetup);