class="markdown_views prism-dracula">

参考博文:

https://blog.csdn.net/ruby97/article/details/7535524

https://blog.csdn.net/ruby97/article/details/7538125

https://blog.csdn.net/youbin2013/article/details/52454273

参考文档:

http://www.docin.com/p-543427376.html

https://blog.csdn.net/hongtao_6/article/details/81588724

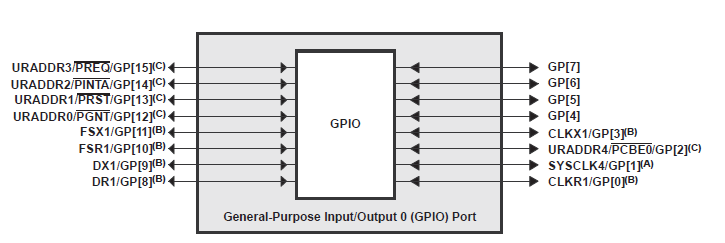

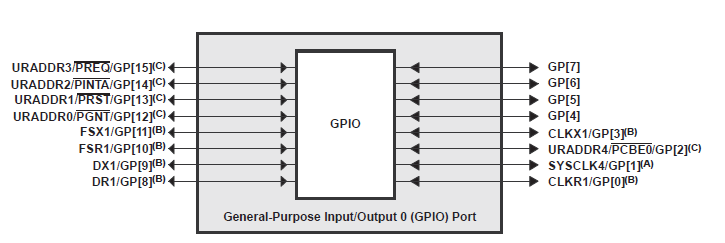

先来看一下与GPIO有关的寄存器组:

然后设置GPIO可作为中断源,需要操作BINTEN寄存器。只需将BINTEN的最低位设置为1即可使能GPIO中断。

最后一步我们需要配置GPIO属性来设置中断方式。涉及到的寄存器有RIS_TRIG 和 FAL_TRIG。但是这两个寄存器不是CPU可以直接访问的,这两个寄存器组可以通过SET_RIS_TRIN、ClR_RIS_TRIG、SET_FAL_TRIN、ClR_FAL_TRIG这四个寄存器来间接访问。

RIS_TRIG 和 FAL_TRIG这两个寄存器组的每一位对应GPn的一个引脚,若我们想要设置GPIO4为下降沿触发的中断,则设置RIS_TRIG 和 FAL_TRIG的第四位分别为1,和0即可。如何设置这两位中的1和0呢,我们就需要对SET_RIS_TRIN、ClR_RIS_TRIG、SET_FAL_TRIN、ClR_FAL_TRIG这四个寄存器进行操作了。

我们先来看SET_RIS_TRIN和ClR_RIS_TRIG这两个寄存器,这两个寄存器是对RIS_TRIG寄存器进行操作的,主要功能是对RIS_TRIG寄存器对应的位进行置位和清除的操作。同理SET_FAL_TRIN和ClR_FAL_TRIG寄存器是对FLA_TRIG进行置位和清除的操作。SET开头的寄存器的对应位设置为1,则RIS_TRIG和FLA_TRIG的对应为会被设置成1,即置位。CLR开头的寄存器的对应位设置为1,则RIS_TRIG和FLA_TRIG的对应为会被设置成0,即清除。

因此我们要把RIS_TRIG 和 FAL_TRIG的第四位分别设置为1和0。则需设置SET_RIS_TRIN和ClR_FAL_TRIG的第四位为1即可。这样一来,我们就配置了GPIO4作为了上升沿除法的中断。GPIO配置到此结束,接下来开始进行中断的配置。

首先进行事件的绑定,我们要用到的中断是INT[15:4],即普通中断,INT[15:4]的上一级是Interrupt Selector,它的功能是对所有中断事件进行选择性映射。

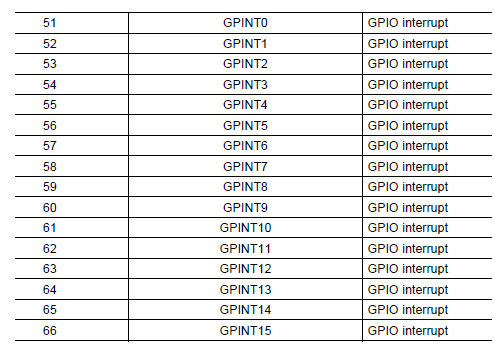

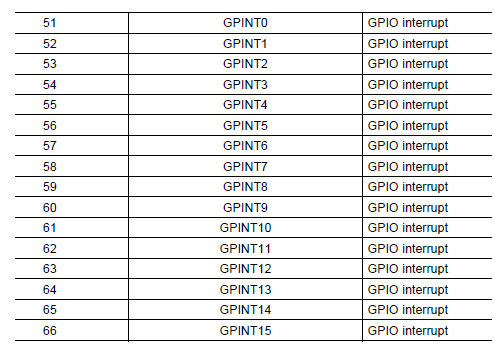

EVENT[127:4]是系统事件,这个事件的编号根据芯片的不同而不同,拿6455来说,部分映射情况如下面两个图片所示:

接下来我们通过操作INTMUXn寄存器来进行事件的绑定,若我们想要把刚才配置的GPIO4作为INT4中断,我们需要配置INTMUX1中INTSEL4中的内容(INTSEL4-15对应4-15的中断号),6455芯片中GPIO4对应的事件号为55,即设置INTMUX1的低七位0x37即可。

绑定事件后我们需要清除中断标志以及使能中断号。这两步分别用到了ICR和IER寄存器。

中断清除寄存器(ICR)可以手动清除中断标志寄存器(IFR)中的可屏蔽中断位。对ICR的IC4-IC15位写1,则引起IFR对应标志位置0。对ICR的任何位写0无效,清除ICR的任何位都不影响NMI和复位。我们设置ICR = 0xFFFF,来清除所有中断标志位。

接下来进行中断号的使能。IER的bit0对应于复位,该位可读(读作1)不可写,由于bit0始终为1,所以复位总被使能。Bit IE4-IE15写1或者写0分别使能或禁止相关中断。NMIE = 0时,禁止所有非复位中断;NMIE = 1时,GIE和相应的IER位一起使能INT15-INT4中断,对NMIE写0无效。只有复位和NMI发生时清零,NMIE的置1靠执行B NRP指令和写1完成。

注意:一定要使能NMIE,否则对中断号的使能无效。

使能中断NMI和IE14-IE15: IER= 0x0000C003。

最后一步,使能全局中断,需要操作CSR寄存器。状态控制寄存器有两个位用于控制中断:GIE和PGIE,GIE-全局中断使能(global interruppt enable)是状态控制寄存器的(CSR)的bit0,控制GIE的值可以使能或者禁止所有的可屏蔽中断。PGIE是控制寄存器(CSR)的bit1,PGIE包含之前的GIE,当处理可屏蔽中断期间PGIE保存GIE的值,而GIE被清零,这样在处理一个可屏蔽中断期间,就防止了另外一个可屏蔽中断的发送,当中断返回时,通过写程序指令把PGIE的值重新返回到GIE中。

禁止全局中断:CSR = 0x00000100;

使能全局中断:CSR = CSR | 1;

到此中断配置部分结束,我们可以将GPIO4作为INT4中断来进行使用了。

https://blog.csdn.net/ruby97/article/details/7535524

https://blog.csdn.net/ruby97/article/details/7538125

https://blog.csdn.net/youbin2013/article/details/52454273

参考文档:

http://www.docin.com/p-543427376.html

https://blog.csdn.net/hongtao_6/article/details/81588724

本文主要介绍配置GPIO端口为中断的过程中的一些寄存器的相关操作,参考博文中对用CSL库进行配置的方法已经介绍的非常详细了。理论上本文涉及到的寄存器对于C6000系列是通用的,但由于参考了一些其他文档,如C64X系列以及C6455,所以可能存在细微的差异。将GPIO配置成中断主要分为两步来完成,首先需要对GPIO进行配置,然后对中断进行配置。

GPIO的相关配置

首先需要操作PERCFG0寄存器来使能GPIO模块,只需将GPIOCLT设置为1即可。

先来看一下与GPIO有关的寄存器组:

然后设置GPIO可作为中断源,需要操作BINTEN寄存器。只需将BINTEN的最低位设置为1即可使能GPIO中断。

最后一步我们需要配置GPIO属性来设置中断方式。涉及到的寄存器有RIS_TRIG 和 FAL_TRIG。但是这两个寄存器不是CPU可以直接访问的,这两个寄存器组可以通过SET_RIS_TRIN、ClR_RIS_TRIG、SET_FAL_TRIN、ClR_FAL_TRIG这四个寄存器来间接访问。

RIS_TRIG 和 FAL_TRIG这两个寄存器组的每一位对应GPn的一个引脚,若我们想要设置GPIO4为下降沿触发的中断,则设置RIS_TRIG 和 FAL_TRIG的第四位分别为1,和0即可。如何设置这两位中的1和0呢,我们就需要对SET_RIS_TRIN、ClR_RIS_TRIG、SET_FAL_TRIN、ClR_FAL_TRIG这四个寄存器进行操作了。

我们先来看SET_RIS_TRIN和ClR_RIS_TRIG这两个寄存器,这两个寄存器是对RIS_TRIG寄存器进行操作的,主要功能是对RIS_TRIG寄存器对应的位进行置位和清除的操作。同理SET_FAL_TRIN和ClR_FAL_TRIG寄存器是对FLA_TRIG进行置位和清除的操作。SET开头的寄存器的对应位设置为1,则RIS_TRIG和FLA_TRIG的对应为会被设置成1,即置位。CLR开头的寄存器的对应位设置为1,则RIS_TRIG和FLA_TRIG的对应为会被设置成0,即清除。

因此我们要把RIS_TRIG 和 FAL_TRIG的第四位分别设置为1和0。则需设置SET_RIS_TRIN和ClR_FAL_TRIG的第四位为1即可。这样一来,我们就配置了GPIO4作为了上升沿除法的中断。GPIO配置到此结束,接下来开始进行中断的配置。

中断的相关配置

中断的配置主要分为四步来完成。

首先进行事件的绑定,我们要用到的中断是INT[15:4],即普通中断,INT[15:4]的上一级是Interrupt Selector,它的功能是对所有中断事件进行选择性映射。

EVENT[127:4]是系统事件,这个事件的编号根据芯片的不同而不同,拿6455来说,部分映射情况如下面两个图片所示:

接下来我们通过操作INTMUXn寄存器来进行事件的绑定,若我们想要把刚才配置的GPIO4作为INT4中断,我们需要配置INTMUX1中INTSEL4中的内容(INTSEL4-15对应4-15的中断号),6455芯片中GPIO4对应的事件号为55,即设置INTMUX1的低七位0x37即可。

绑定事件后我们需要清除中断标志以及使能中断号。这两步分别用到了ICR和IER寄存器。

中断清除寄存器(ICR)可以手动清除中断标志寄存器(IFR)中的可屏蔽中断位。对ICR的IC4-IC15位写1,则引起IFR对应标志位置0。对ICR的任何位写0无效,清除ICR的任何位都不影响NMI和复位。我们设置ICR = 0xFFFF,来清除所有中断标志位。

接下来进行中断号的使能。IER的bit0对应于复位,该位可读(读作1)不可写,由于bit0始终为1,所以复位总被使能。Bit IE4-IE15写1或者写0分别使能或禁止相关中断。NMIE = 0时,禁止所有非复位中断;NMIE = 1时,GIE和相应的IER位一起使能INT15-INT4中断,对NMIE写0无效。只有复位和NMI发生时清零,NMIE的置1靠执行B NRP指令和写1完成。

注意:一定要使能NMIE,否则对中断号的使能无效。

使能中断NMI和IE14-IE15: IER= 0x0000C003。

最后一步,使能全局中断,需要操作CSR寄存器。状态控制寄存器有两个位用于控制中断:GIE和PGIE,GIE-全局中断使能(global interruppt enable)是状态控制寄存器的(CSR)的bit0,控制GIE的值可以使能或者禁止所有的可屏蔽中断。PGIE是控制寄存器(CSR)的bit1,PGIE包含之前的GIE,当处理可屏蔽中断期间PGIE保存GIE的值,而GIE被清零,这样在处理一个可屏蔽中断期间,就防止了另外一个可屏蔽中断的发送,当中断返回时,通过写程序指令把PGIE的值重新返回到GIE中。

禁止全局中断:CSR = 0x00000100;

使能全局中断:CSR = CSR | 1;

到此中断配置部分结束,我们可以将GPIO4作为INT4中断来进行使用了。