文章主要介绍了一下,TMS320C6678 DSP的DDR3的硬件设计需要注意的问题以及相应的软件调试的问题。

------作者:jiangwenj02【转载请注明】

一、硬件设计

本设计参考TI公司的样板设计,在样板的基础上,为了节约成本和空间,删除了DDR3的ECC。只留下4片Samsung公司的K4B1G1646G,总内存为512MB。DDR3拥有800、1066、1333、1600等多个数据传输频率,设计使用1333数据传输频率的DDR3,在调试的时候可以使用低频率的传输频率进行逐步调试。

DDR3数据传输速率最高达到1333MHz,属于高速传输线。所以布线的需要进行阻抗匹配。单线阻抗50欧姆,差分线阻抗100欧姆。

DDR3的传输线主要分为数据线,地址线,其它。4片DDR3拥有8组数据线,1组地址线。其中DDR3第n组(n=0...7)数据线包括DQ[8×n......8×(n+1)-1],DQSnP,DQSnN,DMn。剩余的EA[0..15],EBA0,EBA1,ECAS,ECKE,ECS0,EODT0,ERAS,EWE都是地址线。VREFSSTL为电源参考电压线。EMRESETN为复位线。DDRSLRATE0,DDRSLRAT1为控制速率线。

在绘制PCB板时,需要设置约束文件。DDR3的约束有数据线等长,地址线等长,单线阻抗50欧姆,差分线阻抗100欧姆。所以DDR3一共有12组等长约束,8组数据线,4组地址线(DSP DDR3 CONTROL到每个单片DDR3都有一个约束),外加相关差分线的约束。同一组数据线必须在同一个平面,数据线之间的长度相差不能超过20mil,差分线之间的长度相差不能超过2mil。地址线之间的长度相差不能超过20mil。DDR3数据线和地址线布线过程最好只打两个过孔。DDR3高速线不能跨平面分割。做好这几点,DDR3跑在1333MHz的速率基本没问题。

DDR3的连接方式使用fly-by的形式进行连接。注意其他无关的电路线,远离DDR3高速线,个人做的第一版只能跑在800MHz的原因,就是这个地方没做好,第二版改过来之后就可以跑在1333MHz了。

二、软件调试

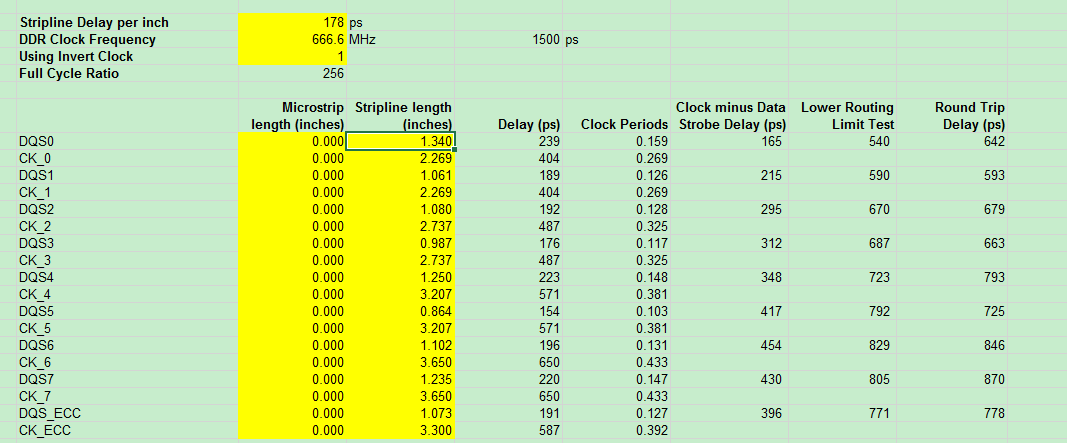

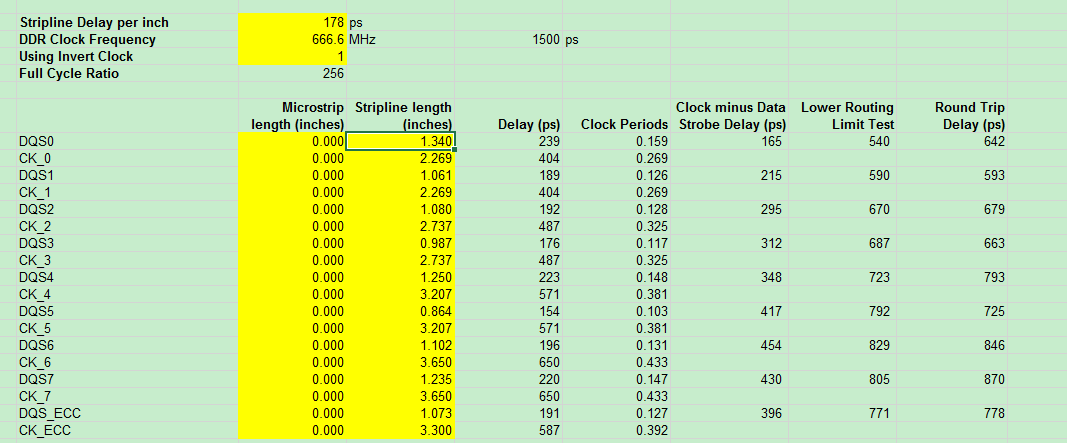

软件调试,选择K1_STK_v1.1提供的开源代码。K1_STK_v1.1中对DDR3的测试代码为Memory_Test工程。因为DDR3的布线长度和官方不一样,所以需要修改DDR3对每组地址线的配置寄存器。寄存器中的数据用DDR3 PHY Calc v10.xlsx计算。

填写内容有,DDR CLOCK FREQUENCY(时钟频率 1333/2,跑在其它速率只需要修改这个值)。修改DQS,CK中Stripline length (inches)(布线线长)的值。没有DDR ECC就不需要填最后的值。可以得到每个数据通道控制寄存器的值。

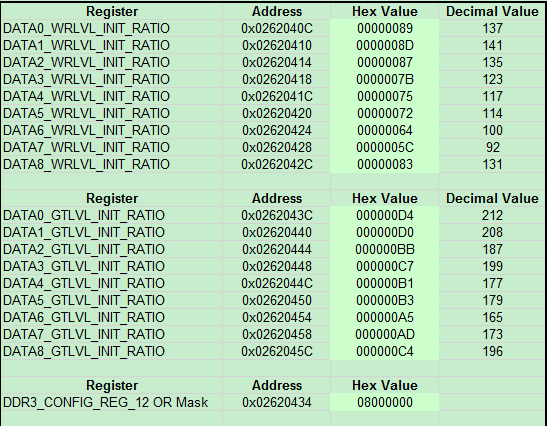

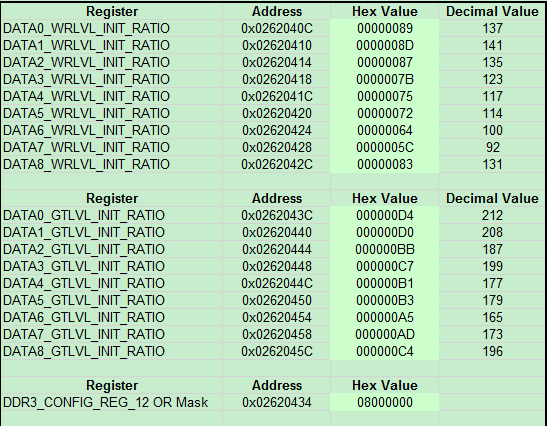

修改Memory_Test工程中,KeyStone_DDR_Init.c文件中的C6678_EVM_DDR_Init函数中对应寄存器的值,如下。 //initial vale for leveling /*WRLVL_INIT_RATIO*/ gpBootCfgRegs->DDR3_CONFIG_REG[2] = 0x89; gpBootCfgRegs->DDR3_CONFIG_REG[3] = 0x8D; gpBootCfgRegs->DDR3_CONFIG_REG[4] = 0x87; gpBootCfgRegs->DDR3_CONFIG_REG[5] = 0x7B; gpBootCfgRegs->DDR3_CONFIG_REG[6] = 0x75; gpBootCfgRegs->DDR3_CONFIG_REG[7] = 0x72; gpBootCfgRegs->DDR3_CONFIG_REG[8] = 0x64; gpBootCfgRegs->DDR3_CONFIG_REG[9] = 0x5C; gpBootCfgRegs->DDR3_CONFIG_REG[10] = 0x83;

/*GTLVL_INIT_RATIO*/ gpBootCfgRegs->DDR3_CONFIG_REG[14] = 0xD4; gpBootCfgRegs->DDR3_CONFIG_REG[15] = 0xD0; gpBootCfgRegs->DDR3_CONFIG_REG[16] = 0xBB; gpBootCfgRegs->DDR3_CONFIG_REG[17] = 0xC7; gpBootCfgRegs->DDR3_CONFIG_REG[18] = 0xB1; gpBootCfgRegs->DDR3_CONFIG_REG[19] = 0xB3; gpBootCfgRegs->DDR3_CONFIG_REG[20] = 0xA5; gpBootCfgRegs->DDR3_CONFIG_REG[21] = 0xAD; gpBootCfgRegs->DDR3_CONFIG_REG[22] = 0xC4; 修改完毕后,就可以运行DDR3测试程序。 注意:该工程会测试TMS320C6678,LL1、LL2、OTHER_L1、OTHER_L2、SL2。如果只是测试DDR3,可以修改mem_test_main.c文件中的测试选项定义。 #define LL1_MEM_TEST 0 #define OTHER_L1_TEST 0 #define LL2_MEM_TEST 0 #define OTHER_L2_TEST 0 #define SL2_MEM_TEST 0 #define EXTERNAL_MEM_TEST 1 #define TEST_BY_DSP_CORE 1 #define TEST_BY_DMA 1

程序下载地址:http://download.csdn.net/detail/a137376864/9795887

填写内容有,DDR CLOCK FREQUENCY(时钟频率 1333/2,跑在其它速率只需要修改这个值)。修改DQS,CK中Stripline length (inches)(布线线长)的值。没有DDR ECC就不需要填最后的值。可以得到每个数据通道控制寄存器的值。

修改Memory_Test工程中,KeyStone_DDR_Init.c文件中的C6678_EVM_DDR_Init函数中对应寄存器的值,如下。 //initial vale for leveling /*WRLVL_INIT_RATIO*/ gpBootCfgRegs->DDR3_CONFIG_REG[2] = 0x89; gpBootCfgRegs->DDR3_CONFIG_REG[3] = 0x8D; gpBootCfgRegs->DDR3_CONFIG_REG[4] = 0x87; gpBootCfgRegs->DDR3_CONFIG_REG[5] = 0x7B; gpBootCfgRegs->DDR3_CONFIG_REG[6] = 0x75; gpBootCfgRegs->DDR3_CONFIG_REG[7] = 0x72; gpBootCfgRegs->DDR3_CONFIG_REG[8] = 0x64; gpBootCfgRegs->DDR3_CONFIG_REG[9] = 0x5C; gpBootCfgRegs->DDR3_CONFIG_REG[10] = 0x83;

/*GTLVL_INIT_RATIO*/ gpBootCfgRegs->DDR3_CONFIG_REG[14] = 0xD4; gpBootCfgRegs->DDR3_CONFIG_REG[15] = 0xD0; gpBootCfgRegs->DDR3_CONFIG_REG[16] = 0xBB; gpBootCfgRegs->DDR3_CONFIG_REG[17] = 0xC7; gpBootCfgRegs->DDR3_CONFIG_REG[18] = 0xB1; gpBootCfgRegs->DDR3_CONFIG_REG[19] = 0xB3; gpBootCfgRegs->DDR3_CONFIG_REG[20] = 0xA5; gpBootCfgRegs->DDR3_CONFIG_REG[21] = 0xAD; gpBootCfgRegs->DDR3_CONFIG_REG[22] = 0xC4; 修改完毕后,就可以运行DDR3测试程序。 注意:该工程会测试TMS320C6678,LL1、LL2、OTHER_L1、OTHER_L2、SL2。如果只是测试DDR3,可以修改mem_test_main.c文件中的测试选项定义。 #define LL1_MEM_TEST 0 #define OTHER_L1_TEST 0 #define LL2_MEM_TEST 0 #define OTHER_L2_TEST 0 #define SL2_MEM_TEST 0 #define EXTERNAL_MEM_TEST 1 #define TEST_BY_DSP_CORE 1 #define TEST_BY_DMA 1

程序下载地址:http://download.csdn.net/detail/a137376864/9795887