FPGA+DSP SRIO通信(一)——DSP端参数设置(通道)

经过漫长的探索之后,博主发现关于TI的板子调试和开发要遵循的规律,称其为潜规则也不为过。 1、文档以上就是我的一些学习经验,分享出来,也是对自己以后学习DSP的一个指导思想。 下面开始正题。

文档是程序的基础,是思想和灵魂,所以文档的阅读必须认真,但由于所有的TI文档都是英文,非英语母语者读起来非常不通畅。我说说我的方法:使用谷歌翻译。不是硬着头皮逐句看,看不懂了再翻译,这非常耗费时间,往往看了后面忘了前面。我给出的方法是大段翻译,直接粘贴到谷歌翻译中,在遇到晦涩的部分时再去细看英文,这样效率就会高起来。 2、例程

以SRIO调试为例,我在调试SRIO时的初始目标就是使SRIO两端的设备能互相读写,初期看完SRIO文档后一头雾水,多亏北航学长给了SRIO_Read代码之后我渐渐明白,我们所要调试的大部分工作官方例程都帮我们做了,我们要做的只是明白官方例程做了什么,和我们需要增加哪些东西就够了。例程一般就在你的TI安装目录下的形如PDK6678的文件夹中。如果找不到可以去官方论坛搜索。 3、实践(调试)

程序最终是要在板子上跑起来的,所以在写好程序并不确定程序的功能能不能实现后,最好的办法是在板子上进行在线调试,不要因为怕麻烦而使用SIMLATOR进行仿真,这种软件仿真的意义在于调通算法,而不是调通硬件板卡,所以硬件调试必须上板,不然就是纸上谈兵。

DSP端参数设置

我们所使用的FPGA+DSP是:K7325t+TI6678。FPGA端的情况我不太了解,是我师兄做的,所以我的这个系列的博客只说DSP的配置。使用的官方例程路径:

tipdk_C6678_1_1_2_5packages i ransportipcexamplessrioIpcBenchmarkdevice_srio.c

port mode(port模式)

SRIO通道有自回环(loopback)模式和普通模式(Normal),要使用SRIO实现FPGA和DSP的通信,必须将各port调至Normal模式,即: /* Configure SRIO to operate in loopback mode.(原始例程代码)*/

// CSL_SRIO_SetLoopbackMode(hSrio,0);

// CSL_SRIO_SetLoopbackMode(hSrio,1);

// CSL_SRIO_SetLoopbackMode(hSrio,2);

// CSL_SRIO_SetLoopbackMode(hSrio,3);

/* Configure SRIO to operate in normal mode.(修改后例程代码) */

CSL_SRIO_SetNormalMode(hSrio,0);

CSL_SRIO_SetNormalMode(hSrio,1);

CSL_SRIO_SetNormalMode(hSrio,2);

CSL_SRIO_SetNormalMode(hSrio,3);- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

D: ipdk_C6678_1_1_2_5packages icsldocsdoxygenhtmlcsl__srio_aux_8h.html

查看相关函数定义和功能

链接速率配置(link rate)

/* Assuming the ref_clock of 312.5 MHz and link rate is 3.125Gbps; program the PLL accordingly. */

CSL_BootCfgSetSRIOSERDESConfigPLL (0x229);- 1

- 2

- 3

首先,该函数就是对SRIO_SERDES_CFGPLL寄存器做配置,而该寄存器最重要的,就是上图所示的0-9bit。其中,ENPLL是对PLL(锁相环)的使能,该位必须置0;MPY是选择PLL的倍频倍数,拿图中的8.25x为例,其对SRIO_SERDES_CFGPLL的1-8位写001000 01,高六位是整数部分,001000b是十进制的8,低两位是小数部分,01b是小数0.25;至于VRANGE,写1就行,如果想了解可以自行谷歌。

而0x229的1-8bit为:000101 00b,整数部分是5。那有人就会问了,你说参考时钟是312.5MHz,现在锁相环的倍频5倍,倍频出来的时钟频率不是3.125G啊?

不要着急,最终的link rate不只有锁相环决定,真正起传输作用的是RX和TX,所以对他们的配置也影响link rate,RX和TX的配置我后面会讲到,RX和TX的配置寄存器中有个域叫RATE,就是配置每个锁相环时钟采样几个数据。

TX和RX的RATE域描述如下图所示:

首先,该函数就是对SRIO_SERDES_CFGPLL寄存器做配置,而该寄存器最重要的,就是上图所示的0-9bit。其中,ENPLL是对PLL(锁相环)的使能,该位必须置0;MPY是选择PLL的倍频倍数,拿图中的8.25x为例,其对SRIO_SERDES_CFGPLL的1-8位写001000 01,高六位是整数部分,001000b是十进制的8,低两位是小数部分,01b是小数0.25;至于VRANGE,写1就行,如果想了解可以自行谷歌。

而0x229的1-8bit为:000101 00b,整数部分是5。那有人就会问了,你说参考时钟是312.5MHz,现在锁相环的倍频5倍,倍频出来的时钟频率不是3.125G啊?

不要着急,最终的link rate不只有锁相环决定,真正起传输作用的是RX和TX,所以对他们的配置也影响link rate,RX和TX的配置我后面会讲到,RX和TX的配置寄存器中有个域叫RATE,就是配置每个锁相环时钟采样几个数据。

TX和RX的RATE域描述如下图所示:  然后然后!!我们看一下下面这张表,就明白了:

然后然后!!我们看一下下面这张表,就明白了:

很明显我们在配置RX和TX时将RATE配成了Half,也就是一个PLL时钟采样2个数据,这样数据率不就变成了3.125G吗!

所以,在对link rate进行配置时,需要考虑的只有RX和TX的Rate域和PLL的MPY域。

RX和TX的配置

接下来就到了我们通道配置的重头戏,传输器和接收器的配置,RX负责接收数据,TX负责传输数据,对RX和TX不太了解的可以看我之前的博客。大概了解即可。首先来看一下例程中这部分的写法: /* Configure the SRIO SERDES Receive Configuration. */

/* loopback mode */

// CSL_BootCfgSetSRIOSERDESRxConfig (0, 0x01C40495);

// CSL_BootCfgSetSRIOSERDESRxConfig (1, 0x01C40495);

// CSL_BootCfgSetSRIOSERDESRxConfig (2, 0x01C40495);

// CSL_BootCfgSetSRIOSERDESRxConfig (3, 0x01C40495);

/* Non-loopback */

CSL_BootCfgSetSRIOSERDESRxConfig (0, 0x00440495);

CSL_BootCfgSetSRIOSERDESRxConfig (1, 0x00440495);

CSL_BootCfgSetSRIOSERDESRxConfig (2, 0x00440495);

CSL_BootCfgSetSRIOSERDESRxConfig (3, 0x00440495);

/* Configure the SRIO SERDES Transmit Configuration. */

/* loopback mode */

// CSL_BootCfgSetSRIOSERDESTxConfig (0, 0x00780795);

// CSL_BootCfgSetSRIOSERDESTxConfig (1, 0x00780795);

// CSL_BootCfgSetSRIOSERDESTxConfig (2, 0x00780795);

// CSL_BootCfgSetSRIOSERDESTxConfig (3, 0x00780795);

/* Non-loopback */

CSL_BootCfgSetSRIOSERDESTxConfig (0, 0x00180795);

CSL_BootCfgSetSRIOSERDESTxConfig (1, 0x00180795);

CSL_BootCfgSetSRIOSERDESTxConfig (2, 0x00180795);

CSL_BootCfgSetSRIOSERDESTxConfig (3, 0x00180795);

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

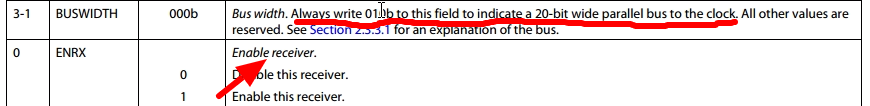

RX配置

对SRIO_SERDES_CFGRX的写入值为0x00440495。我们一步一步讲:先看0-3bit:

最低位是RX使能位,所以不管你要怎样花式配置RX,3-0bit必须是0101b。 第4-5bit的rate域已经在上文说过了。

第6bit是极性转换域,确定高电平使能和低电平使能。没有什么特殊要求置0即可。

第7-9bit只能是001b,想详细了解可以自行查阅相关资料。

第10-11bit是对齐设置域,一般设置为01b即可,需要特殊的对齐设置时可以对该域进行修改。

第12-14bit是丢失信号检测域,一般设置为000b。设置为001b,适用于infiniband通信,设置为100b,适用于PCIE和S-SATA通信。 第15-17bit是时钟/数据恢复算法设置,初级配置中用处不大。设置为000即可。 第18-20bit是均衡器配置,一般设置为001即可。 第21bit是均衡器使能位,默认为使能,即将该位设置为0. 第22bit是漂移补偿使能位,一般要设置为1。 第23-24bit是loopback使能位,设置为00,即关闭loopback模式。不知道大家发现没有,除了rate位,几乎所有的域都是固定配置的,所以大家在配置RX时只需要修改rate位,其余位与0x00440495保持相同即可。

TX配置

对SRIO_SERDES_CFGTX的写入值为0x00180795。我们一步一步讲:0-6bit与RX相同。同样除了rate位,几乎所有的域都是固定配置的,所以大家在配置TX时只需要修改rate位,其余位与0x00180795保持相同即可。 参考文献7-10bit用来设置TX输出电压的振幅。一般设置为1111。 11-18bit用来设置TX输出波形调整的权重,这个我也不太懂,不过一般设置为0000 0000 即可。 19bit用来设置一个FIR滤波器的权重更新使能。该FIR是对TX的波形进行调整的滤波器,该位应该设置为1。 20bit用来设置同步主线。同步时需要一个master,如果要将该位设置为1,就是同步主线,该位设置为0就是同步被动线,单线时该位必须置高,如果为多线,那么必须有一个TX的该位要设置为1。一般设置为1即可。

注意20bit在拓扑结构中的使用,只能有一个TX被设置为1。

http://www.ti.com/cn/litv/pdf/sprugw1b