class="markdown_views prism-dracula">

手册原文:http://www.ti.com/lit/ug/spru871k/spru871k.pdf,翻译参考自谷歌翻译。

中断控制器将系统事件连接到CPU的中断和异常输入。中断控制器最多支持128个系统事件。

有128个系统事件充当中断控制器的输入。它们包括内部生成的事件(在megamodule中)和芯片级事件。事件列表将在后面的7.3节中列举。除了这128个事件外,INTC寄存器还接收不可屏蔽和复位事件,并直接路由到CPU。

中断控制器从这些事件输入向C64x + CPU输出信号:

•一个可屏蔽的硬件异常(EXCEP)

•12个可屏蔽硬件中断(INT4到INT15)

•一个可用作中断或异常(NMI)的不可屏蔽信号

•一个复位信号(RESET)

有关这些CPU中断/异常信号的更多信息,请参阅“TMS320C64x / C64x + DSP CPU和指令集参考指南”(SPRU732)。

中断控制器包括以下模块,以便于将事件路由到中断和异常:

•中断选择器 - 将任何系统事件路由到12个可屏蔽中断

•Event Combiner - 将大量系统事件减少到四个

•异常组合器 - 允许将任何系统事件组合在一起,以用于单个硬件异常输入

系统事件:内部或外部生成的任何信号,旨在通知CPU已发生某些活动和/或需要响应。

中断:由于存在外部或内部硬件信号(事件),提供重定向正常程序流的方法。

异常类似于中断,因为它们还重定向程序流,但异常通常与系统中的错误条件相关联。

有关本章中使用的术语的其他定义,请参阅本文档的附录A和附录B. 附录A描述了本参考指南中使用的一般术语,附录B定义了与内存和缓存架构相关的术语。

此功能使用表7-1中列出的寄存器集实现。 本章提到了这些寄存器。 第7.5节提供了这些寄存器的详细说明。

•事件标志寄存器(EVTFLAGx)

•清除标志寄存器(EVTCLRx)

•设置标志寄存器(EVTSETx)

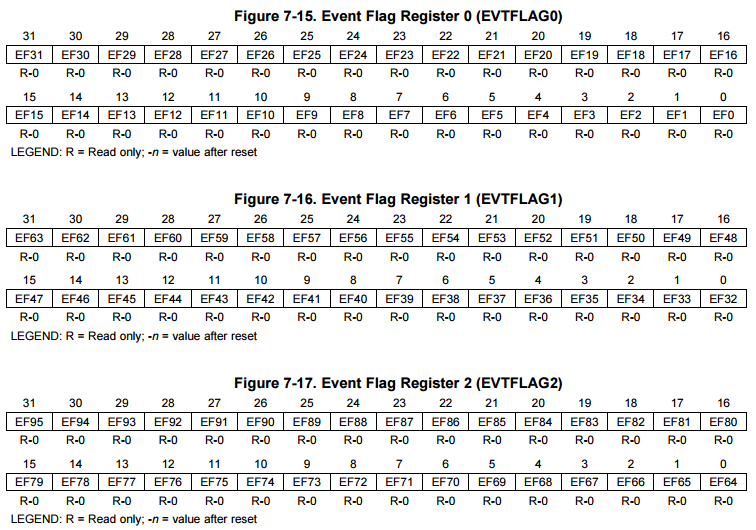

事件标志寄存器捕获中断控制器接收的所有系统事件。 有四个32位寄存器来覆盖124个系统事件输入。 每个系统事件都映射到一个事件标志寄存器中的特定标志位(EFxx)。

通用事件标志寄存器结构如图7-2所示。

所有124个系统事件都单独映射到四个32位EVTFLAGx寄存器中的一个位。 这使得EVTFLAG0(EF03:EF00)的最低有效四位与系统事件无关。 这四个位保留,始终为零。 也就是说,没有与这些字段对应的系统事件输入。 相反,与事件00到03相关联的系统事件由事件组合器在内部(到中断控制器)生成,它们被路由到中断选择器,如图7-1。

事件标志(EFxx)是锁存的寄存器位;也就是说,对于收到的任何事件,它们保留值1。EVTFLAGx寄存器是只读的,必须通过只写事件清除寄存器EVTCLR [3:0]清零。

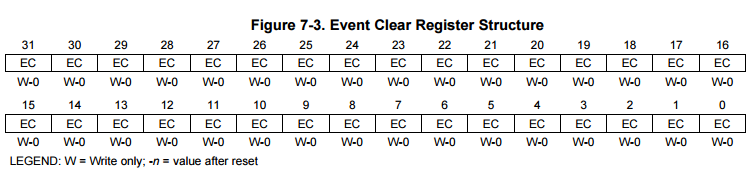

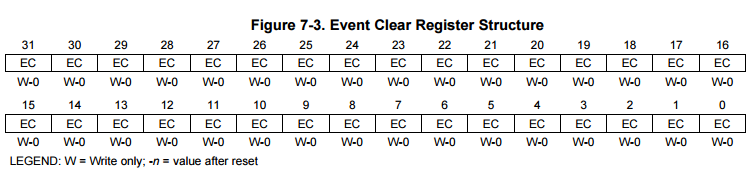

使用事件清除寄存器清除事件标志寄存器。有四个32位事件清除寄存器。这些寄存器的字段与事件标志寄存器的字段一对一映射。将1写入事件清除寄存器中的特定字段会导致相应的事件标志寄存器字段清除。

事件清除寄存器结构如图7-3所示。

事件集寄存器在概念上类似于事件清除寄存器。使用事件集寄存器手动设置事件标志寄存器中的任何位(例如,在测试中断服务例程时使用事件集寄存器来生成中断可能是有益的)。有四个32位事件集寄存器,其字段一对一映射到事件标志寄存器的字段。将1写入事件集寄存器中的特定字段会导致相应的事件标志寄存器设置为1。

事件集寄存器结构如图7-4所示。

中断控制器使用事件清除和事件设置寄存器,而不是直接写入事件标志寄存器以防止潜在的竞争条件。如果没有这些附加寄存器,CPU可能会意外清除在标志位的读 - 修改 - 写操作期间设置的事件标志。

如果在同一周期内收到新事件,则通过EVTCLRx寄存器指定清除,新事件输入优先作为防止丢失事件的附加预防措施。

事件组合器的基本概念是对系统事件标志的子集执行OR运算(如表7-2所示)。 OR运算的结果作为新的“组合”事件提供。

事件组合器将124个系统事件分为四组。 第一组包括事件4到31,第二组包括事件32到63,第三组包括事件64到95,第四组包括事件96到127.您可以组合每个组内的事件以提供新的“组合” “事件。 这些新事件被指定为EVT0,EVT1,EVT2和EVT3。 这些事件与原始的124个系统事件一起路由到中断选择器,总共128个事件。

对于每个组,都有一个事件掩码寄存器。

事件掩码寄存器的一般结构如图7-6所示。

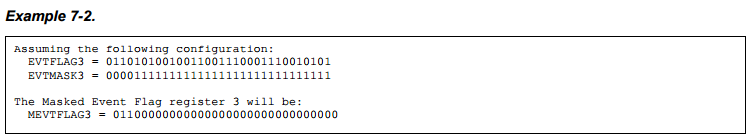

事件掩码寄存器中的事件掩码位用于启用/屏蔽应该组合哪些接收的系统事件。 默认情况下,寄存器为零,因此所有系统事件都被取消屏蔽并组合以形成相关的EVTx。 要屏蔽事件源(例如,禁用组合事件),必须将相应的屏蔽位设置为1.请注意,事件0到3的事件屏蔽位是保留的,并且始终被屏蔽。

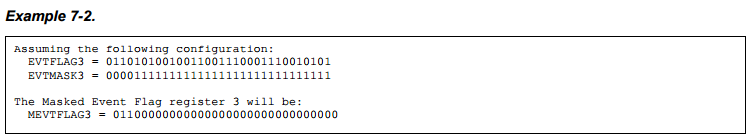

除了基于可编程事件组合生成组合输出事件之外,事件组合器还提供事件标志寄存器的屏蔽视图。

掩码事件标志寄存器的结构如图7-7所示。

屏蔽事件标志寄存器的内容与事件屏蔽寄存器中启用的事件的事件标志寄存器的内容相同。 通过读取屏蔽事件标志寄存器,CPU只能看到与相应组合事件(EVT [3:0])相关的事件标志,这在为组合事件提供服务的中断例程中非常有用。

处理组合中断时,您必须:

1.读取与组合事件EVTx对应的MEVTFLAGx寄存器

2.检查第一个待处理(即标记)事件

3.将此MEVTFLAGx值写入EVTCLRx寄存器

4.服务于步骤2中指示的事件

5.重复步骤1到4,直到MEVTFLAGx寄存器= 0

此过程仅评估和清除EVTx上合并的事件。 此外,EVTMASKx寄存器中屏蔽的任何事件都不会被清除(并且它们不需要清除),即使它们是在EVTFLAGx寄存器中设置的(这允许您使用它们来生成异常)。

注意:CPU应重复步骤1到4,直到在中断服务程序中返回之前没有找到挂起事件。 这可以确保捕获在中断服务程序期间接收到的任何事件(还要记住,如果在EVTCLRy [x]寄存器中清除其标志的同时接收到事件EVTx,则它将不会清除)

128个系统事件是事件组合器生成的事件输入或事件组合。 事件组合器逻辑具有将多个事件输入分组到四个可能的事件输出的能力。 然后将这些输出提供给中断选择器,并将其视为附加系统事件(EVT0至EVT3)。

除中断选择器外,事件组合器还允许灵活的中断路由方案。 INTC模块的这种灵活性允许在兆模块内维护大量系统中断。 它还允许在CPU内同时处理大量中断,从而提高中断效率。

中断选择器包含中断多路复用寄存器INTMUX [3:1],允许您为12个可用CPU中断中的每一个编程源。 呈现给中断选择器的每个事件都有一个事件编号,用于编程这些寄存器。

CPU中断的顺序(CPUINT4到CPUINT15)确定挂起中断的优先级。 由于任何中断服务例程都可以是原子的(不可嵌套),因此CPU中断优先级仅适用于挂起的中断。 有关CPU中断功能的更多信息,请参阅“TMS320C64x / C64x + DSP CPU和指令集参考指南”(SPRU732)。

由于中断丢弃检测逻辑在CPU内,因此只能检测来自单个系统事件的中断。基于组合事件丢弃中断只能指示该组中的一个或多个中断导致错误。

当CPU检测到丢失的错误情况时,它会将信息传递回中断控制器的中断异常状态寄存器(INTXSTAT),该寄存器记录丢弃的中断号并声明系统事件。该寄存器在7.5.3.2节中描述。

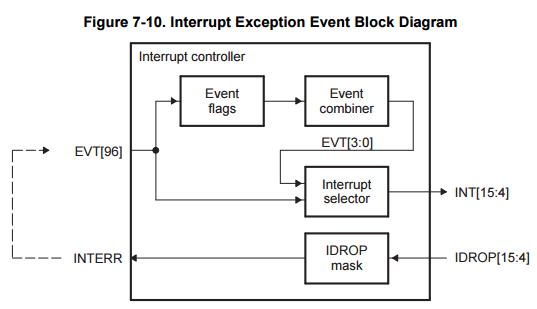

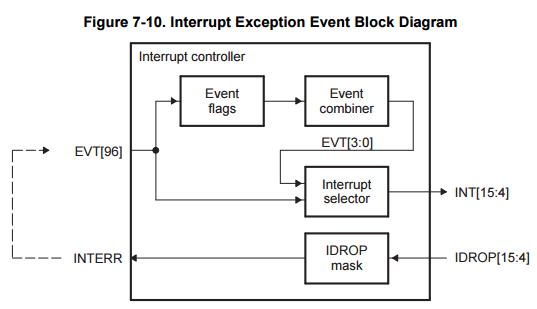

包含与异常生成相关的信号的框图如图7-10所示。

INTERR事件从中断控制器输出,并在内部路由回系统事件EVT96,如图7-10所示。

由于INTXERR只能保存一个丢弃的CPU ID,因此INTERR(EVT96)仅报告检测到的第一个丢弃的中断。 中断异常状态通过异常清除寄存器(INTXCLR)清除,该寄存器仅由一个清零位组成。 将1写入INTXCLR寄存器中的CLEAR字段会将INTXSTAT寄存器复位为0.只有在硬件清除状态后才能检测到新的IDROPx事件。

在处理丢弃的中断错误事件时,服务例程应该:

1.读取INTXSTAT寄存器。

2.检查错误情况。

3.通过INTXCLR寄存器清除错误。

要防止一个或多个CPU中断产生丢弃的中断错误,请通过编程丢弃的中断屏蔽寄存器(INTDMASK)来忽略它们。

异常组合器允许系统设计者选择系统事件标志的子集,在该子集中执行OR操作以确定EXCEP值。

图7-11显示了通过异常组合器路由系统异常的框图。

注意:此图中还显示了Reset和NMI。 实际上,当在C64x + CPU中启用异常时,NMI信号将用作不可屏蔽的异常输入。 这两个信号在CPU中与各种其他CPU异常结合在一起。 有关CPU异常的更多信息,请参阅“TMS320C64x / C64x + DSP CPU和指令集参考指南”(SPRU732)。

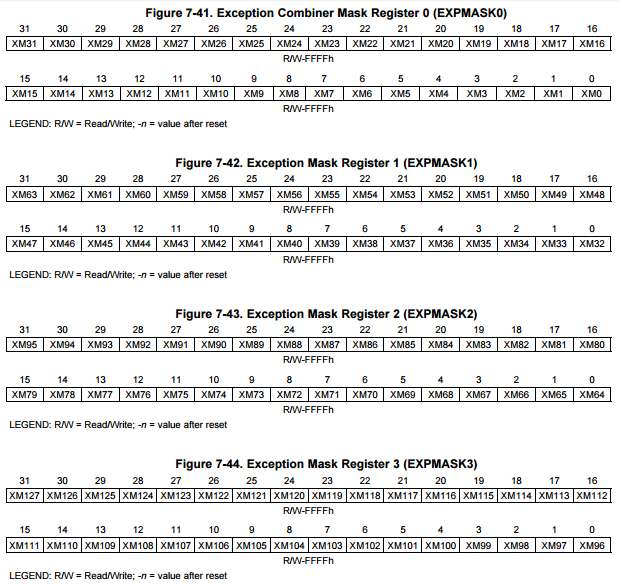

为了只允许系统事件的子集生成CPU异常,异常组合器提供了一组四个掩码寄存器EXPMASK [3:0],用于禁用不需要的事件。 由于CPU只有一个异常输入,因此所有屏蔽寄存器协同工作,最多可将128个事件组合到一个EXCEP输出中。 这允许CPU为所有可用的系统异常提供服务。

异常掩码寄存器的一般结构如图7-12所示:

EXPMASKx寄存器的默认值均为1。 这意味着所有事件都被掩盖了; 因此,除非您对该寄存器进行编程,否则系统事件不会产生异常

与第7.2.2节中讨论的事件组合器类似,异常组合器提供了一组屏蔽异常标志(MEXPFLAGx)以及异常屏蔽寄存器。 屏蔽异常标志寄存器提供事件标志寄存器的屏蔽视图(来自第7.2.1节)。 通过读取屏蔽的异常标志寄存器,唯一的CPU可以看到与CPU的EXCEP输入相关的事件标志。

掩码异常标志寄存器的一般结构如图7-13所示。

CPU应运行异常服务例程以确定异常的原因并在收到异常时响应相应的事件。在处理异常时,服务例程必须首先确定异常是由CPU内部,不可屏蔽异常还是EXCEP信号生成的。

如果发现EXCEP是异常的原因,则例程应读取屏蔽异常标志寄存器(MEXPFLAG [3:0])以确定触发异常的未屏蔽事件。

处理组合中断时,您必须:

1.读取MEXPFLAG [3:0]寄存器。

2.检查要处理的待处理事件。

3.将MEXPFLAG [3:0]值写入EVTCLR [3:0]寄存器。将MEXPFLAGx值与EVTCLRx寄存器一起使用只会清除那些组合在一起以生成EXCEP的事件。即使在EVTFLAGx寄存器中设置,也不需要清除EXPMASKx中屏蔽的任何事件;这允许它们用于生成组合中断事件。

4. CPU应该在步骤1到3之间进行迭代,直到从异常服务例程返回之前没有找到挂起事件。这可确保捕获在异常服务例程期间收到的任何事件。

注意:如果要求CPU响应任何新的异常,则步骤4至关重要。两个事实说明了为什么会这样:

•当任何未屏蔽的事件标志输入处于活动状态时,异常组合器的输出有效。

•CPU将异常请求识别为0到1转换。

因此,在CPU可以识别EXCEP上的新的低到高转换之前,必须清除所有未屏蔽的事件标志。

注意:显示为可用事件(4到8,10和15到95)的事件是针对芯片级事件的megamodule。 因此,每个新的C64x +设备都可以根据需要使用这些事件输入。 有关如何使用这些可用事件的详细信息,请参阅特定于设备的数据手册。

十二个中断信号反映在CPU的中断标志寄存器(IFR)中,如图7-14所示。

必须启用中断才能使CPU识别它们。 CPU需要通过中断使能寄存器(IER)和中断任务寄存器(ITSR.GIE)中的全局中断使能字段进行单独使能。

另请注意,异常信号(EXCEP)记录在图7-15中的CPU异常标志寄存器(EFR)中。必须先启用异常,才能识别显示的异常标志寄存器(EFR)。器件复位后禁用异常识别,以便于系统设计和向后兼容。您可以通过在ITSR寄存器(ITSR)中设置全局异常使能字段(GEE)来打开异常。您应该在启用任何中断之前启用例外以确保当模式(异常与中断)发生变化时,未收到NMI。

当CPU中未启用系统异常时,不可屏蔽中断(NMI)充当中断,并在接收时将标志发送到IFR寄存器中的BIT1字段。在CPU中启用系统异常时;但是,此标志未设置。而是在异常标志寄存器(EFR)中标识异常源,以表示源是NMI,EXCEP,内部异常还是软件异常(SWE / SWENR)。

无论您是将其用作中断还是代表异常,所有NMI处理都会共享NMI中断向量。在SWENR生成异常而不是SWE指令的情况下,CPU仅使用其REP寄存器作为向量而不是NMI向量。

有关更多详细信息,请参阅“TMS320C64x / C64x + DSP CPU和指令集参考指南”(SPRU732)。

但是,在为组合系统事件提供服务时,必须在中断服务例程或异常服务例程中使用事件标志。这些标志用于确定发起中断或异常的事件。换句话说,CPU的中断标志寄存器(或异常标志寄存器)告诉CPU发生了组合事件,然后服务程序必须使用事件标志寄存器来确定确切的原因。

同样重要的是要注意,在服务例程中,必须通过软件清除相应的事件标志寄存器位,以便接收后续事件。如果事件标志未清除,则不会识别新的系统事件。新系统事件甚至不能被识别为丢弃中断。这是因为CPU中断逻辑适用于CPU中断输入(不是中断控制器事件输入)。由于事件在中断控制器中组合在一起,因此CPU在此处没有可见性。

在许多系统中,可能很容易读取服务程序,然后清除整个事件标志寄存器(EVTFLAGx)。虽然这对某些系统可以正常工作,但您必须注意某些事件标志未被任何系统代码轮询。如果必须轮询特定事件(有时通过系统中的某些代码读取而不是允许该事件中断CPU),则不加选择地清除所有事件标志位可能会导致意外结果。

注意:事件标志位0到3保留,并且始终为0.没有与这些字段相对应的事件被路由到事件标志寄存器。

事件集寄存器(EVTSETn)如图7-19至图7-22所示,并在表7-5中进行了描述。

事件清除寄存器(EVTCLRn)如图7-23至图7-26所示,并在表7-6。中进行了描述。

事件掩码寄存器如下所示(位EM [3:0]未使用)。

事件掩码寄存器(EVTMASKn)如图7-27至图7-30所示,并在表7-7中进行了描述。

屏蔽事件标志寄存器(MEVTFLAGn)如图7-31至图7-34所示,并在表7-8中进行了描述。

中断复用寄存器如图7-35至图7-37所示,如表7-9所示。

中断异常状态寄存器(INTXSTAT)如图7-38所示,如表7-10所示。

中断异常清除寄存器如图7-39所示,如表7-11所示。

丢弃的中断屏蔽寄存器(INTDMASK)如图7-40所示,如表7-12所示。

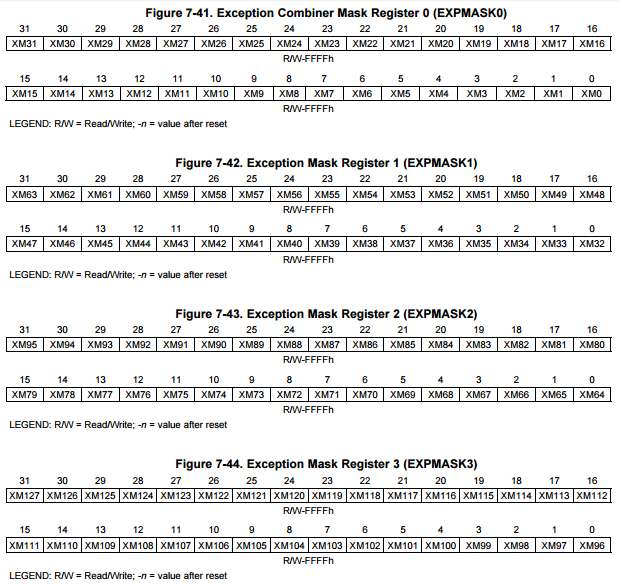

注意:事件0到3的异常掩码是保留的并且始终被屏蔽。

异常组合器掩码寄存器(EXPMASKn)如图7-41至图7-44所示,并在表7-13中进行了描述。

屏蔽异常标志寄存器(MEXPFLAGn)如图7-45至图7-48所示,并在表7-14中进行了描述。

AEGMUX寄存器类似于中断选择器寄存器,因为要传递的事件被简单地编码到选择器位域中。 编码值在可用系统事件(EVT [127:4],组合系统事件(EVT [3:0],CPU中断(CPUINT [15:4],任何中断确认(IACK)和异常确认)之间进行选择( EACK)。组合事件(EVT [3:0]可用并设置为默认事件。

注意:AEGMUX0和AEGMUX1寄存器仅在启用AET的设备上受支持。 请参阅特定于设备的数据表以确定您的设备是否支持AET。

高级事件发生器多路复用器寄存器如图7-49至图7-50所示,并在表7-15中进行了描述。

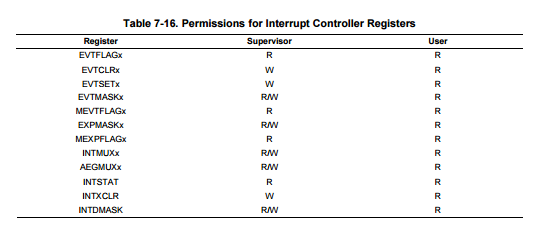

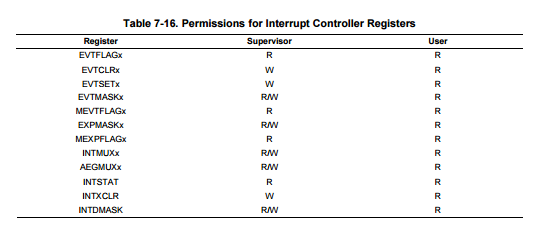

表7-16总结了根据角 {MOD}可访问的中断控制器寄存器。

目录

- 7.1简介

- 7.1.1 C64x + Megamodule中断控制器(INTC)的用途

- 7.1.2特性

- 7.1.3功能框图

- 7.1.4术语和定义

- 7.2中断控制器架构

- 7.2.1事件登记

- 7.2.2事件合并器

- 7.2.3中断选择器

- 7.2.3.1中断选择器操作

- 7.2.3.2中断错误事件

- 7.2.4异常合并器

- 7.3 C64x + Megamodule事件

- 7.4中断控制器 - CPU交互

- 7.4.1 CPU - 中断控制器接口

- 7.4.2中断事件的CPU服务

- 7.5注册

- 7.5.1事件登记

- 7.5.1.1事件标志寄存器(EVTFLAGn)

- 7.5.1.2事件集寄存器(EVTSETn)

- 7.5.1.3事件清除寄存器(EVTCLRn)

- 7.5.2事件合并器寄存器

- 7.5.2.1事件掩码寄存器(EVTMASKn)

- 7.5.2.2屏蔽事件标志寄存器(MEVTFLAGn)

- 7.5.3 CPU中断选择器寄存器

- 7.5.3.1中断复用寄存器(INTMUXn)

- 7.5.3.2中断异常状态寄存器(INTXSTAT)

- 7.5.3.3中断异常清除寄存器(INTXCLR)

- 7.5.3.4丢弃的中断屏蔽寄存器(INTDMASK)

- 7.5.4 CPU异常寄存器

- 7.5.4.1 CPU异常组合器掩码寄存器(EXPMASKn)

- 7.5.4.2屏蔽异常标志寄存器(MEXPFLAGn)

- 7.5.5高级事件发生器复用寄存器(AEGMUXn)

- 7.5.6特权和中断控制器寄存器

- 7.5.1事件登记

7.1简介

本节提供了目的并讨论了中断控制器的功能。7.1.1 C64x + Megamodule中断控制器(INTC)的用途

C64x +系统提供各种各样的系统事件。 中断控制器提供了一种选择必要事件的方法,并将它们路由到适当的CPU中断和异常输入。 虽然您可以使用许多相同的系统事件来驱动其他外围设备,例如EDMA,但兆兆模块的中断控制器专用于管理CPU。7.1.2特性

注意:所有C6000设备均不支持不可屏蔽中断(NMI),有关详细信息,请参阅设备特定的数据手册。中断控制器将系统事件连接到CPU的中断和异常输入。中断控制器最多支持128个系统事件。

有128个系统事件充当中断控制器的输入。它们包括内部生成的事件(在megamodule中)和芯片级事件。事件列表将在后面的7.3节中列举。除了这128个事件外,INTC寄存器还接收不可屏蔽和复位事件,并直接路由到CPU。

中断控制器从这些事件输入向C64x + CPU输出信号:

•一个可屏蔽的硬件异常(EXCEP)

•12个可屏蔽硬件中断(INT4到INT15)

•一个可用作中断或异常(NMI)的不可屏蔽信号

•一个复位信号(RESET)

有关这些CPU中断/异常信号的更多信息,请参阅“TMS320C64x / C64x + DSP CPU和指令集参考指南”(SPRU732)。

中断控制器包括以下模块,以便于将事件路由到中断和异常:

•中断选择器 - 将任何系统事件路由到12个可屏蔽中断

•Event Combiner - 将大量系统事件减少到四个

•异常组合器 - 允许将任何系统事件组合在一起,以用于单个硬件异常输入

7.1.3功能框图

7.1.4术语和定义

本章中特别重要的术语是:系统事件:内部或外部生成的任何信号,旨在通知CPU已发生某些活动和/或需要响应。

中断:由于存在外部或内部硬件信号(事件),提供重定向正常程序流的方法。

异常类似于中断,因为它们还重定向程序流,但异常通常与系统中的错误条件相关联。

有关本章中使用的术语的其他定义,请参阅本文档的附录A和附录B. 附录A描述了本参考指南中使用的一般术语,附录B定义了与内存和缓存架构相关的术语。

7.2中断控制器架构

C64x + megamodule中断控制器旨在提供灵活的系统事件管理。此功能使用表7-1中列出的寄存器集实现。 本章提到了这些寄存器。 第7.5节提供了这些寄存器的详细说明。

7.2.1事件登记

中断控制器包含一组寄存器,用于管理控制器接收的系统事件的状态。 寄存器可以分组如下:•事件标志寄存器(EVTFLAGx)

•清除标志寄存器(EVTCLRx)

•设置标志寄存器(EVTSETx)

事件标志寄存器捕获中断控制器接收的所有系统事件。 有四个32位寄存器来覆盖124个系统事件输入。 每个系统事件都映射到一个事件标志寄存器中的特定标志位(EFxx)。

通用事件标志寄存器结构如图7-2所示。

所有124个系统事件都单独映射到四个32位EVTFLAGx寄存器中的一个位。 这使得EVTFLAG0(EF03:EF00)的最低有效四位与系统事件无关。 这四个位保留,始终为零。 也就是说,没有与这些字段对应的系统事件输入。 相反,与事件00到03相关联的系统事件由事件组合器在内部(到中断控制器)生成,它们被路由到中断选择器,如图7-1。

事件标志(EFxx)是锁存的寄存器位;也就是说,对于收到的任何事件,它们保留值1。EVTFLAGx寄存器是只读的,必须通过只写事件清除寄存器EVTCLR [3:0]清零。

使用事件清除寄存器清除事件标志寄存器。有四个32位事件清除寄存器。这些寄存器的字段与事件标志寄存器的字段一对一映射。将1写入事件清除寄存器中的特定字段会导致相应的事件标志寄存器字段清除。

事件清除寄存器结构如图7-3所示。

事件集寄存器在概念上类似于事件清除寄存器。使用事件集寄存器手动设置事件标志寄存器中的任何位(例如,在测试中断服务例程时使用事件集寄存器来生成中断可能是有益的)。有四个32位事件集寄存器,其字段一对一映射到事件标志寄存器的字段。将1写入事件集寄存器中的特定字段会导致相应的事件标志寄存器设置为1。

事件集寄存器结构如图7-4所示。

中断控制器使用事件清除和事件设置寄存器,而不是直接写入事件标志寄存器以防止潜在的竞争条件。如果没有这些附加寄存器,CPU可能会意外清除在标志位的读 - 修改 - 写操作期间设置的事件标志。

如果在同一周期内收到新事件,则通过EVTCLRx寄存器指定清除,新事件输入优先作为防止丢失事件的附加预防措施。

7.2.2事件合并器

事件组合器(图7-5)允许将多个系统事件组合到一个事件中。 组合事件被路由到中断选择器。 这允许CPU为所有可用的系统事件提供服务,即使CPU只有12个可用中断。

事件组合器的基本概念是对系统事件标志的子集执行OR运算(如表7-2所示)。 OR运算的结果作为新的“组合”事件提供。

事件组合器将124个系统事件分为四组。 第一组包括事件4到31,第二组包括事件32到63,第三组包括事件64到95,第四组包括事件96到127.您可以组合每个组内的事件以提供新的“组合” “事件。 这些新事件被指定为EVT0,EVT1,EVT2和EVT3。 这些事件与原始的124个系统事件一起路由到中断选择器,总共128个事件。

对于每个组,都有一个事件掩码寄存器。

事件掩码寄存器的一般结构如图7-6所示。

事件掩码寄存器中的事件掩码位用于启用/屏蔽应该组合哪些接收的系统事件。 默认情况下,寄存器为零,因此所有系统事件都被取消屏蔽并组合以形成相关的EVTx。 要屏蔽事件源(例如,禁用组合事件),必须将相应的屏蔽位设置为1.请注意,事件0到3的事件屏蔽位是保留的,并且始终被屏蔽。

除了基于可编程事件组合生成组合输出事件之外,事件组合器还提供事件标志寄存器的屏蔽视图。

掩码事件标志寄存器的结构如图7-7所示。

屏蔽事件标志寄存器的内容与事件屏蔽寄存器中启用的事件的事件标志寄存器的内容相同。 通过读取屏蔽事件标志寄存器,CPU只能看到与相应组合事件(EVT [3:0])相关的事件标志,这在为组合事件提供服务的中断例程中非常有用。

处理组合中断时,您必须:

1.读取与组合事件EVTx对应的MEVTFLAGx寄存器

2.检查第一个待处理(即标记)事件

3.将此MEVTFLAGx值写入EVTCLRx寄存器

4.服务于步骤2中指示的事件

5.重复步骤1到4,直到MEVTFLAGx寄存器= 0

此过程仅评估和清除EVTx上合并的事件。 此外,EVTMASKx寄存器中屏蔽的任何事件都不会被清除(并且它们不需要清除),即使它们是在EVTFLAGx寄存器中设置的(这允许您使用它们来生成异常)。

注意:CPU应重复步骤1到4,直到在中断服务程序中返回之前没有找到挂起事件。 这可以确保捕获在中断服务程序期间接收到的任何事件(还要记住,如果在EVTCLRy [x]寄存器中清除其标志的同时接收到事件EVTx,则它将不会清除)

7.2.3中断选择器

7.2.3.1中断选择器操作

CPU有12个可屏蔽中断(CPUINT4到15)可用。 中断选择器允许128个系统事件中的任何一个路由到12个CPU中断输入中的任何一个,如图7-8所示。

128个系统事件是事件组合器生成的事件输入或事件组合。 事件组合器逻辑具有将多个事件输入分组到四个可能的事件输出的能力。 然后将这些输出提供给中断选择器,并将其视为附加系统事件(EVT0至EVT3)。

除中断选择器外,事件组合器还允许灵活的中断路由方案。 INTC模块的这种灵活性允许在兆模块内维护大量系统中断。 它还允许在CPU内同时处理大量中断,从而提高中断效率。

中断选择器包含中断多路复用寄存器INTMUX [3:1],允许您为12个可用CPU中断中的每一个编程源。 呈现给中断选择器的每个事件都有一个事件编号,用于编程这些寄存器。

CPU中断的顺序(CPUINT4到CPUINT15)确定挂起中断的优先级。 由于任何中断服务例程都可以是原子的(不可嵌套),因此CPU中断优先级仅适用于挂起的中断。 有关CPU中断功能的更多信息,请参阅“TMS320C64x / C64x + DSP CPU和指令集参考指南”(SPRU732)。

7.2.3.2中断错误事件

只要CPU检测到中断被丢弃,C64x + CPU和中断控制器就会产生系统事件(EVT96)。当接收到CPU中断且相关CPU的中断标志位已设置时,将生成此事件。此错误事件可能表示程序员可能在代码中出现问题,例如中断是否在较长时间内被禁用,或者不可中断的代码段是否过长。由于中断丢弃检测逻辑在CPU内,因此只能检测来自单个系统事件的中断。基于组合事件丢弃中断只能指示该组中的一个或多个中断导致错误。

当CPU检测到丢失的错误情况时,它会将信息传递回中断控制器的中断异常状态寄存器(INTXSTAT),该寄存器记录丢弃的中断号并声明系统事件。该寄存器在7.5.3.2节中描述。

包含与异常生成相关的信号的框图如图7-10所示。

INTERR事件从中断控制器输出,并在内部路由回系统事件EVT96,如图7-10所示。

由于INTXERR只能保存一个丢弃的CPU ID,因此INTERR(EVT96)仅报告检测到的第一个丢弃的中断。 中断异常状态通过异常清除寄存器(INTXCLR)清除,该寄存器仅由一个清零位组成。 将1写入INTXCLR寄存器中的CLEAR字段会将INTXSTAT寄存器复位为0.只有在硬件清除状态后才能检测到新的IDROPx事件。

在处理丢弃的中断错误事件时,服务例程应该:

1.读取INTXSTAT寄存器。

2.检查错误情况。

3.通过INTXCLR寄存器清除错误。

要防止一个或多个CPU中断产生丢弃的中断错误,请通过编程丢弃的中断屏蔽寄存器(INTDMASK)来忽略它们。

7.2.4异常合并器

C64x + CPU具有单个事件输入,用于系统级可屏蔽异常。 该输入由EXCEP表示。 异常组合器允许将多个系统事件组合到图7-12中的单个异常事件中。 这允许CPU为所有可用的系统事件提供服务,即使只有一个CPU异常输入可用。异常组合器允许系统设计者选择系统事件标志的子集,在该子集中执行OR操作以确定EXCEP值。

图7-11显示了通过异常组合器路由系统异常的框图。

注意:此图中还显示了Reset和NMI。 实际上,当在C64x + CPU中启用异常时,NMI信号将用作不可屏蔽的异常输入。 这两个信号在CPU中与各种其他CPU异常结合在一起。 有关CPU异常的更多信息,请参阅“TMS320C64x / C64x + DSP CPU和指令集参考指南”(SPRU732)。

为了只允许系统事件的子集生成CPU异常,异常组合器提供了一组四个掩码寄存器EXPMASK [3:0],用于禁用不需要的事件。 由于CPU只有一个异常输入,因此所有屏蔽寄存器协同工作,最多可将128个事件组合到一个EXCEP输出中。 这允许CPU为所有可用的系统异常提供服务。

异常掩码寄存器的一般结构如图7-12所示:

EXPMASKx寄存器的默认值均为1。 这意味着所有事件都被掩盖了; 因此,除非您对该寄存器进行编程,否则系统事件不会产生异常

与第7.2.2节中讨论的事件组合器类似,异常组合器提供了一组屏蔽异常标志(MEXPFLAGx)以及异常屏蔽寄存器。 屏蔽异常标志寄存器提供事件标志寄存器的屏蔽视图(来自第7.2.1节)。 通过读取屏蔽的异常标志寄存器,唯一的CPU可以看到与CPU的EXCEP输入相关的事件标志。

掩码异常标志寄存器的一般结构如图7-13所示。

CPU应运行异常服务例程以确定异常的原因并在收到异常时响应相应的事件。在处理异常时,服务例程必须首先确定异常是由CPU内部,不可屏蔽异常还是EXCEP信号生成的。

如果发现EXCEP是异常的原因,则例程应读取屏蔽异常标志寄存器(MEXPFLAG [3:0])以确定触发异常的未屏蔽事件。

处理组合中断时,您必须:

1.读取MEXPFLAG [3:0]寄存器。

2.检查要处理的待处理事件。

3.将MEXPFLAG [3:0]值写入EVTCLR [3:0]寄存器。将MEXPFLAGx值与EVTCLRx寄存器一起使用只会清除那些组合在一起以生成EXCEP的事件。即使在EVTFLAGx寄存器中设置,也不需要清除EXPMASKx中屏蔽的任何事件;这允许它们用于生成组合中断事件。

4. CPU应该在步骤1到3之间进行迭代,直到从异常服务例程返回之前没有找到挂起事件。这可确保捕获在异常服务例程期间收到的任何事件。

注意:如果要求CPU响应任何新的异常,则步骤4至关重要。两个事实说明了为什么会这样:

•当任何未屏蔽的事件标志输入处于活动状态时,异常组合器的输出有效。

•CPU将异常请求识别为0到1转换。

因此,在CPU可以识别EXCEP上的新的低到高转换之前,必须清除所有未屏蔽的事件标志。

7.3 C64x + Megamodule事件

C64x + megamodule的各个组件生成了许多事件。 这些事件被路由到中断控制器,以便在断言时,它们可以由CPU提供服务。表7-2列出了这些事件及其事件映射。注意:显示为可用事件(4到8,10和15到95)的事件是针对芯片级事件的megamodule。 因此,每个新的C64x +设备都可以根据需要使用这些事件输入。 有关如何使用这些可用事件的详细信息,请参阅特定于设备的数据手册。

7.4中断控制器 - CPU交互

7.4.1 CPU - 中断控制器接口

由异常组合器和中断选择器产生的中断控制器输出提供给C64x + CPU。十二个中断信号反映在CPU的中断标志寄存器(IFR)中,如图7-14所示。

必须启用中断才能使CPU识别它们。 CPU需要通过中断使能寄存器(IER)和中断任务寄存器(ITSR.GIE)中的全局中断使能字段进行单独使能。

另请注意,异常信号(EXCEP)记录在图7-15中的CPU异常标志寄存器(EFR)中。必须先启用异常,才能识别显示的异常标志寄存器(EFR)。器件复位后禁用异常识别,以便于系统设计和向后兼容。您可以通过在ITSR寄存器(ITSR)中设置全局异常使能字段(GEE)来打开异常。您应该在启用任何中断之前启用例外以确保当模式(异常与中断)发生变化时,未收到NMI。

当CPU中未启用系统异常时,不可屏蔽中断(NMI)充当中断,并在接收时将标志发送到IFR寄存器中的BIT1字段。在CPU中启用系统异常时;但是,此标志未设置。而是在异常标志寄存器(EFR)中标识异常源,以表示源是NMI,EXCEP,内部异常还是软件异常(SWE / SWENR)。

无论您是将其用作中断还是代表异常,所有NMI处理都会共享NMI中断向量。在SWENR生成异常而不是SWE指令的情况下,CPU仅使用其REP寄存器作为向量而不是NMI向量。

有关更多详细信息,请参阅“TMS320C64x / C64x + DSP CPU和指令集参考指南”(SPRU732)。

7.4.2中断事件的CPU服务

对于CPU服务单事件中断(其中系统事件直接在中断选择器中指定)的情况,不需要读取或清除中断控制器中的事件标志(EVTFLAGx)寄存器。但是,在为组合系统事件提供服务时,必须在中断服务例程或异常服务例程中使用事件标志。这些标志用于确定发起中断或异常的事件。换句话说,CPU的中断标志寄存器(或异常标志寄存器)告诉CPU发生了组合事件,然后服务程序必须使用事件标志寄存器来确定确切的原因。

同样重要的是要注意,在服务例程中,必须通过软件清除相应的事件标志寄存器位,以便接收后续事件。如果事件标志未清除,则不会识别新的系统事件。新系统事件甚至不能被识别为丢弃中断。这是因为CPU中断逻辑适用于CPU中断输入(不是中断控制器事件输入)。由于事件在中断控制器中组合在一起,因此CPU在此处没有可见性。

在许多系统中,可能很容易读取服务程序,然后清除整个事件标志寄存器(EVTFLAGx)。虽然这对某些系统可以正常工作,但您必须注意某些事件标志未被任何系统代码轮询。如果必须轮询特定事件(有时通过系统中的某些代码读取而不是允许该事件中断CPU),则不加选择地清除所有事件标志位可能会导致意外结果。

7.5注册

表7-3列出了C64x + megamodule中断控制器寄存器

7.5.1事件登记

中断控制器包含一组状态和控制寄存器,用于管理控制器接收的系统事件。 这些包括标志,设置和清除寄存器,涵盖所有128个系统事件。注意:事件标志位0到3保留,并且始终为0.没有与这些字段相对应的事件被路由到事件标志寄存器。

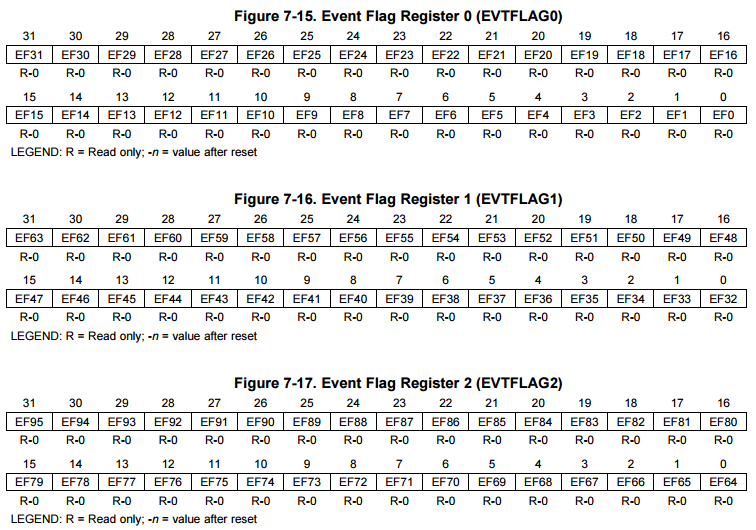

7.5.1.1事件标志寄存器(EVTFLAGn)

事件标志寄存器(EVTFLAGn)中的事件标志对于接收的128个系统事件中的任何一个保留值1,并且是只读寄存器。 使用只写事件清除寄存器(EVTCLRn)清除寄存器。 使用事件集寄存器(EVTSETn)手动设置EVTFLAGn中的任何位,包括屏蔽位。 事件标志寄存器(EVTFLAGn)如图7-15至图7-18所示,并在表7-4中进行了描述。

7.5.1.2事件集寄存器(EVTSETn)

使用事件设置寄存器(EVTSETn)手动设置事件标志寄存器(EVTSETn)中的任何位。事件集寄存器(EVTSETn)如图7-19至图7-22所示,并在表7-5中进行了描述。

7.5.1.3事件清除寄存器(EVTCLRn)

使用事件清除寄存器(EVTCLRn)清除事件标志寄存器(EVTCLRn)中的事件标志。事件清除寄存器(EVTCLRn)如图7-23至图7-26所示,并在表7-6。中进行了描述。

7.5.2事件合并器寄存器

有一组事件掩码寄存器(EVTMASK [3:0])用于对事件组合器进行编程。 这些寄存器允许将最多32个事件组合成单个组合事件,然后中断选择器可以使用这些事件。 EVTMASK [3:0]寄存器中的事件掩码位用于屏蔽(或启用)接收到的系统事件。 有四个事件信号提供给中断选择器(EVT [3:0])。事件掩码寄存器如下所示(位EM [3:0]未使用)。

7.5.2.1事件掩码寄存器(EVTMASKn)

有一组事件掩码寄存器(EVTMASK0到EVTMASK3)用于对事件组合器进行编程。 这些寄存器允许将最多32个事件组合成单个事件输出,用作单个CPU中断或AET事件。 EVTMASKn寄存器中的事件掩码位充当接收系统事件的启用器,以便在事件输出上进行组合。 事件和AET事件选择器有四个事件输出(EVT [3:0])。事件掩码寄存器(EVTMASKn)如图7-27至图7-30所示,并在表7-7中进行了描述。

7.5.2.2屏蔽事件标志寄存器(MEVTFLAGn)

事件组合器提供一组四个屏蔽事件标志寄存器(事件标志寄存器的屏蔽视图)。屏蔽事件标志寄存器(MEVTFLAGn)如图7-31至图7-34所示,并在表7-8中进行了描述。

7.5.3 CPU中断选择器寄存器

7.5.3.1中断复用寄存器(INTMUXn)

中断选择器包含中断复用寄存器,允许您为12个可用CPU中断中的每一个编程源。中断复用寄存器如图7-35至图7-37所示,如表7-9所示。

7.5.3.2中断异常状态寄存器(INTXSTAT)

中断异常状态寄存器(INTXSTAT)提供信息以确定导致生成的异常的原因。 INTXSTAT寄存器保存CPU中断和丢弃事件的系统事件编号。中断异常状态寄存器(INTXSTAT)如图7-38所示,如表7-10所示。

7.5.3.3中断异常清除寄存器(INTXCLR)

中断异常状态通过异常清除寄存器清除,该寄存器基本上是一个清除位,如下所示。 只有在状态清除后,硬件才能检测到新的IDROPx事件。中断异常清除寄存器如图7-39所示,如表7-11所示。

7.5.3.4丢弃的中断屏蔽寄存器(INTDMASK)

生成INTERR事件的丢弃中断可以通过掩码寄存器进行过滤。 丢弃检测硬件要忽略的那些CPU中断可以在丢弃的中断屏蔽寄存器(INTDMASK)中屏蔽掉。丢弃的中断屏蔽寄存器(INTDMASK)如图7-40所示,如表7-12所示。

7.5.4 CPU异常寄存器

7.5.4.1 CPU异常组合器掩码寄存器(EXPMASKn)

与事件组合器一样,异常组合器具有掩码寄存器,用于控制触发EXCEP的事件。注意:事件0到3的异常掩码是保留的并且始终被屏蔽。

异常组合器掩码寄存器(EXPMASKn)如图7-41至图7-44所示,并在表7-13中进行了描述。

7.5.4.2屏蔽异常标志寄存器(MEXPFLAGn)

异常组合器提供一组四个屏蔽异常标志寄存器(异常标志寄存器的屏蔽视图)。屏蔽异常标志寄存器(MEXPFLAGn)如图7-45至图7-48所示,并在表7-14中进行了描述。

7.5.5高级事件发生器复用寄存器(AEGMUXn)

高级事件生成器(AEG)允许任何事件充当仿真触发器。 发送到AEG块的事件在AEG复用寄存器(AEGMUX0和AEGMUX1)中配置。AEGMUX寄存器类似于中断选择器寄存器,因为要传递的事件被简单地编码到选择器位域中。 编码值在可用系统事件(EVT [127:4],组合系统事件(EVT [3:0],CPU中断(CPUINT [15:4],任何中断确认(IACK)和异常确认)之间进行选择( EACK)。组合事件(EVT [3:0]可用并设置为默认事件。

注意:AEGMUX0和AEGMUX1寄存器仅在启用AET的设备上受支持。 请参阅特定于设备的数据表以确定您的设备是否支持AET。

高级事件发生器多路复用器寄存器如图7-49至图7-50所示,并在表7-15中进行了描述。

7.5.6特权和中断控制器寄存器

C64x +架构提供内存保护支持。表7-16总结了根据角 {MOD}可访问的中断控制器寄存器。