PAE分页模式可以将32位的线性地址空间映射到52位的物理地址空间。相比于32位分页方式,其物理地址空间增加到了4PB。但对于在处理器上运行的任一进程而言,其最大的线性地址空间仍然是4GB。

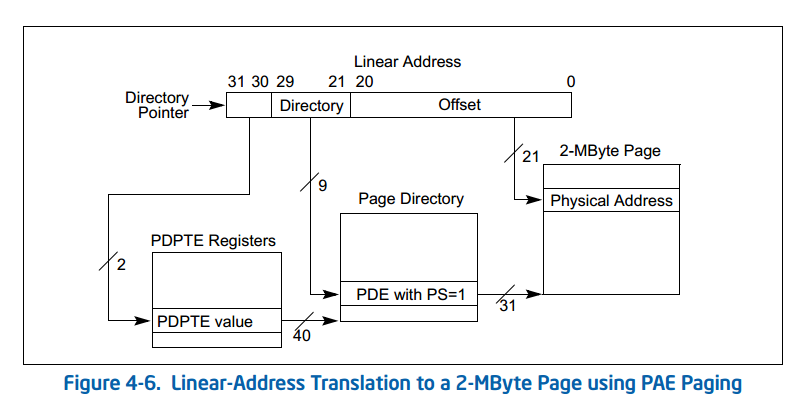

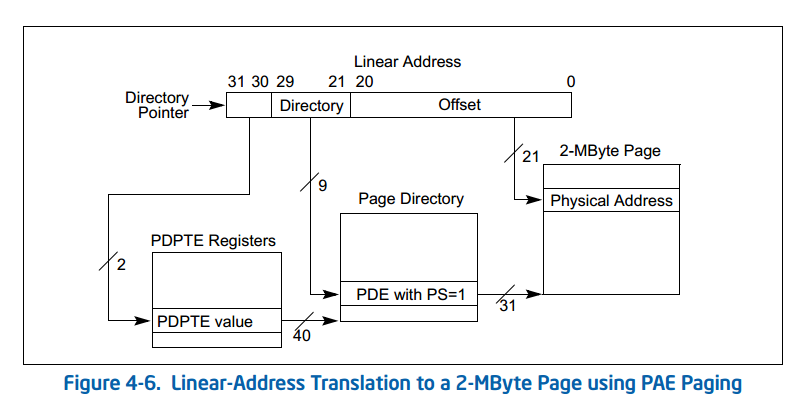

对于2MB的页面,其线性地址转换方式如下:

对于2MB的页面,其线性地址转换方式如下:

那么它是如何把地址扩展到52位的呢?注意PDPT的表项长度,它有40个bit,再住下的每一级目录都有40个bit,最后加上offset的12个bit, 一共刚好组成了52个bit。但是其线性地址的长度任然是32个bit。所以线性地址空间的大小不变。

那么现在问题来了?线性地址空间只有4GB,一定不能做到对4PB的物理空间的1:1映射。难道要1对多映射么?怎么映射呢?

刚开始这个问题让我困惑了很久,线性空间只有4GB,如果不是1对多映射,就算是物理地址有52 bits。也只能用于其中的4GB啊,剩下的只能白白浪费掉!!!

网上苦苦搜索,没有找到答案,只好再细读IA32 spec。当看到以下几句话的时候才明白过来:

什么意思呢?

第一句话是讲,PDPT的物理地址被存放在CR3中。也就是说改变CR3, PDPTE也会跟着变。

第二句话最关键,如果PAE分页被使用,而进程在运行的过程中改变了CR3的值,PDPTE将会指向CR3所保存的新地址。

这就意味着,我们在内存中不只保存了一套页表,而是保存了多套,进程跟据需要,改变CR3的值,从而实现对当前4GB物理地址之外的访问。这也就说明了一对多是如何实现的。

页面大小

PAE分页主要支持两种页面大小:- 4KB页面

- 2MB页面

对于2MB的页面,其线性地址转换方式如下:

对于2MB的页面,其线性地址转换方式如下:

如何映射(4GB->4PB)

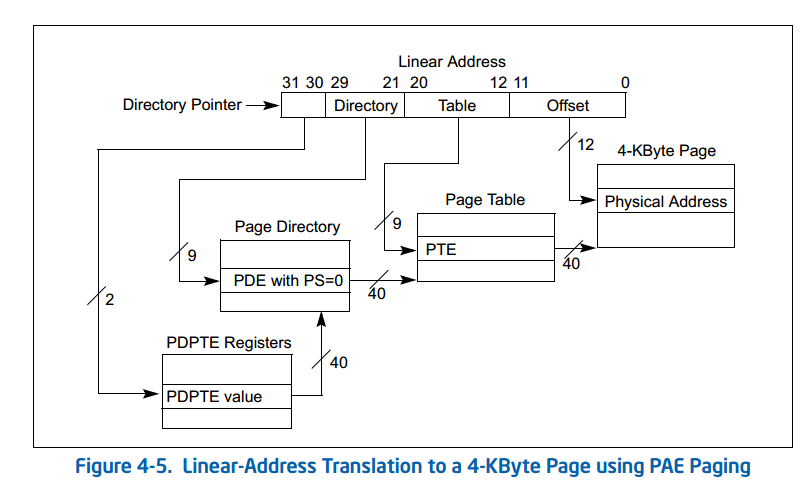

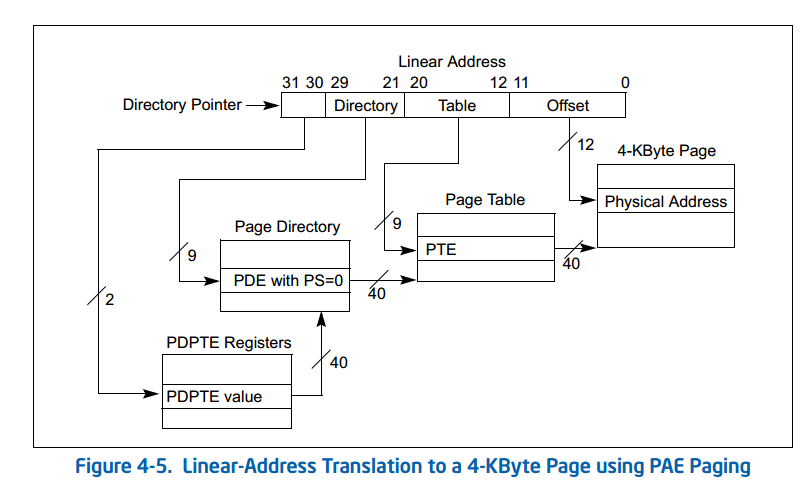

相比于32位分页方式,PAE的4KB分页要多一级分页,由上图可以看出,多出了PDPT。即Page-Directory-Page-Table。这个Table只有4个入口,因为它只占了两个bit。那么它是如何把地址扩展到52位的呢?注意PDPT的表项长度,它有40个bit,再住下的每一级目录都有40个bit,最后加上offset的12个bit, 一共刚好组成了52个bit。但是其线性地址的长度任然是32个bit。所以线性地址空间的大小不变。

那么现在问题来了?线性地址空间只有4GB,一定不能做到对4PB的物理空间的1:1映射。难道要1对多映射么?怎么映射呢?

刚开始这个问题让我困惑了很久,线性空间只有4GB,如果不是1对多映射,就算是物理地址有52 bits。也只能用于其中的4GB啊,剩下的只能白白浪费掉!!!

网上苦苦搜索,没有找到答案,只好再细读IA32 spec。当看到以下几句话的时候才明白过来:

什么意思呢?

第一句话是讲,PDPT的物理地址被存放在CR3中。也就是说改变CR3, PDPTE也会跟着变。

第二句话最关键,如果PAE分页被使用,而进程在运行的过程中改变了CR3的值,PDPTE将会指向CR3所保存的新地址。

这就意味着,我们在内存中不只保存了一套页表,而是保存了多套,进程跟据需要,改变CR3的值,从而实现对当前4GB物理地址之外的访问。这也就说明了一对多是如何实现的。