对于任何一种CPU来说,除了正常的执行指令外,中断(或异常)是唯一的异步事件。中断的出现是随机的,对中断的处理能力也是CPU的一个重要指标,特别是对于嵌入式处理器。TMS320F28335内置的是C28x系列的CPU。下面介绍C28x对中断的处理过程。

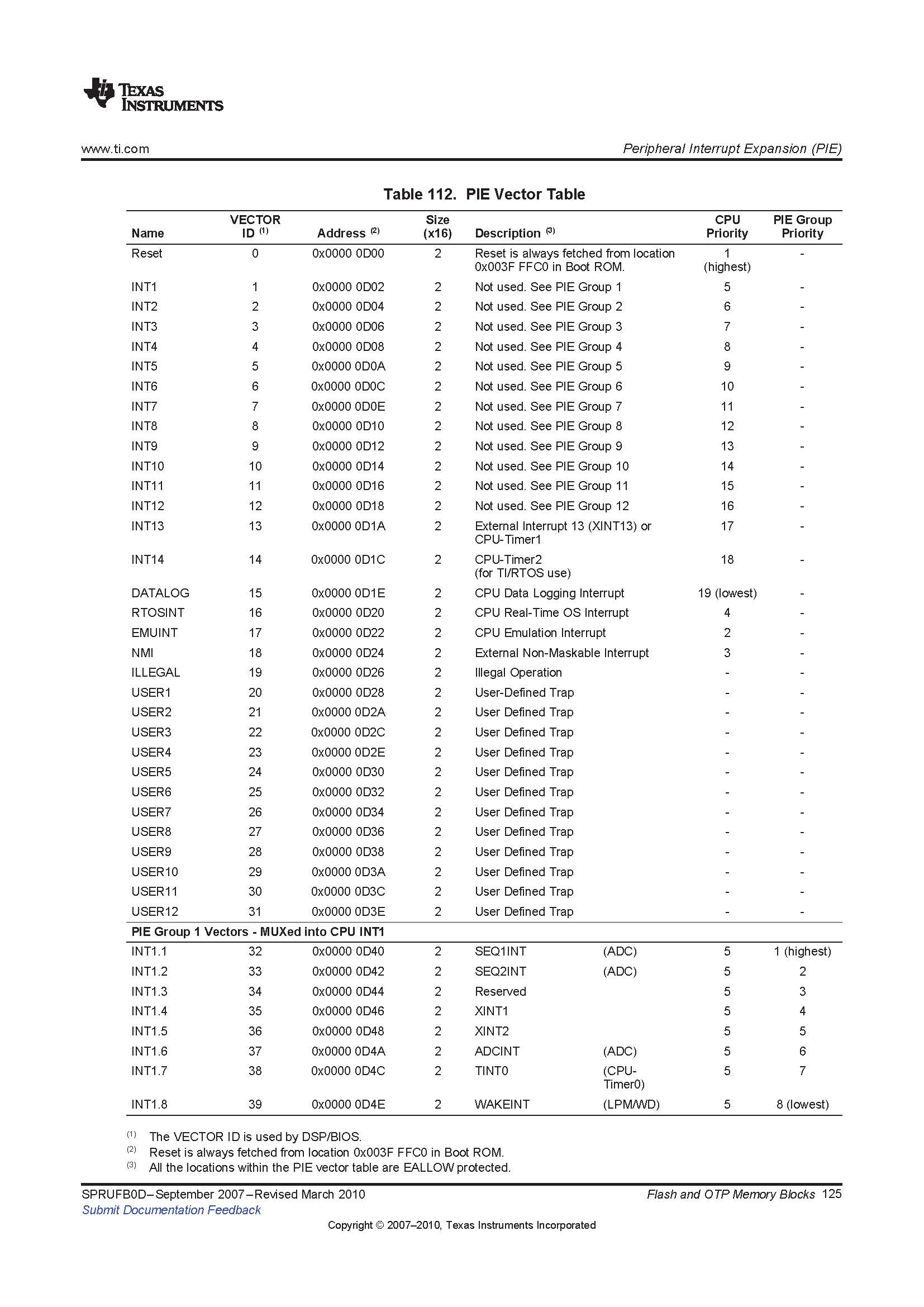

图1

PIE表的构造如下:

图1

PIE表的构造如下:

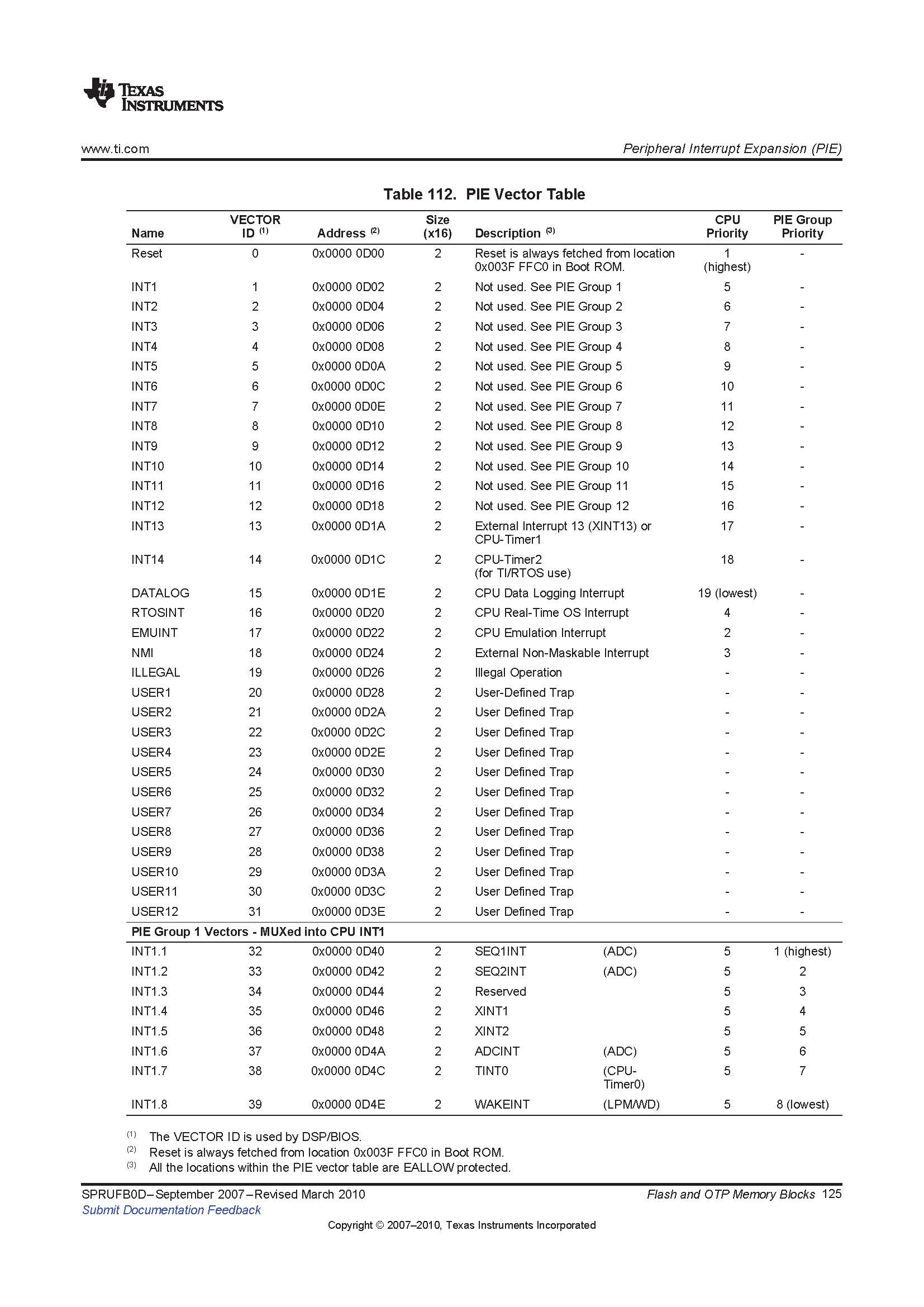

图2

从图中可得:

1.CPU级中断的优先级Reset优先级最高,但是系统复位时复位向量总是从0x3fffc0取。

2.CPU可屏蔽中断优先级顺序(从高到低):RTOSINT,INT1-INT14,DLOGINT。

3.INT1-INT12接PIE模块拓展了中断系统,INTx.1-INTx.8中断优先级依次降低。

图2

从图中可得:

1.CPU级中断的优先级Reset优先级最高,但是系统复位时复位向量总是从0x3fffc0取。

2.CPU可屏蔽中断优先级顺序(从高到低):RTOSINT,INT1-INT14,DLOGINT。

3.INT1-INT12接PIE模块拓展了中断系统,INTx.1-INTx.8中断优先级依次降低。

图3 相应的位置位表示中断申请。寄存器的位格式同IER和DBGIER。 注意这个寄存器可以用软件置位实现软件中断,如OR IFR,#1,将会置位INT1用软件模拟中断的请求。 对于F28335其INT1-INT12外接了PIE模块,中断对INT1的处理会牵扯到PIE模块中的部分寄存器。这些将会在后续内容中详细的讲。INT13,INT14外接了CPU timer0,如下图所示:

图4 CPU对可屏蔽中断的的响应过程如下: 1)中断申请。 PIE模块通过将INT1-INT12中置位; 仿真逻辑通过置位RTOSINT或DLOGINT; 通过执行指令OR IFR,#x将IFR中某一位置位。 2)中断允许。 中断申请后,只有得到允许才能受到CPU的处理。中断允许条件见表1. 3) 中断的判优。 当同时有多个中断申请时,优先级高的讲得到响应。中断的优先级见2 4)清除IFR中相应位。 一旦中断得到相应,IFR中的相应位就会被清除。在得到响应到进入中断服务子程序之前,所有的中断都会被屏蔽。 5)清除流水线。 6)保存PC值。 保存PC的值(中断返回后要执行的指令地址)到一个内部寄存器。在自动上下午切换时,该值会被压入堆栈。 7)获得中断向量。 CPU根据中断源获得相应的中断向量。由于F28335有PIE模块,一般情况下其中断向量表将定位到PIE Vector,PIE Vector的结构见图2 8)执行自动上下文切换。 上下文切换就是断点的保存。自动保存的CPU寄存器和顺序如下图: 1stST0,T 2nd AL,AH 3rd PL,PH 4st AR0,AR1 5st ST1,DP 6st IER,DBGSTAT 7st Return address 9)清除IER中的相应位。 这样使正在服务的中断源被屏蔽。当然如果想使能中断嵌套的话可以从新将其置位。 10)置位INTM,DBGM,清除LOOP,EALLOW,IDLESTAT位。 置位INTM禁止所有可屏蔽中断。 11)将在第7)中得到的中断向量加载到PC,开始执行中断服务程序。 12)中断的返回。C28x系列CPU中断的返回通过IRET指令。 C28x系列CPU中IRET指令完成的断点的恢复,执行IRET指令CPU会按照进入中断时入栈的相反顺序将相应寄存器弹出堆栈。 对于使用中断来说,写程序最需要注意的是中断的断点保护和中断标志的清除。断点如果被破坏,中断后返回就会出现问题,中断标志不清会重复触发相同的中断。 尽管在8)中CPU已经保存了一些寄存器,但是中断服务程序千变万化在执行中还会破坏其他一些寄存器,这时需要在中断服务子程序开始执行前保存被破坏的寄存器。

概述

对于C28x,中断可以由软件(INTR,OR IFR,或TRAP指令)或硬件(定时器等)触发。在CPU级所有的中断可以分为两类: 1.可屏蔽中断。可以通过软件的方法屏蔽或使能中断。大部分硬件中断是可屏蔽中断。 2.不可屏蔽中断。不可用软件屏蔽的中断。一旦中断发生,就会立即得到响应。INTR,TRAP指令产生的软件中断都是不可屏蔽的。 中断的一般处理过程如下: 1).中断的申请。硬件或软件向CPU发出中断申请。 2).中断的允许。对于可屏蔽中断,只有相应的中断允许位置位后其中断才能得到响应。 3).中断判优。当同时有多个中断向CPU发出中断申请时,只有优先级高的才能得到系统的响应。 4).断点的保护。保护会被会被中断破坏掉的资源。一般是全部的CPU寄存器。 5).清中断标志。以免中断再次发生。 6).重新打开中断。这个可选。重新打开中断是为了使能中断的嵌套。 7).执行中断服务程序。这时才真正开始进行中断的处理。 8).断点的恢复和中断的返回。中断向量表和优先级

对于F28335,其中断向量表根据配置可以定位到3个不同的地方。当复位是VMAP =1 ,ENPIE=0。中断向量表定位在Boot ROM中的最后32*32个存储单元中。当设置VMAP=0时,向量表定位在0x000000开始的32*32的存储单元中。在CPU级,一共有32个中断,每个中断的向量一共有22位(程序的地址总线只有22位)。每个向量占用两个连续的地址,高地址存储高6位,低地址存低16位。存储在向量表中的高10位将会被忽略。由于F28335带有PIE模块,PIE模块对CPU的中断功能进行了扩充。当ENPIE =1,VMAP=1时,中断向量表定位到PF0区域中,如下图: 图1

PIE表的构造如下:

图1

PIE表的构造如下:

图2

从图中可得:

1.CPU级中断的优先级Reset优先级最高,但是系统复位时复位向量总是从0x3fffc0取。

2.CPU可屏蔽中断优先级顺序(从高到低):RTOSINT,INT1-INT14,DLOGINT。

3.INT1-INT12接PIE模块拓展了中断系统,INTx.1-INTx.8中断优先级依次降低。

图2

从图中可得:

1.CPU级中断的优先级Reset优先级最高,但是系统复位时复位向量总是从0x3fffc0取。

2.CPU可屏蔽中断优先级顺序(从高到低):RTOSINT,INT1-INT14,DLOGINT。

3.INT1-INT12接PIE模块拓展了中断系统,INTx.1-INTx.8中断优先级依次降低。

CPU级中断控制

在CPU级,可屏蔽中断包括INT1-INT14,RTOSINT和DLOGINT。INT1-INT14是通用中断,RTOSINT和DLOGINT是用于仿真的。这些中断的控制是由寄存器IFR,IER和DBGIER控制的。 IFR是中断申请标准寄存器 IER是中断允许寄存器 DBGIER是中断允许寄存器(在实时仿真模式下才使用)。 ST1中的第0位,INTM控制整个中断的屏蔽,INTM=1是所有中断都被屏蔽。 在某种条件下(软件或硬件)IFR置位,如果系统工作在正常模式下,IER中的相应位置位且INTM=0,则这个中断将得到响应。注意:RTOSINT,INT1-INT14,DLOGINT的中断优先级依次递减。如果工作在实时仿真模式下且CPU处于Halt状态,中断的允许由DBGIER决定INTM将被屏蔽。 中断允许条件如下表: 表1 DSP运行模式 中断允许条件 标准 INTM = 0,相应的IER为1 实时模式且CPU Halt IER且DBGIER相应位为1 几个寄存器的详细描述: IFR寄存器

图3 相应的位置位表示中断申请。寄存器的位格式同IER和DBGIER。 注意这个寄存器可以用软件置位实现软件中断,如OR IFR,#1,将会置位INT1用软件模拟中断的请求。 对于F28335其INT1-INT12外接了PIE模块,中断对INT1的处理会牵扯到PIE模块中的部分寄存器。这些将会在后续内容中详细的讲。INT13,INT14外接了CPU timer0,如下图所示:

图4 CPU对可屏蔽中断的的响应过程如下: 1)中断申请。 PIE模块通过将INT1-INT12中置位; 仿真逻辑通过置位RTOSINT或DLOGINT; 通过执行指令OR IFR,#x将IFR中某一位置位。 2)中断允许。 中断申请后,只有得到允许才能受到CPU的处理。中断允许条件见表1. 3) 中断的判优。 当同时有多个中断申请时,优先级高的讲得到响应。中断的优先级见2 4)清除IFR中相应位。 一旦中断得到相应,IFR中的相应位就会被清除。在得到响应到进入中断服务子程序之前,所有的中断都会被屏蔽。 5)清除流水线。 6)保存PC值。 保存PC的值(中断返回后要执行的指令地址)到一个内部寄存器。在自动上下午切换时,该值会被压入堆栈。 7)获得中断向量。 CPU根据中断源获得相应的中断向量。由于F28335有PIE模块,一般情况下其中断向量表将定位到PIE Vector,PIE Vector的结构见图2 8)执行自动上下文切换。 上下文切换就是断点的保存。自动保存的CPU寄存器和顺序如下图: 1stST0,T 2nd AL,AH 3rd PL,PH 4st AR0,AR1 5st ST1,DP 6st IER,DBGSTAT 7st Return address 9)清除IER中的相应位。 这样使正在服务的中断源被屏蔽。当然如果想使能中断嵌套的话可以从新将其置位。 10)置位INTM,DBGM,清除LOOP,EALLOW,IDLESTAT位。 置位INTM禁止所有可屏蔽中断。 11)将在第7)中得到的中断向量加载到PC,开始执行中断服务程序。 12)中断的返回。C28x系列CPU中断的返回通过IRET指令。 C28x系列CPU中IRET指令完成的断点的恢复,执行IRET指令CPU会按照进入中断时入栈的相反顺序将相应寄存器弹出堆栈。 对于使用中断来说,写程序最需要注意的是中断的断点保护和中断标志的清除。断点如果被破坏,中断后返回就会出现问题,中断标志不清会重复触发相同的中断。 尽管在8)中CPU已经保存了一些寄存器,但是中断服务程序千变万化在执行中还会破坏其他一些寄存器,这时需要在中断服务子程序开始执行前保存被破坏的寄存器。