DSP入门:中断PIE

1、DSP中断管理分为3个层次:外设级,PIE级,CPU级。其中,外设级中断管理负责具体外设中断源的允许与禁止,PIE级中断管理负责对外设级中断分组并按照优先级管理,CPU内核级中断管理则负责处理直接向CPU申请的中断请求。

DSP控制器的外设中断扩展模块(PIE),对中断进行集中化扩展,使每一级CPU中断均可以响应多个中断源。

2、PIE级中断及管理:

CPU内核级中断(INT1–INT14),INT1-INT12被PIE模块用来进行中断扩展,有12组,每组8个中断源。

各中断的优先级自上而下,由右到左逐步降低,总体优先级INT1最高,INT12最低。

各中断的优先级自上而下,由右到左逐步降低,总体优先级INT1最高,INT12最低。 INT13由CPU定时器1和外部中断XINT13复用,INT14由定时器2独占。

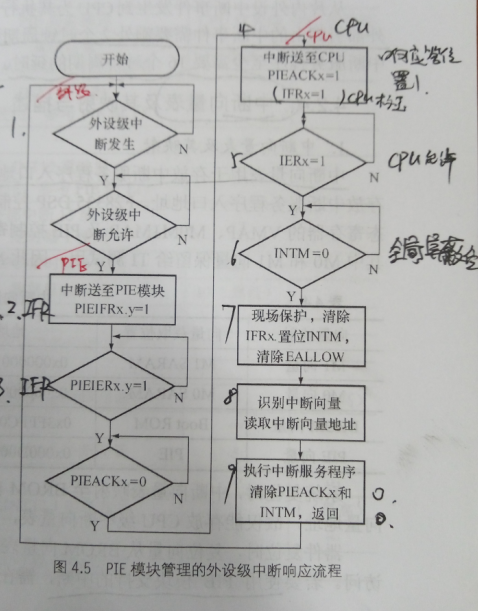

3、中断响应过程

4、中断寄存器介绍

- PIEIFRx (1-12)中断标志寄存器

- PIEIERx (1-12)中断屏蔽寄存器

各有12个,每个16位宽,只用了前8位分别表示8个中断源;IFR标志中断到来,IER表示是否要响应(PIEIFRx.1-8,PIEIERx.1-8) - PIEACKx (1-12)应答位

CPU是否响应给位的中断,为0中断送入CPU,为1等待 - PIECTRL PIE控制寄存器,只读

读取中断向量 - XINTnCR (n为1-7) 7个外部中断

选择中断边沿,01上升沿;外部中断允许位

5、代码片

PieCtrlRegs.PIEIFR1.bit.INTx4=1;//在PIE中断组1设置XINT1的中断标志位

PieCtrlRegs.PIEIER1.bit.INTx4=1;//允许PIE中断组1的XINT1 中断

PieCtrlRegs.PIEACK.all = 0x0004;//清除中断组3的ACK位,以便再次响应

PieCtrlRegs.PIECTRL.bit.ENPIE=1;//允许从向量表中读取中断向量- 1

- 2

- 3

- 4

- 5

6、定时器中断实例

#include "DSP2833x_Device.h"

#include "DSP2833x_Examples.h"

interrupt void cpu_timer0_isr(void);//声明中断服务函数

void main()

{

//step1:初始化系统控制、PLL、看门狗、允许外设时钟

InitSysCtrl();

//step2:初始化GPIO

InitGpio();

//step3:清除所有中断,初始化PIE向量表

DINT;

InitPieCtrl(); //初始化PIE控制器

IER = 0x0000; //禁止CPU中断

IFR = 0x0000; //清除所有CPU中断标志

InitPieVectTable(); //初始化PIE中断向量表

EALLOW;

PieVectTable.TINT0 = &cpu_timer0_isr; //重映射中断向量,指向中断服务程序

EDIS;

//step4:初始化外设模块

InitCpuTimers();

ConfigCpuTimer(&CpuTimer0,150,1000000); //150MHz,周期1秒

CpuTimer0Regs.TCR.all = 0x4001; //允许定时器中断,且设置TSS为0启动定时器工作

//step5:

IER |= M_INT1; //允许CPU的INT1中断,该中断连接至TINT0

PieCtrlRegs.PIEIER1.bit.INTx7 = 1; //在PIE中断组1中允许TINT0中断

EINT; //清除全局屏蔽

ERTM; //允许全局实时中断

//step6:循环

while(1);

}

interrupt void cpu_timer0_isr(void)

{

CpuTimer0.InterruptCount++;

PieCtrlRegs.PIEACK.all = PIEACK_GROUP1; //清除PIE中断组1的应答位,以便CPU再次响应

}

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

后续实例,先占个坑- 1