refer:http://blog.csdn.net/lxl584685501/article/details/46771623

基带数字处理功能以及手机基本外围功能都集中到单片片上系统(SOC)中,其基本构架都采用了微处理器+数字信号处理器(DSP)的结构,微处理器和DSP的处理能力一直增强。 (1)微处理器是整颗芯片的控制中心,会运行一个实时嵌入式操作系统(如Nucleus PLUS)。 (2)DSP 子系统是基带处理的重点,其中包含了许多硬件加速器和基带专用处理模块,完成所有物理层功能。 现在,随着实时数字信号处理技术的发展,ARM微处理器(会采用不同的微系列,如3G芯片多采用ARM9)、DSP 和 FPGA 体系结构成为移动终端芯片实现的主要方式。

2.基于ARM架构的基带芯片的逻辑架构

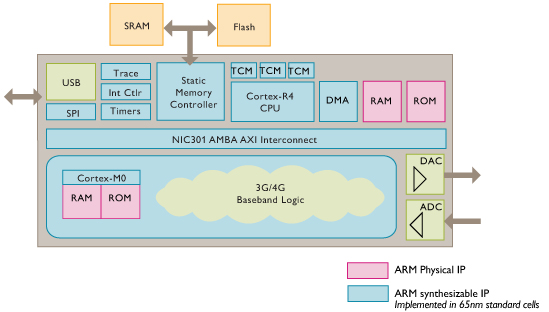

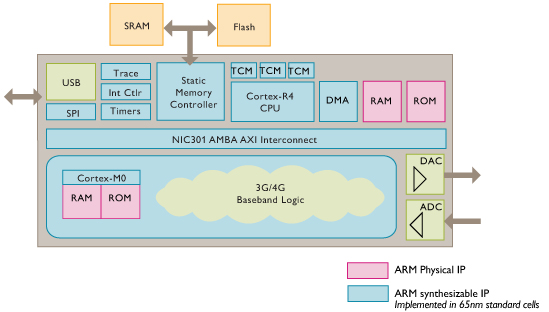

下图是典型的基于ARM架构的基带芯片的逻辑架构,其中3G/4G Baseband Logic指的是DSP运算子系统。

图1 典型ARM架构上的基带芯片框架 (1)微处理器通过实时操作系统RTOS(如Nucleus PLUS)完成多任务的调度、任务间通信、外设驱动以及微处理器与DSP子系统及其他模块的通信等等。功能还包括: 1,对整个移动台进行控制和管理,包括定时控制、数字系统控制、射频控制、省电控制等。 2,完成所有的软件功能,即无线通信协议的物理层与协议栈的通信、高层协议栈(TCP/IP等),若用于功能机则还会包括MMI(人-机交互接口)和应用软件。 (2)DSP 子系统则用于物理层所有算法的处理,包括信息的信道编码、加密、信道均衡、语音编码/解码、调制解调等。DSP 子系统和微处理器子系统之间的数据通信手段包括双端口随机读取存储器(RAM)、多总线共享资源(一些厂商采用了AMBA公司的多层总线协议)等。多模多频基带芯片中可能包含多颗DSP。 (3)在存储器组织方面,微处理器和DSP子系统可能都有各自独立的高速缓冲存储器(Cache),有共享的片内SRAM和共享的外扩存储器。扩展存储器普遍支持同步动态随机存储器(SDRAM)和NAND型Flash RAM等。 FLASH ROM可用于存储Boot Rom、链接操作系统和用户应用程序的CP Rom。ROM接口主要用来连接存储程序的存储器FLASH ROM,RAM接口主要用来连接存贮暂存数据的静态RAM(SRAM)。片内嵌入大容量静态随机读取存储器(SRAM)已非常普遍,有利于降低功耗,减少系统成本。 Intel公司还嵌入了大容量的闪速存储器(Flash RAM)。 (4)外设和接口方面,基带芯片往往支持多种接口以方便和应用处理器的通信以及增加其他模块如Wifi、GPS。接口包括UART、多媒体接口(MMI)、通用串行总线(USB)、SPI等。 MCU与外部接口的通信可通过DMA进行,若基带芯片没有集成RF,则还有RF专用接口。

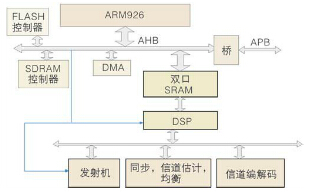

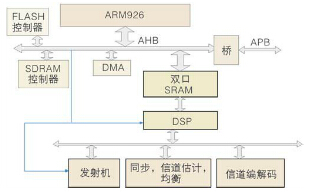

如图2是传统双核基带芯片的架构图,其中蓝 {MOD}单线表示ARM对DSP子系统的直接控制。

图2 传统基带芯片主架构 采用双口SRAM进行ARM和DSP子系统的数据交互原因有:(1)两个子系统的时钟通常不一致,SRAM则可以做良好的桥接;(2)SRAM数据交互带宽较大、功耗低。实施过程中要注意读、写的同步问题,预防两个子系统对同一块数据的同时读写。可通过设置一个信号量控制,一方读(写)时另一方不得写(读)。

图3 GSM/EDGE/TD-SCDMA三模基带芯片框图 由于GSM/EDGE物理层算法基本一致,两者的调制方式虽不同(GSM采用GMSK、EDGE采用8PSK)但解调方式一致-都是Viterbi译码,因此两者物理层处理共享一个DSP加上一些额外的硬件支持。TD-SCDMA的物理层算法则与GSM/EDGE有很大差距,有完全不同的实现体系,尤其是TD-SCDMA的联合检测算法需要大量的计算,因此需要独立的DSP子系统实现。 多模终端的一大技术要点是通信模式的切换,这就需要基带芯片的支持。若是手动切换模式就比较简单,不同模式的DSP子系统彼此独立、简单的捆绑,MCU 中不同模式的协议栈也独立创建任务即可。实际商用中手动切换那是会被用户无情的抛弃的,因此多模终端必须能够智能探测不同模式的信号强度,自动完成模式切换,这一切最好都要在用户感觉不到的情况下进行。多模基带的模式自动切换就需要额外的设计难度了,需要将多种模式的协议栈紧密糅合、各自的物理层之间还有必要的数据通信。各种通信模式互切换的规范和算法使得MCU上多种模式协议栈的糅合称为可能,物理层信息共享则可通过在不同DSP子系统间建立简单直连(如寄存器或SPI等)进行。 若是所有的通信模式都封装在一颗芯片上,由一个主控处理器控制时模式切换相对简单。能做到单芯片支持全模的只有高通一家。大部分终端基带方案都两颗甚至多棵基带芯片的组合,如CDMA/GSMg 基带+LTE 基带,两颗基带芯片间通过SPI, SDIO , USB 等通信。

(一)概述

1.基带芯片SOC架构基带数字处理功能以及手机基本外围功能都集中到单片片上系统(SOC)中,其基本构架都采用了微处理器+数字信号处理器(DSP)的结构,微处理器和DSP的处理能力一直增强。 (1)微处理器是整颗芯片的控制中心,会运行一个实时嵌入式操作系统(如Nucleus PLUS)。 (2)DSP 子系统是基带处理的重点,其中包含了许多硬件加速器和基带专用处理模块,完成所有物理层功能。 现在,随着实时数字信号处理技术的发展,ARM微处理器(会采用不同的微系列,如3G芯片多采用ARM9)、DSP 和 FPGA 体系结构成为移动终端芯片实现的主要方式。

2.基于ARM架构的基带芯片的逻辑架构

下图是典型的基于ARM架构的基带芯片的逻辑架构,其中3G/4G Baseband Logic指的是DSP运算子系统。

图1 典型ARM架构上的基带芯片框架 (1)微处理器通过实时操作系统RTOS(如Nucleus PLUS)完成多任务的调度、任务间通信、外设驱动以及微处理器与DSP子系统及其他模块的通信等等。功能还包括: 1,对整个移动台进行控制和管理,包括定时控制、数字系统控制、射频控制、省电控制等。 2,完成所有的软件功能,即无线通信协议的物理层与协议栈的通信、高层协议栈(TCP/IP等),若用于功能机则还会包括MMI(人-机交互接口)和应用软件。 (2)DSP 子系统则用于物理层所有算法的处理,包括信息的信道编码、加密、信道均衡、语音编码/解码、调制解调等。DSP 子系统和微处理器子系统之间的数据通信手段包括双端口随机读取存储器(RAM)、多总线共享资源(一些厂商采用了AMBA公司的多层总线协议)等。多模多频基带芯片中可能包含多颗DSP。 (3)在存储器组织方面,微处理器和DSP子系统可能都有各自独立的高速缓冲存储器(Cache),有共享的片内SRAM和共享的外扩存储器。扩展存储器普遍支持同步动态随机存储器(SDRAM)和NAND型Flash RAM等。 FLASH ROM可用于存储Boot Rom、链接操作系统和用户应用程序的CP Rom。ROM接口主要用来连接存储程序的存储器FLASH ROM,RAM接口主要用来连接存贮暂存数据的静态RAM(SRAM)。片内嵌入大容量静态随机读取存储器(SRAM)已非常普遍,有利于降低功耗,减少系统成本。 Intel公司还嵌入了大容量的闪速存储器(Flash RAM)。 (4)外设和接口方面,基带芯片往往支持多种接口以方便和应用处理器的通信以及增加其他模块如Wifi、GPS。接口包括UART、多媒体接口(MMI)、通用串行总线(USB)、SPI等。 MCU与外部接口的通信可通过DMA进行,若基带芯片没有集成RF,则还有RF专用接口。

(二)传统ARM基带芯片基本框架

单模基带芯片采用双核架构,一个ARM处理器和一个DSP,两者之间的通信通过双端口静态存储器(Dual port SRAM)进行。同时,ARM还会对DSP子系统做一些直接的控制,通过直接操作寄存器(地址/控制/数据寄存器)完成。 当然,对于一些运算能力比较强的DSP,1个ARM+1个DSP+多个加速器子系统也可实现多模基带。如图2是传统双核基带芯片的架构图,其中蓝 {MOD}单线表示ARM对DSP子系统的直接控制。

图2 传统基带芯片主架构 采用双口SRAM进行ARM和DSP子系统的数据交互原因有:(1)两个子系统的时钟通常不一致,SRAM则可以做良好的桥接;(2)SRAM数据交互带宽较大、功耗低。实施过程中要注意读、写的同步问题,预防两个子系统对同一块数据的同时读写。可通过设置一个信号量控制,一方读(写)时另一方不得写(读)。

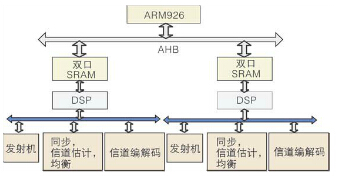

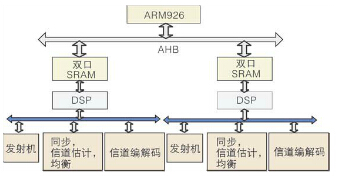

(三)多模基带基本框架

多模移动终端基带芯片成为必然,即最终在一颗基带芯片上支持所有的移动网络和无线网络制式,包括2G、3G、4G和WiFi等,多模移动终端可实现全球范围内多个移动网络和无线网络间的无缝漫游。多种通信模式汇集在一颗芯片内会大大增加芯片的实现难度,不仅要设计通用的移动通信模式实现平台,还要在有限的尺寸范围内为每种通信模式增设特有的加速单元、MCU 上和不同模式子系统之间则还要考虑模式切换所必须的通信管理。MCU 上的软件复杂程度变高,不同模式子系统间因为要共享一些数据(如基站信号强度)也需要一些数据的直接交换。 本节以GSM/EDGE/TD-SCDMA 三模基带芯片的基本架构为例描述了多模基带芯片的逻辑架构。 该三模芯片又一个ARM9、两个DSP子系统实现,ARM和俩DSP子系统间的通信依然是双口SRAM,如图3所示。

图3 GSM/EDGE/TD-SCDMA三模基带芯片框图 由于GSM/EDGE物理层算法基本一致,两者的调制方式虽不同(GSM采用GMSK、EDGE采用8PSK)但解调方式一致-都是Viterbi译码,因此两者物理层处理共享一个DSP加上一些额外的硬件支持。TD-SCDMA的物理层算法则与GSM/EDGE有很大差距,有完全不同的实现体系,尤其是TD-SCDMA的联合检测算法需要大量的计算,因此需要独立的DSP子系统实现。 多模终端的一大技术要点是通信模式的切换,这就需要基带芯片的支持。若是手动切换模式就比较简单,不同模式的DSP子系统彼此独立、简单的捆绑,MCU 中不同模式的协议栈也独立创建任务即可。实际商用中手动切换那是会被用户无情的抛弃的,因此多模终端必须能够智能探测不同模式的信号强度,自动完成模式切换,这一切最好都要在用户感觉不到的情况下进行。多模基带的模式自动切换就需要额外的设计难度了,需要将多种模式的协议栈紧密糅合、各自的物理层之间还有必要的数据通信。各种通信模式互切换的规范和算法使得MCU上多种模式协议栈的糅合称为可能,物理层信息共享则可通过在不同DSP子系统间建立简单直连(如寄存器或SPI等)进行。 若是所有的通信模式都封装在一颗芯片上,由一个主控处理器控制时模式切换相对简单。能做到单芯片支持全模的只有高通一家。大部分终端基带方案都两颗甚至多棵基带芯片的组合,如CDMA/GSMg 基带+LTE 基带,两颗基带芯片间通过SPI, SDIO , USB 等通信。