外设数据流

外设数据流概念

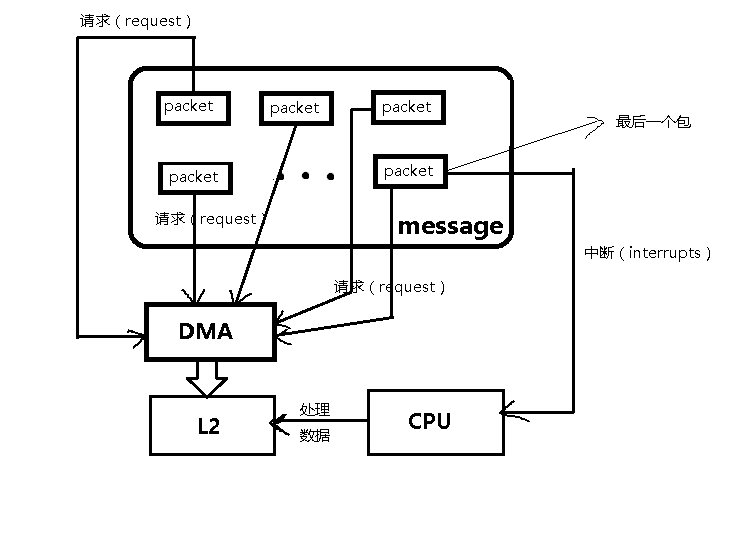

SRIO是一个外部驱动的从模块,但能够在dsp上扮演主模块的角 {MOD},意思就是他能够直接向dsp推送所需的数据而不需要产生中断或者通过DMA。这有一个好处就是减少来中断数量,减少来与只读中断的握手时间,并将EDMA释放给其他任务。SRIO确定数据包(packet)的有效载荷(payload)最高有256个字节,很多时候,数据的交换(transactions)跨越很多个数据包,Rapid IO规定每条消息(message)最多含有16个数据包,尽管在包数据传输时,会为每个包对dsp产生一个请求,这样就可以让DMA把数据传送到L2(L2缓存)中去,但是中断只会在最后一个包处理之后产生,该中断是传输结束的标志,标志着CPU可以开始处理L2中的数据。以上这段话所描述的过程,为了便于读者理解,笔者作了相关流程图。

数据包接收模式

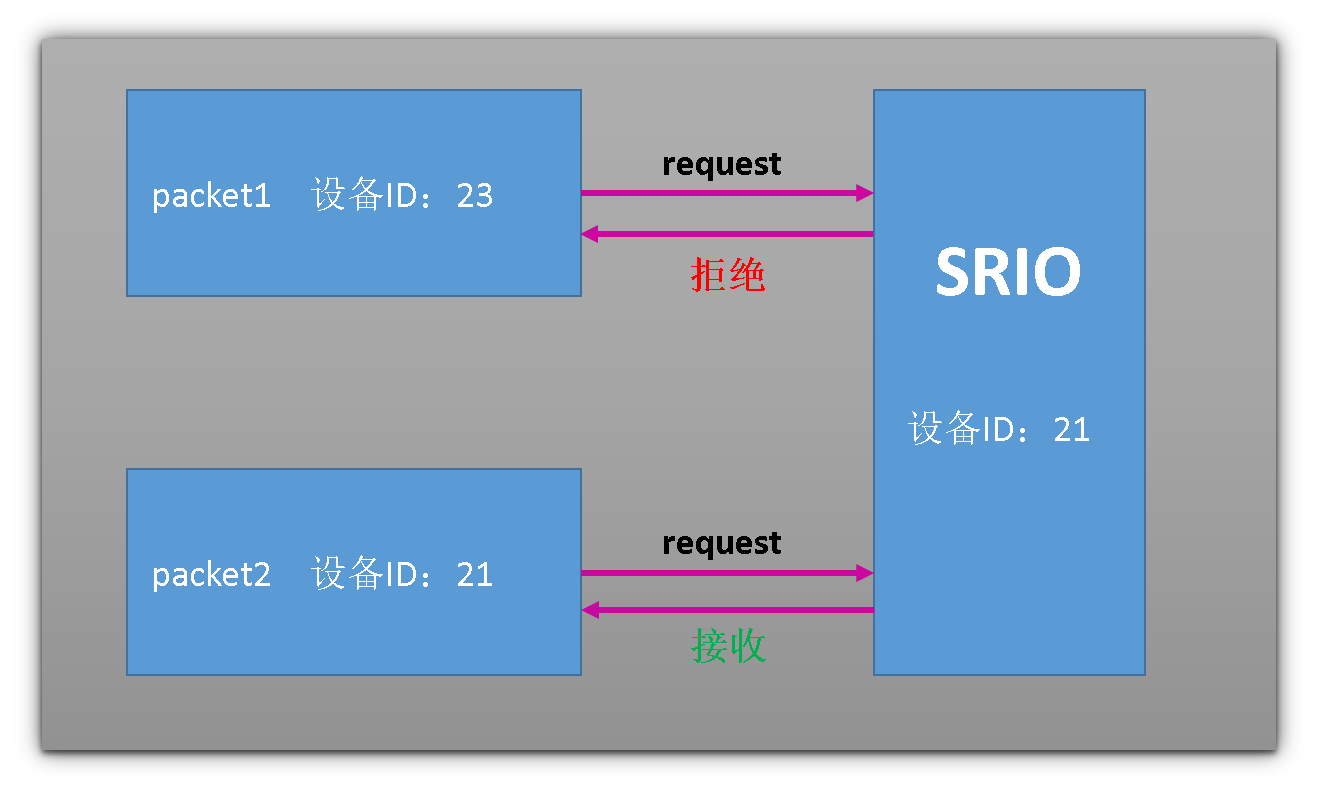

SRIO作为一个端点设备(endpoint device),SRIO接收的是基于目标ID(destination ID)的数据包。有两种数据包接收模式:1、本地接收

第一种模式是SRIO只接收那些目标ID与自己(SRIO)的本地ID相同的数据包,这种接收模式提供了一层安全保障。

2、系统多点传送操作

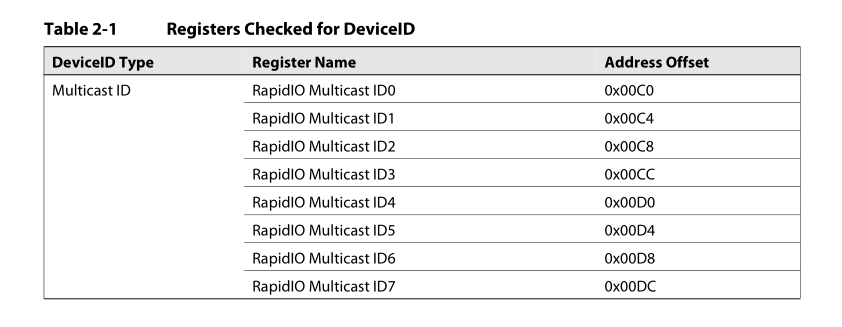

当多点传送开启时,所有流向SRIO的数据包,只要符合Base Routing Register(TLM port n BRR pattern and match registers)或符合table 2-1中的目标ID号的包,都会被接收。

2.1使能多点传送

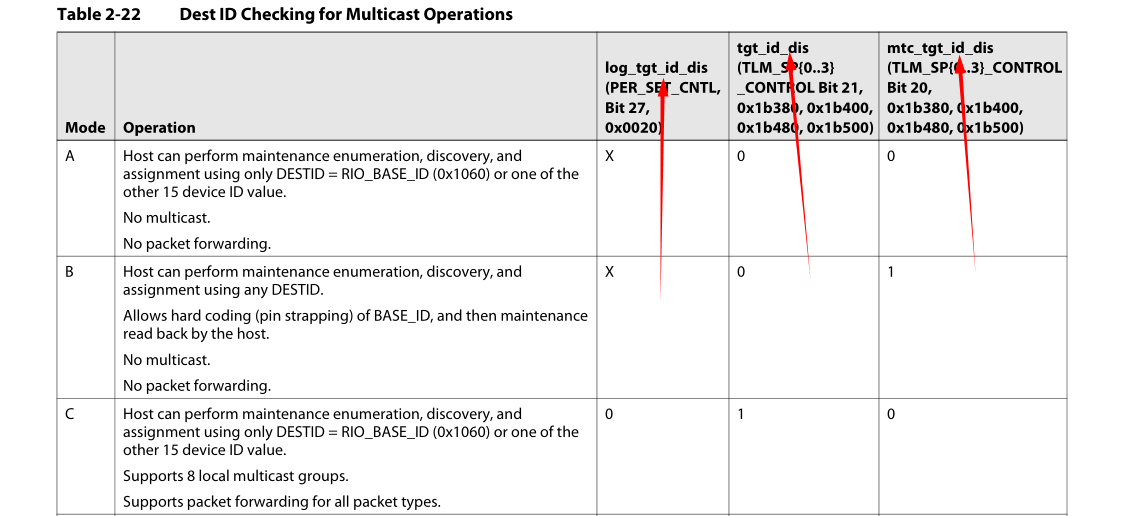

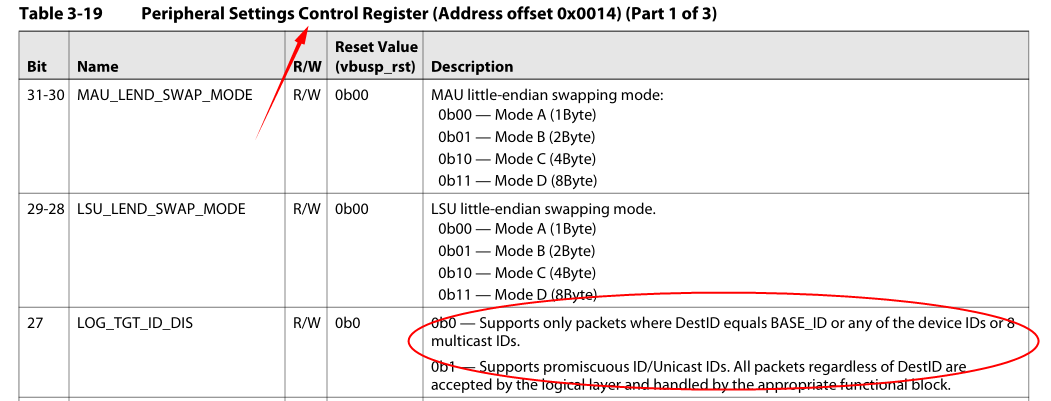

以模式C为例,可以看到在模式C下,主机可以只使用DESTID = RIO_BASE_ID(0X1060),或者与0X1060地位相同的RIO的其余15个设备ID号,就能完成维护枚举,发现和分配操作。模式C支持8个本地多点传送,也支持所有类型包的转发,但支持的这两种情况需要寄存器PER_SET_CNTL的第27位(LOG_TGT_ID_DIS )设置不同的值,由Table3-19可以得出,对第27位设置为二进制0支持第一种情况,设置为二进制1支持第二种情况。其它模式也用相同的方式操作即可。PS:Table 2-22 中的X表示对该位的设置不是二进制的0或1,而是两位或三位或更多。

以模式C为例,可以看到在模式C下,主机可以只使用DESTID = RIO_BASE_ID(0X1060),或者与0X1060地位相同的RIO的其余15个设备ID号,就能完成维护枚举,发现和分配操作。模式C支持8个本地多点传送,也支持所有类型包的转发,但支持的这两种情况需要寄存器PER_SET_CNTL的第27位(LOG_TGT_ID_DIS )设置不同的值,由Table3-19可以得出,对第27位设置为二进制0支持第一种情况,设置为二进制1支持第二种情况。其它模式也用相同的方式操作即可。PS:Table 2-22 中的X表示对该位的设置不是二进制的0或1,而是两位或三位或更多。

2.2 ID号的对比

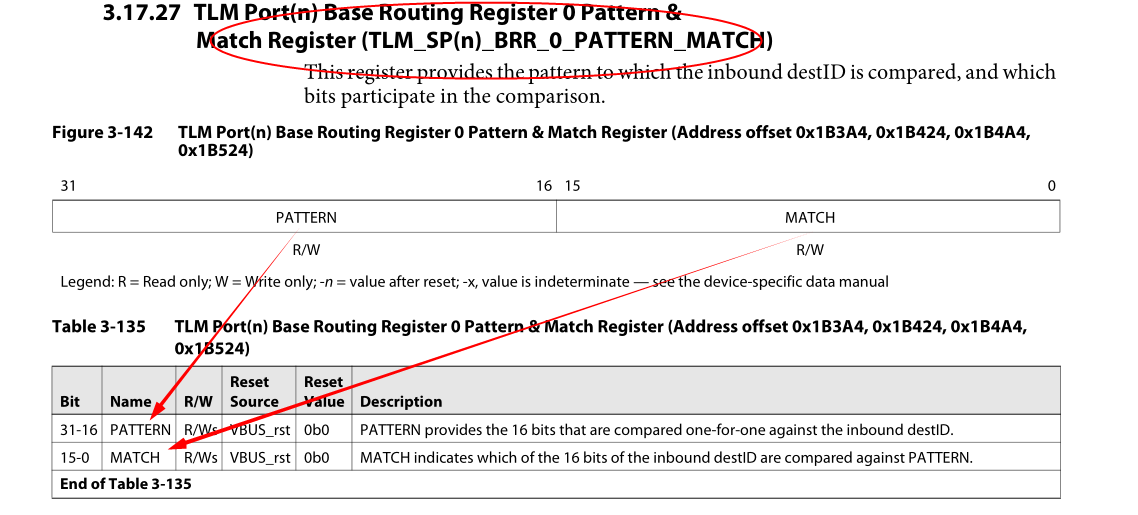

TLM_SP(n)_BRR_0_PATTERN_MATCH寄存器的相关设置提供了与被传输进来的destID进行对比的模板ID;同时提供了哪一位参与比较功能。PATTERN段的16位提供了与destID进行一位一位比较的一个16位二进制数,可以看做一个比较模板。

TLM_SP(n)_BRR_0_PATTERN_MATCH寄存器的相关设置提供了与被传输进来的destID进行对比的模板ID;同时提供了哪一位参与比较功能。PATTERN段的16位提供了与destID进行一位一位比较的一个16位二进制数,可以看做一个比较模板。 MATCH段指明了被传输进来的destID的哪一位参与,与PATTERN提供的模板的比较。PS:设备ID寄存器1到设备ID寄存器15中的设备ID值,都是继承自PATTERN中的16位数。参考文献

http://www.ti.com/cn/litv/pdf/sprugw1bPS:欢迎大家与我讨论文章中的问题,包括反对我的观点。-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.

分割线//还有一些数据流的问题没有讲清楚,特此补充

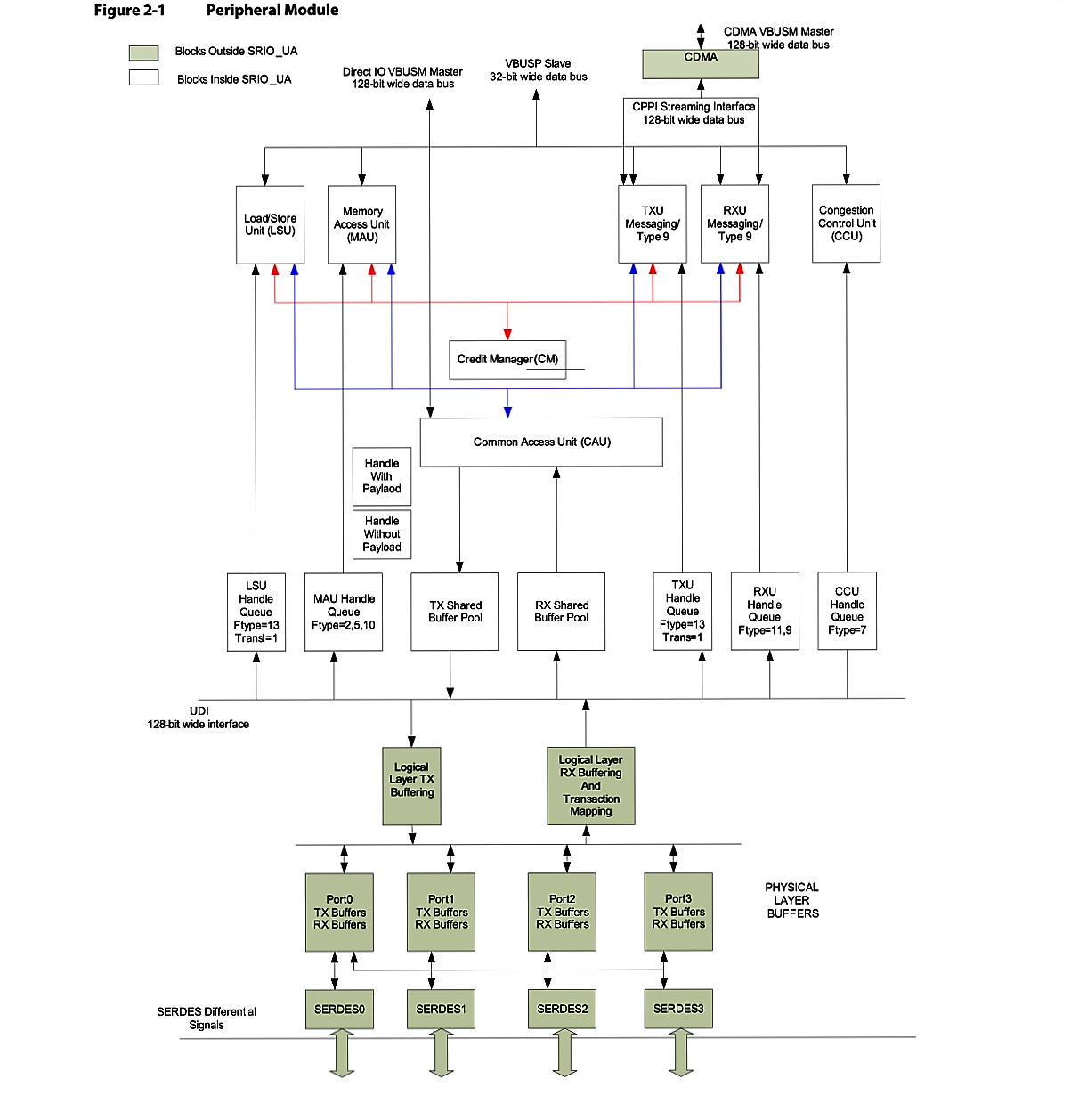

-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.-.通过外设的数据流可以使用Figure 2-1解释。

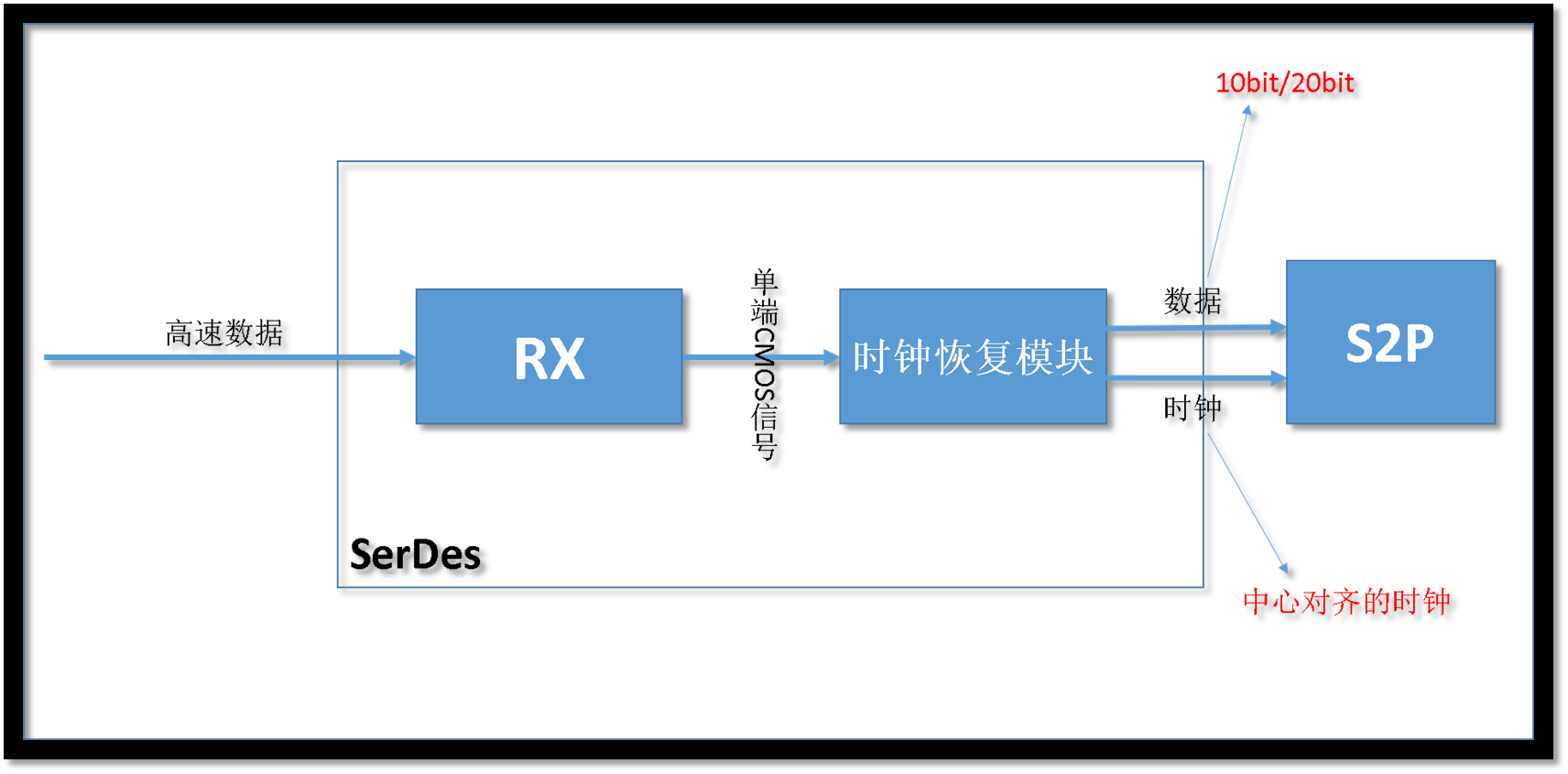

关键词:S2P SerDes 单端CMOS 时钟恢复模块【高速数据从设备管脚进入SerDes(串行/解串器)的RX(接收)区域。RX块差分接收器接收至少175mv峰值差分输入电压(VID)。电平转换在RX区域进行,转换之后的输出是单端CMOS,然后将串行数据送入SerDes时钟恢复模块。这个时钟恢复模块唯一的目的是从数据流中提取出一个时钟信号,要做到这一点,必须有一个低频参考信号,频率是数据频率的十分之一或二十分之一。

关键词:S2P SerDes 单端CMOS 时钟恢复模块【高速数据从设备管脚进入SerDes(串行/解串器)的RX(接收)区域。RX块差分接收器接收至少175mv峰值差分输入电压(VID)。电平转换在RX区域进行,转换之后的输出是单端CMOS,然后将串行数据送入SerDes时钟恢复模块。这个时钟恢复模块唯一的目的是从数据流中提取出一个时钟信号,要做到这一点,必须有一个低频参考信号,频率是数据频率的十分之一或二十分之一。 例如,3.125Gbps的数据,参考频率(refclk)就应该是 312.5Mhz 或156.25Mhz 或125MHz。通常来说,这个时钟是来自片外稳定的晶振,并且是一个LVDS器件单独输入给SERDES的。

将这个时钟分给SerDes的PLL锁相环模块,这样锁相环可以将这个时钟倍频到数据频率。创建高速时钟相位并传递给时钟恢复模块,(The clock recovery blocks further interpolate between these clocks to provide maximum Unit Interval (UI) resolution on the recovered clock. )时钟恢复模块进一步贯穿在这些时钟中间, 提供最大单位间隔(UI)的恢复时钟分辨率。

时钟恢复块对输入的数据进行采样,并监视数据边缘的相对位置(即输入的上升沿和下降沿)。有了这些信息,它就可以向S2P块提供数据和中心对齐的时钟。S2P使用新的时钟恢复模块并将这些输入的数据分解为10bit或20bit的字。在这一点上,离开SerDes的数据频率是管脚频率的十分之一或者二十分之一,伴随着一个中心对齐时钟,5G频率的操作能使用20bit的SerDes模块。】便于读者理解,我画了该段的示意图:

在物理层,数据之后会去8b/10b解码块,RapidIO采用8b/10b编码,以确保为时钟恢复电路提供充足的数据转换。编码时有20%的编码被删除,因为10位码被编辑为了8位码,在这里恢复位时钟依然在使用。下一步是时钟同步和数据分配。这些功能是由FIFO和线偏移校正块管理的,FIFO提供了一种弹性存储机制,来确保恢复时钟域和系统时钟的交流。经过FIFO之后,四条线变成频率和相位都同步的,1X,2X,4X模式都能用。FIFO队列有8个字的深度,只有在4X模式下线偏移校正才是有意义的,该模式用下线偏移校正来分配每个频道的字边界,这样最终32bit的字才是分配正确的。CRC错误检测模块持续记录分别在1X,2X,4X模式下,输入的数据和持续计算CRC值得期望值,算得的这个CRC值与最终的接收完最后一个包时的CRC值进行比较。包到达物理层之后,包区(packet fileds)会被解码并且包的payload会存在缓存中,基于包的类型,包会分配到控制DMA的功能区。这些功能区就是figure2-1里的LSU、MAU、TXU、RXU和CCU。LSU控制的是DirectIO包的传输,MAU控制的是DirectIO的接收,LSU也控制维护包的传输,TXU和RXU分别控制消息包(message packet)的传输和接收,这四个单元使用内部DMA与内部存储进行交流,使用缓存和接收传递ports与外部设备进行交流。参考文献

在物理层,数据之后会去8b/10b解码块,RapidIO采用8b/10b编码,以确保为时钟恢复电路提供充足的数据转换。编码时有20%的编码被删除,因为10位码被编辑为了8位码,在这里恢复位时钟依然在使用。下一步是时钟同步和数据分配。这些功能是由FIFO和线偏移校正块管理的,FIFO提供了一种弹性存储机制,来确保恢复时钟域和系统时钟的交流。经过FIFO之后,四条线变成频率和相位都同步的,1X,2X,4X模式都能用。FIFO队列有8个字的深度,只有在4X模式下线偏移校正才是有意义的,该模式用下线偏移校正来分配每个频道的字边界,这样最终32bit的字才是分配正确的。CRC错误检测模块持续记录分别在1X,2X,4X模式下,输入的数据和持续计算CRC值得期望值,算得的这个CRC值与最终的接收完最后一个包时的CRC值进行比较。包到达物理层之后,包区(packet fileds)会被解码并且包的payload会存在缓存中,基于包的类型,包会分配到控制DMA的功能区。这些功能区就是figure2-1里的LSU、MAU、TXU、RXU和CCU。LSU控制的是DirectIO包的传输,MAU控制的是DirectIO的接收,LSU也控制维护包的传输,TXU和RXU分别控制消息包(message packet)的传输和接收,这四个单元使用内部DMA与内部存储进行交流,使用缓存和接收传递ports与外部设备进行交流。参考文献http://www.ti.com/cn/litv/pdf/sprugw1b