摘要: 阐述了雷达中频正交采样的原理, 研究了使用 System Generator实现数字下变频的一种自顶向下的新型设计方法。在 Simulink中进行了功能仿真验证, 生成了 HDL代码, 并在 X ili nx FPGA中进行了 RTL的时序仿真分析。

数字下变频的硬件设计主要采用专用 DSP芯片或 FPGA 实现。与基于软件处理的 DSP 芯片相比,FPGA的集成度高、逻辑实现能力强、设计灵活性更好。数字下变频采用 FPGA实现逐渐成为一种趋势。

但是, 由于 VHDL、Verilog语言的严谨性和 FPGA内部结构的复杂性, 利用 FPGA来实现一个高效的数字下变频, 会占去较多的时间。 System Generator是Xilinx公司和 Mathw or ks合作开发的一款 FPGA辅助设计工具, 它降低了 FPGA设计门槛, 使用者只需在S i mulink中完成模型的搭建, 启动 System Generator ,就能自动生成 VHDL或 V eri log源程序及其他一些工程文件, 并将系统模型映射到目标器件 FPGA上进行硬件实现。本文采用

System Generator设计了数字下变频, 避开传统设计过程中采用 HDL编程的复杂环节, 缩短了设计所需时间。

1、数字下变频的原理

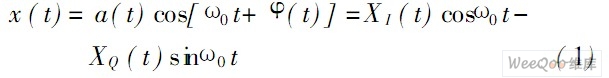

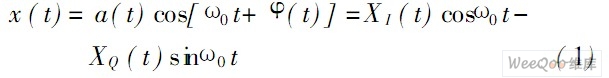

一个中频带通信号可表示为:

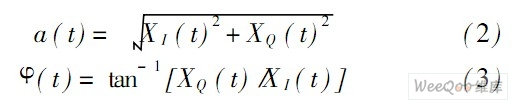

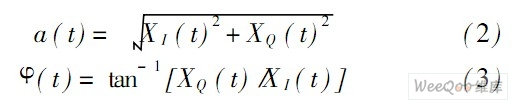

其中, Xi( t) = a(t)cosψ( t), XQ ( t ) = a ( t) sinψ(t)分别成为 x (t)的同相分量和正交分量;w0 为载频a (t), ψ(t)分别为包络和相位, 且有如下关系:

其中, Xi( t) = a(t)cosψ( t), XQ ( t ) = a ( t) sinψ(t)分别成为 x (t)的同相分量和正交分量;w0 为载频a (t), ψ(t)分别为包络和相位, 且有如下关系:

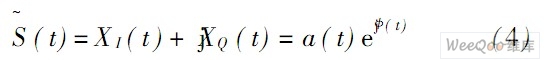

在雷达应用中, 输出信号可以表示为:

在雷达应用中, 输出信号可以表示为:

S~( t)称为信号的复包络。实信号 x ( t)的正负频谱是共轭对称的, 而其复包络 S~( t)就包含了 x ( t)中的所有信息 。

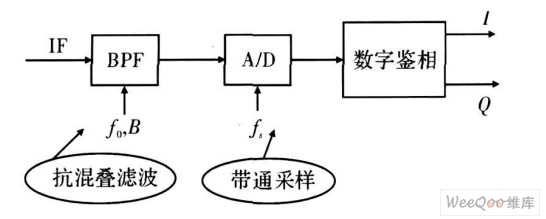

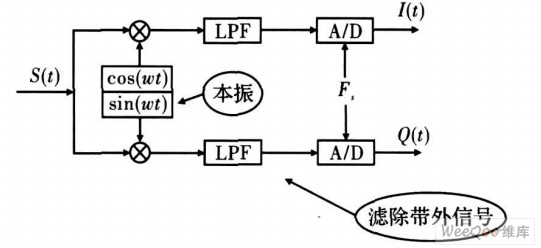

对复包络进行采样的传统方法是正交双通道采样, 如图 1所示。

S~( t)称为信号的复包络。实信号 x ( t)的正负频谱是共轭对称的, 而其复包络 S~( t)就包含了 x ( t)中的所有信息 。

对复包络进行采样的传统方法是正交双通道采样, 如图 1所示。

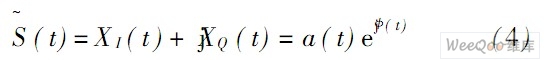

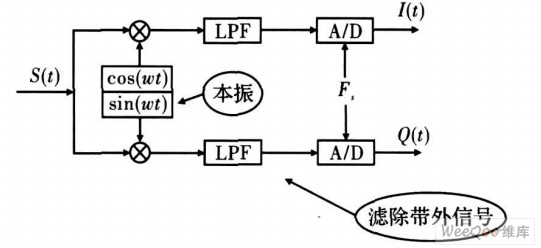

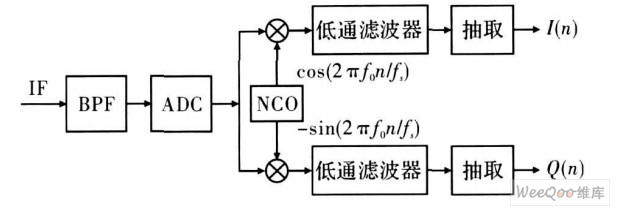

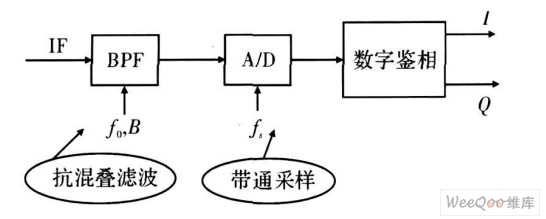

但是由于模拟电路存在漂移和不一致性, 使得到的两路信号并不是完全正交的, 而是存在一定的幅度和相位误差。直接中频采样与数字正交相干检波技术则可以较好地克服上述模拟方法存在的问题。中频直接采样实现正交相干检波的一般原理如图 2所示。

但是由于模拟电路存在漂移和不一致性, 使得到的两路信号并不是完全正交的, 而是存在一定的幅度和相位误差。直接中频采样与数字正交相干检波技术则可以较好地克服上述模拟方法存在的问题。中频直接采样实现正交相干检波的一般原理如图 2所示。

图 2数字中频正交采样

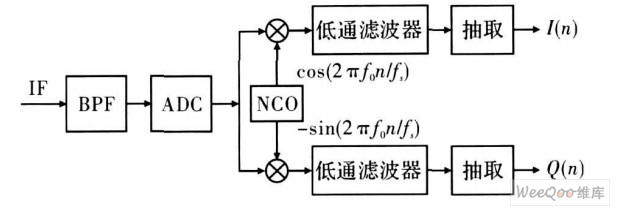

应用低通滤波法进行数字下变频的研究。低通滤波法是一种完全仿照传统模拟正交采样的实现方法, 只是将移频放在 A /D变换之后, 其原理框图如图 3所示。

图 2数字中频正交采样

应用低通滤波法进行数字下变频的研究。低通滤波法是一种完全仿照传统模拟正交采样的实现方法, 只是将移频放在 A /D变换之后, 其原理框图如图 3所示。

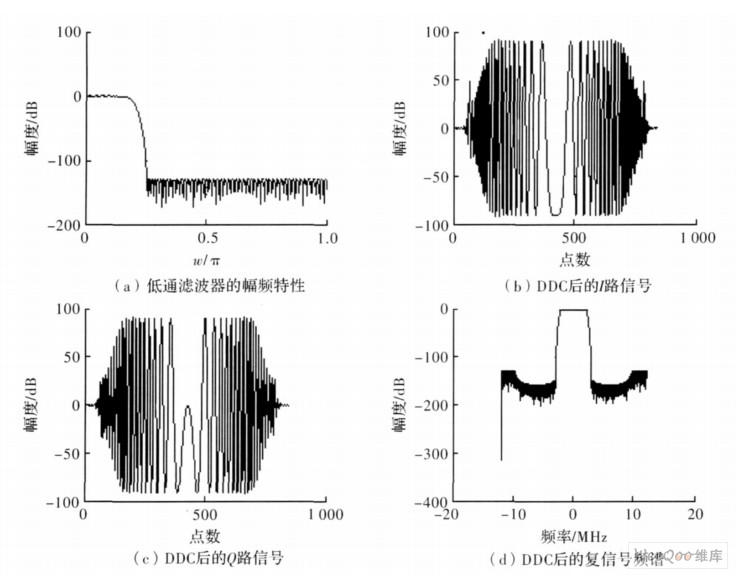

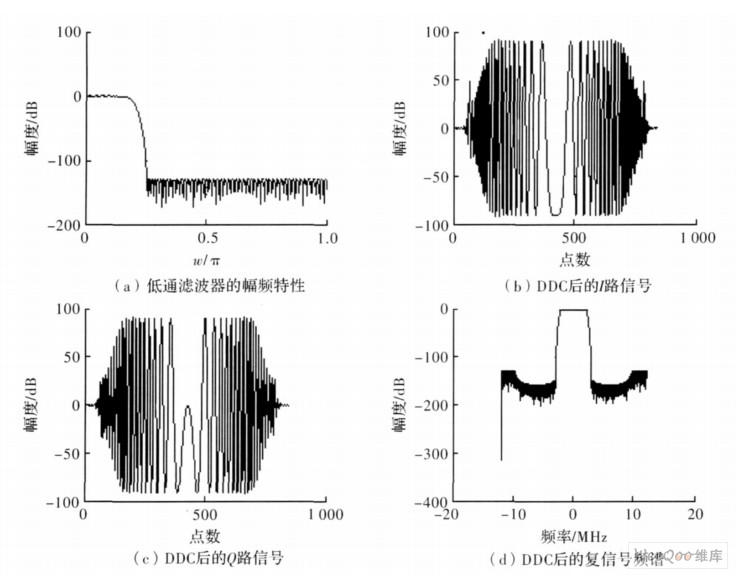

低通滤波法实现数字下变频中取 f 0 = 30MH z , 调频带宽 B = 5 MH z , 脉宽 T = 30us , 采样频率 fs =24MH z , 下面给出了一个脉冲重复周期的数字下变频及 2倍抽取后的仿真结果, 如图 4所示。

低通滤波法实现数字下变频中取 f 0 = 30MH z , 调频带宽 B = 5 MH z , 脉宽 T = 30us , 采样频率 fs =24MH z , 下面给出了一个脉冲重复周期的数字下变频及 2倍抽取后的仿真结果, 如图 4所示。

2、采用 System Generator实现数字下变频

2.1 数字下变频的设计

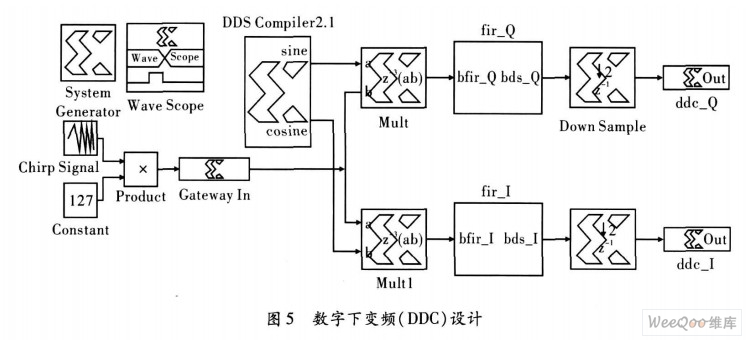

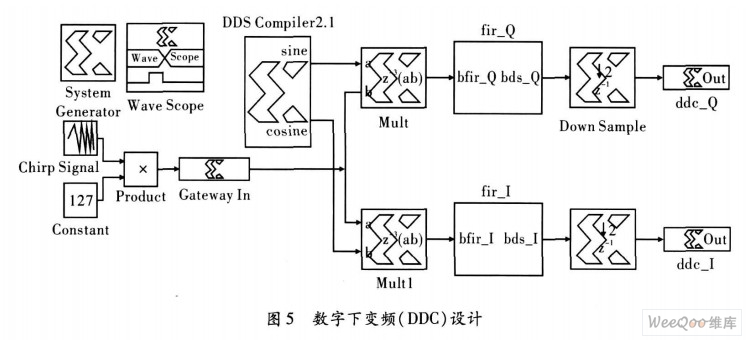

数字下变频低通滤波法原理图如图 5所示, 对一线性调频信号作正交解调, 信号参数为: 采样频率 f s =24MHz , 中频 f 0 = 30MHz , 带宽 B = 5MHz , 时宽 T =30 us , 抽取倍数D = 2。采用的滤波器为 127阶 FI R低通滤波器, 采用 Syste m Generator设计 DDC如图 5所示。

2、采用 System Generator实现数字下变频

2.1 数字下变频的设计

数字下变频低通滤波法原理图如图 5所示, 对一线性调频信号作正交解调, 信号参数为: 采样频率 f s =24MHz , 中频 f 0 = 30MHz , 带宽 B = 5MHz , 时宽 T =30 us , 抽取倍数D = 2。采用的滤波器为 127阶 FI R低通滤波器, 采用 Syste m Generator设计 DDC如图 5所示。

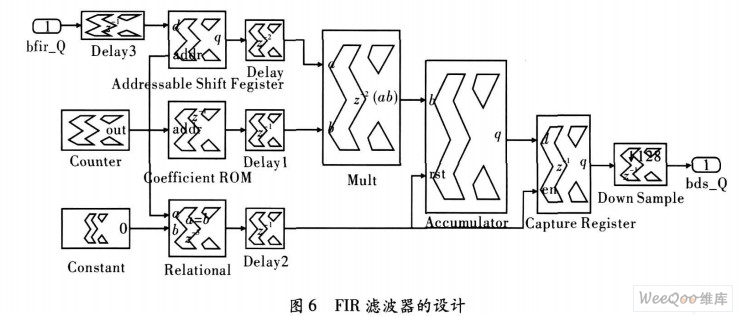

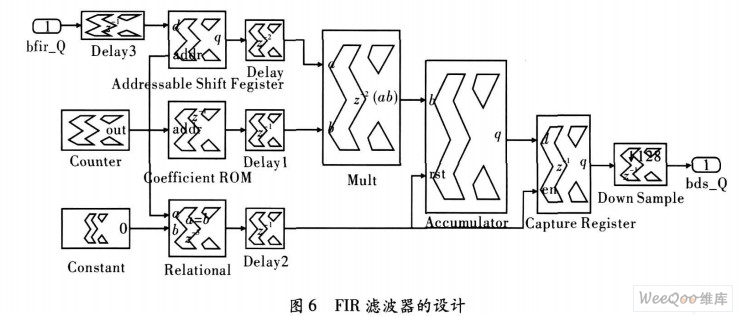

数字下变频( DDC)设计 FI R低通滤波器 fir_I及fir_ Q设计结构, 如图 6所示。

数字下变频( DDC)设计 FI R低通滤波器 fir_I及fir_ Q设计结构, 如图 6所示。

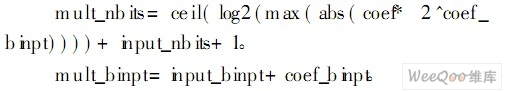

于乘累加的 FIR滤波器的模型化设计工作原理如下: 整个滤波器的各个子模块均 128倍于输入样本的速率。模计数器 Counter的输出作为 ASR和系数存储器模块 C oe f f icient Rom的地址输入, 分别取出样本x ( n- i)及滤波系数 ai进行乘法运算。在设计中, 为了提高运行的速度, 对样本及系数均插入了寄存器以达到流水线运行的目的。累加器模块 A ccumulato r实现对乘积项的累加, 当 Counter的输出变为 0时, 关系模块 Relat i ona l的输出为 1 , 使

MAC的输出 q保持为当前的累加结果, 同时 Capture Reg ister模块对输出q进行锁存。Down Sample模块 128分频采样 C aptureReg ister的输出以匹配输入样本的速率。Mult和A ccumulato r 模块中的数据位数定义必须依照以下格式来设定:

于乘累加的 FIR滤波器的模型化设计工作原理如下: 整个滤波器的各个子模块均 128倍于输入样本的速率。模计数器 Counter的输出作为 ASR和系数存储器模块 C oe f f icient Rom的地址输入, 分别取出样本x ( n- i)及滤波系数 ai进行乘法运算。在设计中, 为了提高运行的速度, 对样本及系数均插入了寄存器以达到流水线运行的目的。累加器模块 A ccumulato r实现对乘积项的累加, 当 Counter的输出变为 0时, 关系模块 Relat i ona l的输出为 1 , 使

MAC的输出 q保持为当前的累加结果, 同时 Capture Reg ister模块对输出q进行锁存。Down Sample模块 128分频采样 C aptureReg ister的输出以匹配输入样本的速率。Mult和A ccumulato r 模块中的数据位数定义必须依照以下格式来设定:

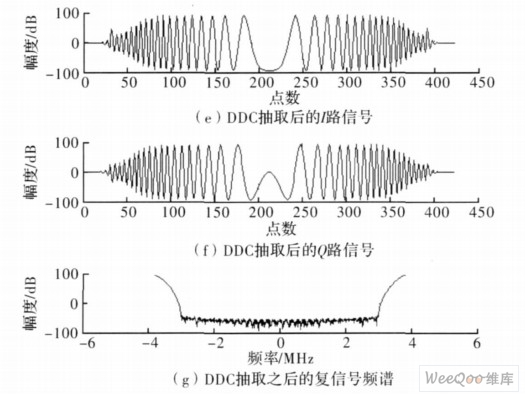

2.2仿真分析

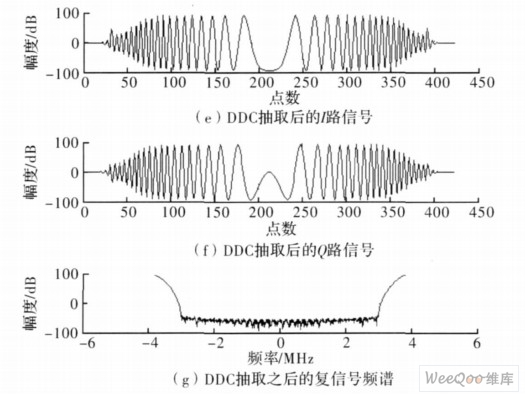

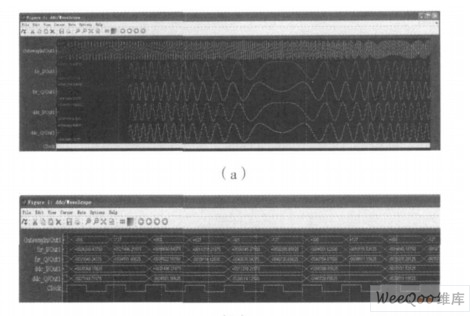

实现的数字下变频 System Generator 设计在Simulink /Matlab中进行了仿真, 输出波形如图 7所示。图 7( a), 图 7( b)中 fi r_I及 f i r_Q分别是抽取前后 DDC的 I、Q两路波形, 与图 4( a) , 图 4( b)的理论仿真进行对比, 发现波形一致

2.2仿真分析

实现的数字下变频 System Generator 设计在Simulink /Matlab中进行了仿真, 输出波形如图 7所示。图 7( a), 图 7( b)中 fi r_I及 f i r_Q分别是抽取前后 DDC的 I、Q两路波形, 与图 4( a) , 图 4( b)的理论仿真进行对比, 发现波形一致

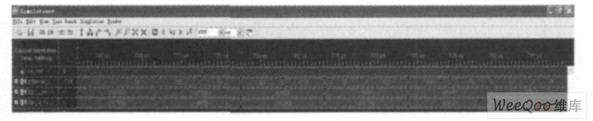

数字下变频 Syste m Generator设计通过了 S i mulink /Matlab仿真, 其结果也正确, 接下来就要生成HDL代码。在生成 HDL代码时, 同时会自动生成Testbenc h测试代码。这样便于浮点与定点的仿真,可以确保是在相同输入情况下进行对比, 而无需为仿真和实现建立不同的模型。在传统 RTL设计中, 验证代码的正确性是需要耗费很多时间和精力的, 因此这一功能不仅节省了人力同时也缩短了开发周期。下面给出具体在 X ili nx的集成开发环境 I SE 101下进行仿真综合结果,

其中输入为 Si mu li nk中模拟的雷达回波信号, 在生成 HDL代码时它自动产生测试代码时序仿真输出波形, 如图 8所示。表 1为 DDC 布局布线后占用资源情况和静态时序仿真报告。

数字下变频 Syste m Generator设计通过了 S i mulink /Matlab仿真, 其结果也正确, 接下来就要生成HDL代码。在生成 HDL代码时, 同时会自动生成Testbenc h测试代码。这样便于浮点与定点的仿真,可以确保是在相同输入情况下进行对比, 而无需为仿真和实现建立不同的模型。在传统 RTL设计中, 验证代码的正确性是需要耗费很多时间和精力的, 因此这一功能不仅节省了人力同时也缩短了开发周期。下面给出具体在 X ili nx的集成开发环境 I SE 101下进行仿真综合结果,

其中输入为 Si mu li nk中模拟的雷达回波信号, 在生成 HDL代码时它自动产生测试代码时序仿真输出波形, 如图 8所示。表 1为 DDC 布局布线后占用资源情况和静态时序仿真报告。

图 8 DDC在 ISE中的时序仿真波形

表 1 DDC布局布线后占用资源情况和静态时序报告

图 8 DDC在 ISE中的时序仿真波形

表 1 DDC布局布线后占用资源情况和静态时序报告

文中所选为 V i rtex5 系列的 xc5vsx95t封装为ff1136 , 速度为- 1 , 所对应的每个 Slice中包括有 4个触发器和 4个 6输入的 L UT , V i rtex5中有分布式RAM和 B lock RAM 两种, 而所选的这一芯片分别为1 520 kb和 8 784 kb。

3、结束语

此方法在设计仿真时图形化操作、简单易用, 对FPGA不熟悉的设计者仍可利用 Mat l ab软件和 X ili nx提供的工具, 进行基于 FPGA的数字信号处理系统开发。实现的算法能够确保与仿真结果相符, 而且无需为仿真和实现建立不同的模型, 在生成 HDL代码时会自动产生测试代码。若用传统的 FPGA 开发流程RTL设计数字下变频则需要编写大量代码, 然后将代码转换成具体的硬件来实现, 工作量大。因此, 这种方法不仅节省了开发时间, 同时由于 System Generator中的模块均是 X ili

nx公司用经过优化的 I P核集成的,在一定程度上也节省了资源

文中所选为 V i rtex5 系列的 xc5vsx95t封装为ff1136 , 速度为- 1 , 所对应的每个 Slice中包括有 4个触发器和 4个 6输入的 L UT , V i rtex5中有分布式RAM和 B lock RAM 两种, 而所选的这一芯片分别为1 520 kb和 8 784 kb。

3、结束语

此方法在设计仿真时图形化操作、简单易用, 对FPGA不熟悉的设计者仍可利用 Mat l ab软件和 X ili nx提供的工具, 进行基于 FPGA的数字信号处理系统开发。实现的算法能够确保与仿真结果相符, 而且无需为仿真和实现建立不同的模型, 在生成 HDL代码时会自动产生测试代码。若用传统的 FPGA 开发流程RTL设计数字下变频则需要编写大量代码, 然后将代码转换成具体的硬件来实现, 工作量大。因此, 这种方法不仅节省了开发时间, 同时由于 System Generator中的模块均是 X ili

nx公司用经过优化的 I P核集成的,在一定程度上也节省了资源

其中, Xi( t) = a(t)cosψ( t), XQ ( t ) = a ( t) sinψ(t)分别成为 x (t)的同相分量和正交分量;w0 为载频a (t), ψ(t)分别为包络和相位, 且有如下关系:

其中, Xi( t) = a(t)cosψ( t), XQ ( t ) = a ( t) sinψ(t)分别成为 x (t)的同相分量和正交分量;w0 为载频a (t), ψ(t)分别为包络和相位, 且有如下关系:

在雷达应用中, 输出信号可以表示为:

在雷达应用中, 输出信号可以表示为:

S~( t)称为信号的复包络。实信号 x ( t)的正负频谱是共轭对称的, 而其复包络 S~( t)就包含了 x ( t)中的所有信息 。

对复包络进行采样的传统方法是正交双通道采样, 如图 1所示。

S~( t)称为信号的复包络。实信号 x ( t)的正负频谱是共轭对称的, 而其复包络 S~( t)就包含了 x ( t)中的所有信息 。

对复包络进行采样的传统方法是正交双通道采样, 如图 1所示。

但是由于模拟电路存在漂移和不一致性, 使得到的两路信号并不是完全正交的, 而是存在一定的幅度和相位误差。直接中频采样与数字正交相干检波技术则可以较好地克服上述模拟方法存在的问题。中频直接采样实现正交相干检波的一般原理如图 2所示。

但是由于模拟电路存在漂移和不一致性, 使得到的两路信号并不是完全正交的, 而是存在一定的幅度和相位误差。直接中频采样与数字正交相干检波技术则可以较好地克服上述模拟方法存在的问题。中频直接采样实现正交相干检波的一般原理如图 2所示。

图 2数字中频正交采样

应用低通滤波法进行数字下变频的研究。低通滤波法是一种完全仿照传统模拟正交采样的实现方法, 只是将移频放在 A /D变换之后, 其原理框图如图 3所示。

图 2数字中频正交采样

应用低通滤波法进行数字下变频的研究。低通滤波法是一种完全仿照传统模拟正交采样的实现方法, 只是将移频放在 A /D变换之后, 其原理框图如图 3所示。

低通滤波法实现数字下变频中取 f 0 = 30MH z , 调频带宽 B = 5 MH z , 脉宽 T = 30us , 采样频率 fs =24MH z , 下面给出了一个脉冲重复周期的数字下变频及 2倍抽取后的仿真结果, 如图 4所示。

低通滤波法实现数字下变频中取 f 0 = 30MH z , 调频带宽 B = 5 MH z , 脉宽 T = 30us , 采样频率 fs =24MH z , 下面给出了一个脉冲重复周期的数字下变频及 2倍抽取后的仿真结果, 如图 4所示。

2、采用 System Generator实现数字下变频

2.1 数字下变频的设计

数字下变频低通滤波法原理图如图 5所示, 对一线性调频信号作正交解调, 信号参数为: 采样频率 f s =24MHz , 中频 f 0 = 30MHz , 带宽 B = 5MHz , 时宽 T =30 us , 抽取倍数D = 2。采用的滤波器为 127阶 FI R低通滤波器, 采用 Syste m Generator设计 DDC如图 5所示。

2、采用 System Generator实现数字下变频

2.1 数字下变频的设计

数字下变频低通滤波法原理图如图 5所示, 对一线性调频信号作正交解调, 信号参数为: 采样频率 f s =24MHz , 中频 f 0 = 30MHz , 带宽 B = 5MHz , 时宽 T =30 us , 抽取倍数D = 2。采用的滤波器为 127阶 FI R低通滤波器, 采用 Syste m Generator设计 DDC如图 5所示。

数字下变频( DDC)设计 FI R低通滤波器 fir_I及fir_ Q设计结构, 如图 6所示。

数字下变频( DDC)设计 FI R低通滤波器 fir_I及fir_ Q设计结构, 如图 6所示。

于乘累加的 FIR滤波器的模型化设计工作原理如下: 整个滤波器的各个子模块均 128倍于输入样本的速率。模计数器 Counter的输出作为 ASR和系数存储器模块 C oe f f icient Rom的地址输入, 分别取出样本x ( n- i)及滤波系数 ai进行乘法运算。在设计中, 为了提高运行的速度, 对样本及系数均插入了寄存器以达到流水线运行的目的。累加器模块 A ccumulato r实现对乘积项的累加, 当 Counter的输出变为 0时, 关系模块 Relat i ona l的输出为 1 , 使

MAC的输出 q保持为当前的累加结果, 同时 Capture Reg ister模块对输出q进行锁存。Down Sample模块 128分频采样 C aptureReg ister的输出以匹配输入样本的速率。Mult和A ccumulato r 模块中的数据位数定义必须依照以下格式来设定:

于乘累加的 FIR滤波器的模型化设计工作原理如下: 整个滤波器的各个子模块均 128倍于输入样本的速率。模计数器 Counter的输出作为 ASR和系数存储器模块 C oe f f icient Rom的地址输入, 分别取出样本x ( n- i)及滤波系数 ai进行乘法运算。在设计中, 为了提高运行的速度, 对样本及系数均插入了寄存器以达到流水线运行的目的。累加器模块 A ccumulato r实现对乘积项的累加, 当 Counter的输出变为 0时, 关系模块 Relat i ona l的输出为 1 , 使

MAC的输出 q保持为当前的累加结果, 同时 Capture Reg ister模块对输出q进行锁存。Down Sample模块 128分频采样 C aptureReg ister的输出以匹配输入样本的速率。Mult和A ccumulato r 模块中的数据位数定义必须依照以下格式来设定:

2.2仿真分析

实现的数字下变频 System Generator 设计在Simulink /Matlab中进行了仿真, 输出波形如图 7所示。图 7( a), 图 7( b)中 fi r_I及 f i r_Q分别是抽取前后 DDC的 I、Q两路波形, 与图 4( a) , 图 4( b)的理论仿真进行对比, 发现波形一致

2.2仿真分析

实现的数字下变频 System Generator 设计在Simulink /Matlab中进行了仿真, 输出波形如图 7所示。图 7( a), 图 7( b)中 fi r_I及 f i r_Q分别是抽取前后 DDC的 I、Q两路波形, 与图 4( a) , 图 4( b)的理论仿真进行对比, 发现波形一致

数字下变频 Syste m Generator设计通过了 S i mulink /Matlab仿真, 其结果也正确, 接下来就要生成HDL代码。在生成 HDL代码时, 同时会自动生成Testbenc h测试代码。这样便于浮点与定点的仿真,可以确保是在相同输入情况下进行对比, 而无需为仿真和实现建立不同的模型。在传统 RTL设计中, 验证代码的正确性是需要耗费很多时间和精力的, 因此这一功能不仅节省了人力同时也缩短了开发周期。下面给出具体在 X ili nx的集成开发环境 I SE 101下进行仿真综合结果,

其中输入为 Si mu li nk中模拟的雷达回波信号, 在生成 HDL代码时它自动产生测试代码时序仿真输出波形, 如图 8所示。表 1为 DDC 布局布线后占用资源情况和静态时序仿真报告。

数字下变频 Syste m Generator设计通过了 S i mulink /Matlab仿真, 其结果也正确, 接下来就要生成HDL代码。在生成 HDL代码时, 同时会自动生成Testbenc h测试代码。这样便于浮点与定点的仿真,可以确保是在相同输入情况下进行对比, 而无需为仿真和实现建立不同的模型。在传统 RTL设计中, 验证代码的正确性是需要耗费很多时间和精力的, 因此这一功能不仅节省了人力同时也缩短了开发周期。下面给出具体在 X ili nx的集成开发环境 I SE 101下进行仿真综合结果,

其中输入为 Si mu li nk中模拟的雷达回波信号, 在生成 HDL代码时它自动产生测试代码时序仿真输出波形, 如图 8所示。表 1为 DDC 布局布线后占用资源情况和静态时序仿真报告。

图 8 DDC在 ISE中的时序仿真波形

表 1 DDC布局布线后占用资源情况和静态时序报告

图 8 DDC在 ISE中的时序仿真波形

表 1 DDC布局布线后占用资源情况和静态时序报告

文中所选为 V i rtex5 系列的 xc5vsx95t封装为ff1136 , 速度为- 1 , 所对应的每个 Slice中包括有 4个触发器和 4个 6输入的 L UT , V i rtex5中有分布式RAM和 B lock RAM 两种, 而所选的这一芯片分别为1 520 kb和 8 784 kb。

3、结束语

此方法在设计仿真时图形化操作、简单易用, 对FPGA不熟悉的设计者仍可利用 Mat l ab软件和 X ili nx提供的工具, 进行基于 FPGA的数字信号处理系统开发。实现的算法能够确保与仿真结果相符, 而且无需为仿真和实现建立不同的模型, 在生成 HDL代码时会自动产生测试代码。若用传统的 FPGA 开发流程RTL设计数字下变频则需要编写大量代码, 然后将代码转换成具体的硬件来实现, 工作量大。因此, 这种方法不仅节省了开发时间, 同时由于 System Generator中的模块均是 X ili

nx公司用经过优化的 I P核集成的,在一定程度上也节省了资源

文中所选为 V i rtex5 系列的 xc5vsx95t封装为ff1136 , 速度为- 1 , 所对应的每个 Slice中包括有 4个触发器和 4个 6输入的 L UT , V i rtex5中有分布式RAM和 B lock RAM 两种, 而所选的这一芯片分别为1 520 kb和 8 784 kb。

3、结束语

此方法在设计仿真时图形化操作、简单易用, 对FPGA不熟悉的设计者仍可利用 Mat l ab软件和 X ili nx提供的工具, 进行基于 FPGA的数字信号处理系统开发。实现的算法能够确保与仿真结果相符, 而且无需为仿真和实现建立不同的模型, 在生成 HDL代码时会自动产生测试代码。若用传统的 FPGA 开发流程RTL设计数字下变频则需要编写大量代码, 然后将代码转换成具体的硬件来实现, 工作量大。因此, 这种方法不仅节省了开发时间, 同时由于 System Generator中的模块均是 X ili

nx公司用经过优化的 I P核集成的,在一定程度上也节省了资源