近期使用PLX公司的9052芯片通过DSP6713的HPI接口相连,参考了很多资料,有了自己的一点理解,和大家交流一下,理解有问题的还希望大家多多指正。

一、PCI空间地址到本地空间地址的地址映射 Example:一个1MB的可预取的本地地址空间0120 0000h~012F FFFFh被配置为本地地址空间0。假设上位机操作系统可以分配1MB的PCI空间,地址范围从3450 0000h到345F FFFFh。 具体配置如下: 1. 配置LAS0RR寄存器为——FFF0 0008h。

二、如何写本地空间地址的片选基地址寄存器 Example:一个16K的SRAM设备连到本地地址空间,一个片选需要被提供。基地址指定为24000h。 1. 将16进制的地址空间范围转换成 2的指数形式 例:16K=4000h或 214 位 2.设置片选X基寄存器的范围值, 设置第14位为1。 3. 基地址的设置方法:

3. 基地址的设置方法:

三、EEPROM的配置 1. Device ID设为5201h比较好。

四、9052驱动编程 1. 同样名字的驱动,在卸载时一定要选择删除原程序,否则即便改了程序,但如果加载的话,还是加载原来保存的驱动!!

五、官方SDK应用 1.添加库目录,Include和Shared。方法: 依次点击“项目——配置属性——C/C++——常规”,Project->Property->C/C++->General->Additional Include Directories在“附加包含目录”中加入H文件所在的文件夹 2.添加lib库,PlxApi.lib。方法: 依次点击“项目——配置属性——链接器——常规”,在“附加库目录”中加入LIB所在目录 Project->ProPerty->Link->General->Additional Include Directories 还没完,在“链接器”中找到“输入”,在“附加依赖项”中加入lua51.lib Input->Additional Dependencies或用#pragma comment(lib,"lua51.lib") 3.Debug和Release两个方式都要这样添加

六、上电RESET时LAD数据总线电平随机分配导致DSP配置引脚电平不对无法启动问题 调整DSP复位电路的电容,缩短DSP的复位时间,使DSP先于PCI9052完成复位即可。

七、PCI9052与DSP6713握手信号的研究 HCS#和HDS1#、HDS2#共同组成了HSTROBE#信号,其关系是:当HCS#为低电平,同时HDS1#和HDS2#有且仅有一个低电平时,HSTROBE#才是低电平。

在与DSP6713相连中,HDS1#——LRD#,HDS2#——LWR#,HCS#——LCS1#。即片选脚选中,且读和写有一个选中,HSTROBE#才选通。

HSTROBE#下降沿时可以锁存HHWIL、HR/W#、HCNTL[1:0]。上升沿时可以锁存数据。

HCS#和HDS1#、HDS2#共同组成了HSTROBE#信号,其关系是:当HCS#为低电平,同时HDS1#和HDS2#有且仅有一个低电平时,HSTROBE#才是低电平。

在与DSP6713相连中,HDS1#——LRD#,HDS2#——LWR#,HCS#——LCS1#。即片选脚选中,且读和写有一个选中,HSTROBE#才选通。

HSTROBE#下降沿时可以锁存HHWIL、HR/W#、HCNTL[1:0]。上升沿时可以锁存数据。

原理图可以参考:http://download.csdn.net/detail/sundonga/8269655,注意图中的逻辑芯片不要用CD系列,可以用速度高一些的74HC系列。

原理图可以参考:http://download.csdn.net/detail/sundonga/8269655,注意图中的逻辑芯片不要用CD系列,可以用速度高一些的74HC系列。

一、PCI空间地址到本地空间地址的地址映射 Example:一个1MB的可预取的本地地址空间0120 0000h~012F FFFFh被配置为本地地址空间0。假设上位机操作系统可以分配1MB的PCI空间,地址范围从3450 0000h到345F FFFFh。 具体配置如下: 1. 配置LAS0RR寄存器为——FFF0 0008h。

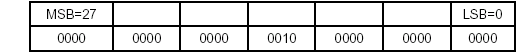

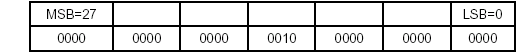

- 27:4:实际上是指定哪些地址位要进行PCI地址到本地地址的转换,即哪位要转换就把哪位置1。就是简单的指定了一下把哪些PCI空间的高位地址在映射时转换为本地空间的高位地址。

- 31:28位必须设为1,即这几位必须进行转换。

- LAS0RR[0]为0表示映射到PCI的存储器空间。

- LAS0RR[1:2]为00表示映射为32位的PCI地址空间。

- LAS0RR[3]为1表示映射为存储空间时是可预取的,映射为IO空间时加入到LAS0RR[27:4]中。

- LAS0BA[31:28]是保留位。

- LAS0BA[27:4]LAS0RR指定了哪些PCI位进行转换,这里给出本地空间地址要转换为什么。

- LAS0BA[3:2]如果映射为内存地址,这两位就没用。映射为IO地址,就加入到LAS0BA[27:4]中。

- LAS0BA[1]是保留位。

- LAS0BA[0]为1是使能PCI空间到本地空间的映射。

- PCIBAR2[31:4]到本地地址空间0的基地址

- PCIBAR2[3]如果是存储器空间相关的总线描述寄存器LAS0BRD控制地址空间的预取功能。如果是IO空间加入上面

- PCIBAR2[2:1]为00表示32位存储空间

- PCIBAR2[0]为0表示寄存器映射到存储空间,为1表示寄存器映射到IO空间,在LAS0RR中有指定。

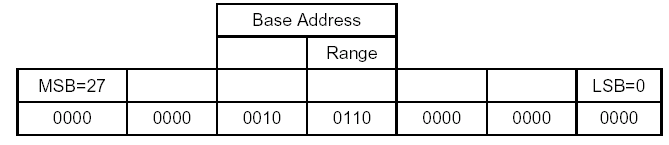

二、如何写本地空间地址的片选基地址寄存器 Example:一个16K的SRAM设备连到本地地址空间,一个片选需要被提供。基地址指定为24000h。 1. 将16进制的地址空间范围转换成 2的指数形式 例:16K=4000h或 214 位 2.设置片选X基寄存器的范围值, 设置第14位为1。

3. 基地址的设置方法:

3. 基地址的设置方法:

- 确定基地址(如24000h);

- 算出基地址为范围的倍数,用16进制进行计算;例: 24000h/4000h=9h

- 将倍值转换成2进制(例1001b);

- 将 倍值填在范围的设置位之后, 如范围的设置位为第14位,倍值为9h (1001b),则实际基寄存器设置如下:

三、EEPROM的配置 1. Device ID设为5201h比较好。

四、9052驱动编程 1. 同样名字的驱动,在卸载时一定要选择删除原程序,否则即便改了程序,但如果加载的话,还是加载原来保存的驱动!!

五、官方SDK应用 1.添加库目录,Include和Shared。方法: 依次点击“项目——配置属性——C/C++——常规”,Project->Property->C/C++->General->Additional Include Directories在“附加包含目录”中加入H文件所在的文件夹 2.添加lib库,PlxApi.lib。方法: 依次点击“项目——配置属性——链接器——常规”,在“附加库目录”中加入LIB所在目录 Project->ProPerty->Link->General->Additional Include Directories 还没完,在“链接器”中找到“输入”,在“附加依赖项”中加入lua51.lib Input->Additional Dependencies或用#pragma comment(lib,"lua51.lib") 3.Debug和Release两个方式都要这样添加

六、上电RESET时LAD数据总线电平随机分配导致DSP配置引脚电平不对无法启动问题 调整DSP复位电路的电容,缩短DSP的复位时间,使DSP先于PCI9052完成复位即可。

七、PCI9052与DSP6713握手信号的研究

- HAS#——地址锁存信号。在主机的地址数据是复用的时,HAS#接主机的ALE地址锁存引脚或其他类似功能的引脚。主机的地址数据是独立的时,HAS#上拉到高电平。NC板:拉高即可。

- HCS、HDS1和HDS2信号。

HCS#和HDS1#、HDS2#共同组成了HSTROBE#信号,其关系是:当HCS#为低电平,同时HDS1#和HDS2#有且仅有一个低电平时,HSTROBE#才是低电平。

在与DSP6713相连中,HDS1#——LRD#,HDS2#——LWR#,HCS#——LCS1#。即片选脚选中,且读和写有一个选中,HSTROBE#才选通。

HSTROBE#下降沿时可以锁存HHWIL、HR/W#、HCNTL[1:0]。上升沿时可以锁存数据。

HCS#和HDS1#、HDS2#共同组成了HSTROBE#信号,其关系是:当HCS#为低电平,同时HDS1#和HDS2#有且仅有一个低电平时,HSTROBE#才是低电平。

在与DSP6713相连中,HDS1#——LRD#,HDS2#——LWR#,HCS#——LCS1#。即片选脚选中,且读和写有一个选中,HSTROBE#才选通。

HSTROBE#下降沿时可以锁存HHWIL、HR/W#、HCNTL[1:0]。上升沿时可以锁存数据。

- LRDY#——本地总线准备好信号。该信号需要在LASxBRD寄存器中使能。

- LW/R#——指示数据传输的方向,因为PCI9052与DSP6713的极性正好相反,要接一个反向器。

原理图可以参考:http://download.csdn.net/detail/sundonga/8269655,注意图中的逻辑芯片不要用CD系列,可以用速度高一些的74HC系列。

原理图可以参考:http://download.csdn.net/detail/sundonga/8269655,注意图中的逻辑芯片不要用CD系列,可以用速度高一些的74HC系列。