6747的定时器配置如下:

1. 设置引脚复用寄存器PINMUX8,将3脚功能选择为定时器输出,注意,该脚与I2C0的SCL重合。

(用户手册P203)

2. 设置定时器setup_TIMER0();在setup_TIMER0函数中清除TIMER0的高32位计数器TIMER34和低32位计数器TIMER12,然后选择32位unchained模式,预分频系数为1,设置周期数寄存器为周期值

(用户手册P203)

2. 设置定时器setup_TIMER0();在setup_TIMER0函数中清除TIMER0的高32位计数器TIMER34和低32位计数器TIMER12,然后选择32位unchained模式,预分频系数为1,设置周期数寄存器为周期值

(用户手册P1235)

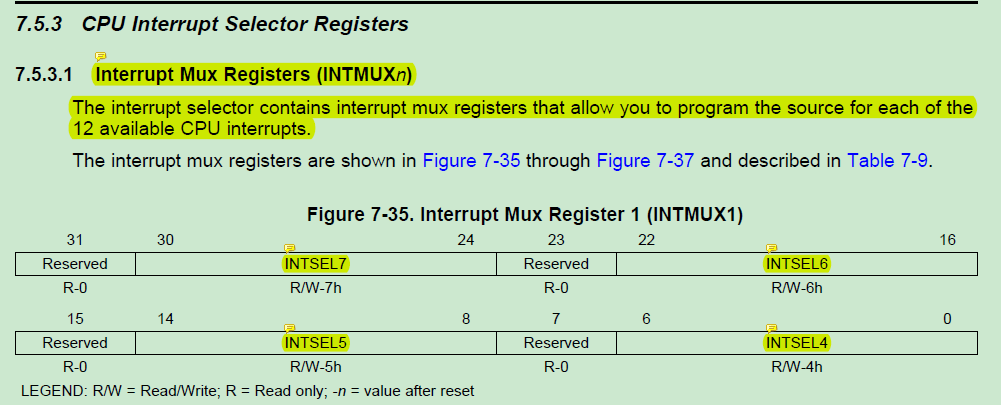

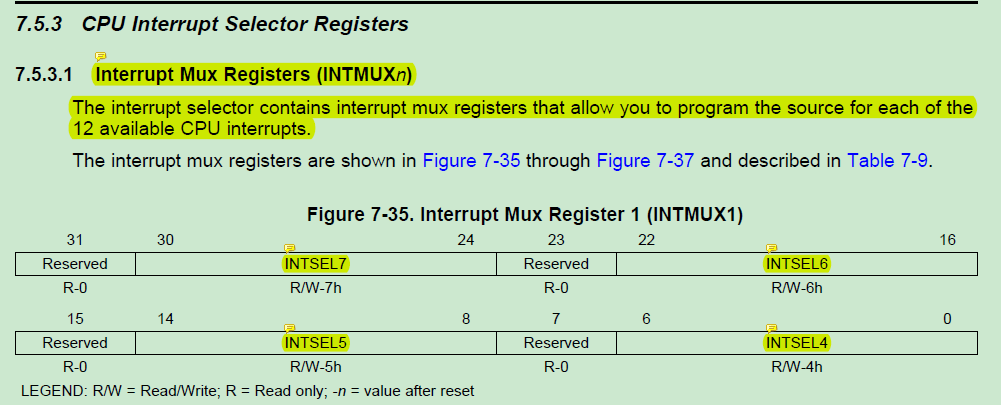

3. 在中断复用寄存器INTmux1中选择CPU级中断的中断源,将CPU中断的中断源设置为定时器

(用户手册P1235)

3. 在中断复用寄存器INTmux1中选择CPU级中断的中断源,将CPU中断的中断源设置为定时器

(用户手册P72)

(MegaModule手册P178) 4. 设置ISTP为中断向量表的地址,将ISTP指向中断向量表 5. 清除所有中断标志 6. 使能非可屏蔽中断位,打开中断总开关GIE位 7. 使能定时器0的12部分和34部分,选择连续模式,同时,如果不使用TIMER1,务必将TIMER1禁用掉 8. 编写中断服务子程序,至此,程序就能定时执行中断服务程序了。 注意:6747的64位定时器用作32位unchainedmode的时候,分成Timer12和Timer34两部分,不用的那部分,在初始化TIMER_TCR的时候,千万要关闭,不要打开,不然会对中断产生影响,具体原因是,打开了该部分,但是又没有相应的中断处理程序,当发生中断时得不到正确处理,结果会导致另外所用的那部分32位定时器发生第一次中断后就再也不能再进入中断程序了,这点千万注意,不用的TIMER部分千万不要打开!!! 附上定时器程序(注释部分代码是用RCSL库写的,可不用):

(用户手册P203)

2. 设置定时器setup_TIMER0();在setup_TIMER0函数中清除TIMER0的高32位计数器TIMER34和低32位计数器TIMER12,然后选择32位unchained模式,预分频系数为1,设置周期数寄存器为周期值

(用户手册P203)

2. 设置定时器setup_TIMER0();在setup_TIMER0函数中清除TIMER0的高32位计数器TIMER34和低32位计数器TIMER12,然后选择32位unchained模式,预分频系数为1,设置周期数寄存器为周期值

(用户手册P1235)

3. 在中断复用寄存器INTmux1中选择CPU级中断的中断源,将CPU中断的中断源设置为定时器

(用户手册P1235)

3. 在中断复用寄存器INTmux1中选择CPU级中断的中断源,将CPU中断的中断源设置为定时器

(用户手册P72)

(MegaModule手册P178) 4. 设置ISTP为中断向量表的地址,将ISTP指向中断向量表 5. 清除所有中断标志 6. 使能非可屏蔽中断位,打开中断总开关GIE位 7. 使能定时器0的12部分和34部分,选择连续模式,同时,如果不使用TIMER1,务必将TIMER1禁用掉 8. 编写中断服务子程序,至此,程序就能定时执行中断服务程序了。 注意:6747的64位定时器用作32位unchainedmode的时候,分成Timer12和Timer34两部分,不用的那部分,在初始化TIMER_TCR的时候,千万要关闭,不要打开,不然会对中断产生影响,具体原因是,打开了该部分,但是又没有相应的中断处理程序,当发生中断时得不到正确处理,结果会导致另外所用的那部分32位定时器发生第一次中断后就再也不能再进入中断程序了,这点千万注意,不用的TIMER部分千万不要打开!!! 附上定时器程序(注释部分代码是用RCSL库写的,可不用):

/*

* Core 6747 'led program.

* All by yanxu.

*/

#include "stdio.h"

#include "C6747.h"

//const unsigned int TIMER_PERIOD = 0x00001000;

const unsigned int TIMER_PERIOD = 0x00B71B00;

static void setup_TIMER0(void);

static void test_TIMERS(void);

void myExit(int);

void test_TIMERS(void);

void TIMER0_TINT12_isr();

static int TIMER0_TINT12_status = 1; // Pass/Fail flag

static int test_status = 1; // Test status

unsigned int k=0;

extern const unsigned int TIMER_PERIOD;

/*============================================================================*/

/* EXTERNAL FUNCTION PROTOTYPES */

/*============================================================================*/

extern void vectors(void);

void delay()

{

Uint32 i;

for(i=0;i<0x1fffff;i++);

}

void main( void )

{

/*初始化6747核*/

C6747_init();

PINMUX11=0X08888888;

PINMUX8=0x00040000;

GPIO_DIR23=0;//设置IO为输出,控制LED

//GPIO_DIR23=0xffffffff;

/* for(;;)

{GPIO_OUT_DATA23=0x800;//GPIO输出高电平

delay(); //延时

GPIO_OUT_DATA23=0x0;//GPIO输出低电平

delay(); //延时

}*/

/* Configure TIMER0, both halves to be used by application */

setup_TIMER0();

/* function to test the timer interrupts */

test_TIMERS();

/* for(;;)

{

GPIO_OUT_DATA23=0x800;//GPIO输出高电平

delay(); //延时

GPIO_OUT_DATA23=0x0;//GPIO输出低电平

delay(); //延时

}*/

while(1)

{

}

}

void setup_TIMER0 (void)

{

/* Clear TIM12 register */

// CSL_FINST(tmr0Regs->TIM12,TMR_TIM12_TIM12,RESETVAL);

TIMER0_TIM12=0x0;

/* Clear TIM34 register */

// CSL_FINST(tmr0Regs->TIM34,TMR_TIM34_TIM34,RESETVAL);

TIMER0_TIM34=0x0;

/* Select 32 bit unchained mode */

/* Take the timer out of reset and set the pre-scalar count for 3:4 */

/* tmr0Regs->TGCR = CSL_FMKT(TMR_TGCR_TIMMODE,32BIT_UNCHAIN)

| CSL_FMKT(TMR_TGCR_TIM12RS,NO_RESET)

| CSL_FMKT(TMR_TGCR_TIM34RS,NO_RESET)

| CSL_FMK(TMR_TGCR_PSC34,0x1);*/

TIMER0_TGCR=0x00000107;

/* Set timer0 PRD1:2 */

// CSL_FINS(tmr0Regs->PRD12,TMR_PRD12_PRD12,TIMER_PERIOD);

TIMER0_PRD12=TIMER_PERIOD;

/* Set timer0 PRD3:4 */

/* CSL_FINS(tmr0Regs->PRD34,TMR_PRD34_PRD34,TIMER_PERIOD);

TIMER0_PRD34=TIMER_PERIOD;*/

}

static void test_TIMERS(void)

{

/* Interrupt Controller Register Overlay */

printf("Testing TIMER0 and TIMER1 in unchained 32 bit mode.

");

printf("Starting TIMER0 3:4 side and TIMER1 1:2 and 3:4 sides.

");

/* connect the event to the interrupt 4,5,6 and 7 */

/* CSL_FINS(intcRegs->INTMUX1, INTC_INTMUX1_INTSEL4,TIMER_EVENT0);

CSL_FINS(intcRegs->INTMUX1, INTC_INTMUX1_INTSEL5,TIMER_EVENT1);

CSL_FINS(intcRegs->INTMUX1, INTC_INTMUX1_INTSEL6,TIMER_EVENT2);

CSL_FINS(intcRegs->INTMUX1, INTC_INTMUX1_INTSEL7,TIMER_EVENT3);*/

INTmux1=0x30284004;

/* set ISTP to point to the vector table address */

ISTP = (unsigned int)vectors;

/* clear all interrupts, bits 4 thru 15 */

ICR = 0xFFF0;

/* enable the bits for non maskable interrupt and */

IER = 0xF2;

/* enable interrupts, set GIE bit */

_enable_interrupts();

delay();

/* Enable TIMER0 1:2 side, one shot mode */

/* CSL_FINST(tmr0Regs->TCR,TMR_TCR_ENAMODE12,EN_ONCE);

TIMER0_TRC=0x00400040;*/

/* Enable TIMER0 1:2 side, continuous mode */

TIMER0_TRC=0x00000080;

/* Enable TIMER0 3:4 side, one shot mode */

/* CSL_FINST(tmr0Regs->TCR,TMR_TCR_ENAMODE34,EN_ONCE);*/

/* Enable TIMER1 1:2 side, one shot mode */

/* CSL_FINST(tmr1Regs->TCR,TMR_TCR_ENAMODE12,EN_ONCE);*/

TIMER1_TRC=0x00000000;

/* Enable TIMER1 3:4 side, one shot mode */

/* CSL_FINST(tmr1Regs->TCR,TMR_TCR_ENAMODE34,EN_ONCE);*/

/* Sleep for 3 system clock PRD's to ensure other timers have ran. *

* Since 3:4 sides are running at a divide by 2 PRD, we need to *

* sleep at least 2 PRDs. */

delay();

do

{

/* Check if interrupts occurred */

test_status = TIMER0_TINT12_status;

delay();

}while (test_status != 0);

/* Call exit function */

myExit(test_status);

}

interrupt void TIMER0_TINT12_isr()

{

/* Disable TIMER0 1:2 side */

/* CSL_FINST(tmr0Regs->TCR,TMR_TCR_ENAMODE12,DISABLE);

TIMER0_TRC=0x00000000;*/

/* Set flag to 0 indicating ISR occurred */

TIMER0_TINT12_status=0;

k=(k+1)%2;

if(k==0)

{

GPIO_OUT_DATA23=0x800;//GPIO输出高电平

}

else

{

GPIO_OUT_DATA23=0x0;//GPIO输出低电平

}

}

void myExit(int test_result)

{

/* Disable TIMER0 1:2 side */

/* CSL_FINST(tmr0Regs->TCR,TMR_TCR_ENAMODE12,DISABLE);

TIMER0_TRC=0x00000000;*/

/* Disable TIMER0 3:4 side */

/* CSL_FINST(tmr0Regs->TCR,TMR_TCR_ENAMODE34,DISABLE);*/

/* Disable TIMER1 1:2 side */

/* CSL_FINST(tmr1Regs->TCR,TMR_TCR_ENAMODE12,DISABLE);*/

/* TIMER1_TRC=0x00000000;*/

/* Disable TIMER1 3:4 side */

/* CSL_FINST(tmr1Regs->TCR,TMR_TCR_ENAMODE34,DISABLE);*/

/* Turn off all interrupts */

/* _disable_interrupts();*/

/* Display test status */

if (test_result == 0)

{

printf("Timer0 and Timer1 interrupt test: PASSED.

");

}

else

{

printf("Timer0 and Timer1 interrupt test: FAILED.

");

}

}