rev 0.1

快乐虾

http://blog.csdn.net/lights_joy/

lights@hb165.com

本文适用于

ADI bf561 DSP

优视BF561EVB开发板

uclinux-2008r1-rc8 (移植到vdsp5)

Visual DSP++ 5.0

欢迎转载,但请保留作者信息

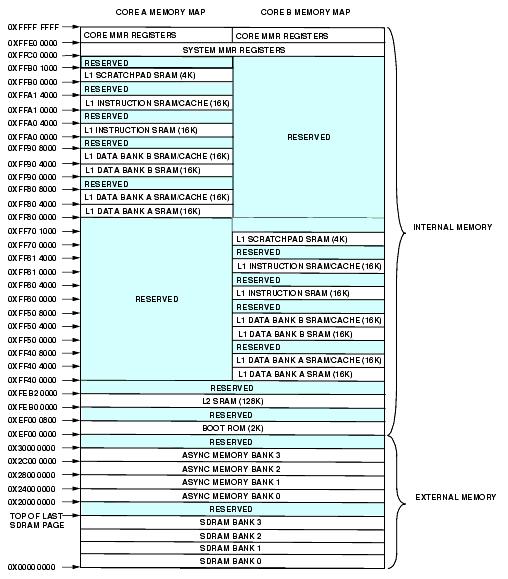

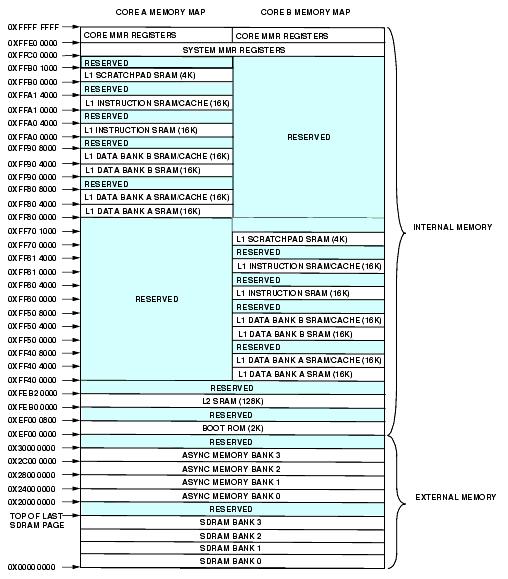

在BF561中,它的整个存储空间是这样的:

cplb_data这个全局变量的定义在arch/blackfin/kernel/cplb-nommu/cplb_init.c文件中,从这个全局变量可以看出内核对整个存储区域的划分。

static struct cplb_desc cplb_data[] = {

{

.start = 0,

.end = SIZE_1K,

.psize = SIZE_1K,

.attr = INITIAL_T | SWITCH_T | I_CPLB | D_CPLB,

.i_conf = SDRAM_OOPS,

.d_conf = SDRAM_OOPS,

#if defined(CONFIG_DEBUG_HUNT_FOR_ZERO)

.valid = 1,

#else

.valid = 0,

#endif

.name = "Zero Pointer Guard Page",

},

{

.start = 0, /* dyanmic */

.end = 0, /* dynamic */

.psize = SIZE_4M,

.attr = INITIAL_T | SWITCH_T | I_CPLB,

.i_conf = L1_IMEMORY,

.d_conf = 0,

.valid = 1,

.name = "L1 I-Memory",

},

{

.start = 0, /* dynamic */

.end = 0, /* dynamic */

.psize = SIZE_4M,

.attr = INITIAL_T | SWITCH_T | D_CPLB,

.i_conf = 0,

.d_conf = L1_DMEMORY,

#if ((L1_DATA_A_LENGTH > 0) || (L1_DATA_B_LENGTH > 0))

.valid = 1,

#else

.valid = 0,

#endif

.name = "L1 D-Memory",

},

{

#if defined(CONFIG_BF561) || defined(CONFIG_BF54x)

.start = L2_START,

.end = L2_START+L2_LENGTH,

.psize = SIZE_1M,

.attr = L2_ATTR,

.i_conf = L2_MEMORY,

.d_conf = L2_MEMORY,

.valid = 1,

#else

.valid = 0,

#endif

.name = "L2 Memory",

},

{

.start = 0,

.end = 0, /* dynamic */

.psize = 0,

.attr = INITIAL_T | SWITCH_T | I_CPLB | D_CPLB,

.i_conf = SDRAM_IGENERIC,

.d_conf = SDRAM_DGENERIC,

.valid = 1,

.name = "Kernel Memory",

},

{

.start = 0, /* dynamic */

.end = 0, /* dynamic */

.psize = 0,

.attr = INITIAL_T | SWITCH_T | D_CPLB,

.i_conf = SDRAM_IGENERIC,

.d_conf = SDRAM_DNON_CHBL,

.valid = 1,

.name = "uClinux MTD Memory",

},

{

.start = 0, /* dynamic */

.end = 0, /* dynamic */

.psize = SIZE_1M,

.attr = INITIAL_T | SWITCH_T | D_CPLB,

.d_conf = SDRAM_DNON_CHBL,

.valid = 1,

.name = "Uncached DMA Zone",

},

{

.start = 0, /* dynamic */

.end = 0, /* dynamic */

.psize = 0,

.attr = SWITCH_T | D_CPLB,

.i_conf = 0, /* dynamic */

.d_conf = 0, /* dynamic */

.valid = 1,

.name = "Reserved Memory",

},

{

.start = ASYNC_BANK0_BASE,

.end = ASYNC_BANK3_BASE + ASYNC_BANK3_SIZE,

.psize = 0,

.attr = SWITCH_T | D_CPLB,

.d_conf = SDRAM_EBIU,

.valid = 1,

.name = "Asynchronous Memory Banks",

},

{

.start = BOOT_ROM_START,

.end = BOOT_ROM_START + BOOT_ROM_LENGTH,

.psize = SIZE_1M,

.attr = SWITCH_T | I_CPLB | D_CPLB,

.i_conf = SDRAM_IGENERIC,

.d_conf = SDRAM_DGENERIC,

.valid = 1,

.name = "On-Chip BootROM",

},

};

从上面可以看出,内核将整个存储空间分为10个区域,每个区域的序号可以用下面的宏来表示。

enum {

ZERO_P, L1I_MEM, L1D_MEM, L2_MEM, SDRAM_KERN, SDRAM_RAM_MTD, SDRAM_DMAZ, RES_MEM, ASYNC_MEM, OCB_ROM

};

cplb_data这个全局变量的定义在arch/blackfin/kernel/cplb-nommu/cplb_init.c文件中,从这个全局变量可以看出内核对整个存储区域的划分。

static struct cplb_desc cplb_data[] = {

{

.start = 0,

.end = SIZE_1K,

.psize = SIZE_1K,

.attr = INITIAL_T | SWITCH_T | I_CPLB | D_CPLB,

.i_conf = SDRAM_OOPS,

.d_conf = SDRAM_OOPS,

#if defined(CONFIG_DEBUG_HUNT_FOR_ZERO)

.valid = 1,

#else

.valid = 0,

#endif

.name = "Zero Pointer Guard Page",

},

{

.start = 0, /* dyanmic */

.end = 0, /* dynamic */

.psize = SIZE_4M,

.attr = INITIAL_T | SWITCH_T | I_CPLB,

.i_conf = L1_IMEMORY,

.d_conf = 0,

.valid = 1,

.name = "L1 I-Memory",

},

{

.start = 0, /* dynamic */

.end = 0, /* dynamic */

.psize = SIZE_4M,

.attr = INITIAL_T | SWITCH_T | D_CPLB,

.i_conf = 0,

.d_conf = L1_DMEMORY,

#if ((L1_DATA_A_LENGTH > 0) || (L1_DATA_B_LENGTH > 0))

.valid = 1,

#else

.valid = 0,

#endif

.name = "L1 D-Memory",

},

{

#if defined(CONFIG_BF561) || defined(CONFIG_BF54x)

.start = L2_START,

.end = L2_START+L2_LENGTH,

.psize = SIZE_1M,

.attr = L2_ATTR,

.i_conf = L2_MEMORY,

.d_conf = L2_MEMORY,

.valid = 1,

#else

.valid = 0,

#endif

.name = "L2 Memory",

},

{

.start = 0,

.end = 0, /* dynamic */

.psize = 0,

.attr = INITIAL_T | SWITCH_T | I_CPLB | D_CPLB,

.i_conf = SDRAM_IGENERIC,

.d_conf = SDRAM_DGENERIC,

.valid = 1,

.name = "Kernel Memory",

},

{

.start = 0, /* dynamic */

.end = 0, /* dynamic */

.psize = 0,

.attr = INITIAL_T | SWITCH_T | D_CPLB,

.i_conf = SDRAM_IGENERIC,

.d_conf = SDRAM_DNON_CHBL,

.valid = 1,

.name = "uClinux MTD Memory",

},

{

.start = 0, /* dynamic */

.end = 0, /* dynamic */

.psize = SIZE_1M,

.attr = INITIAL_T | SWITCH_T | D_CPLB,

.d_conf = SDRAM_DNON_CHBL,

.valid = 1,

.name = "Uncached DMA Zone",

},

{

.start = 0, /* dynamic */

.end = 0, /* dynamic */

.psize = 0,

.attr = SWITCH_T | D_CPLB,

.i_conf = 0, /* dynamic */

.d_conf = 0, /* dynamic */

.valid = 1,

.name = "Reserved Memory",

},

{

.start = ASYNC_BANK0_BASE,

.end = ASYNC_BANK3_BASE + ASYNC_BANK3_SIZE,

.psize = 0,

.attr = SWITCH_T | D_CPLB,

.d_conf = SDRAM_EBIU,

.valid = 1,

.name = "Asynchronous Memory Banks",

},

{

.start = BOOT_ROM_START,

.end = BOOT_ROM_START + BOOT_ROM_LENGTH,

.psize = SIZE_1M,

.attr = SWITCH_T | I_CPLB | D_CPLB,

.i_conf = SDRAM_IGENERIC,

.d_conf = SDRAM_DGENERIC,

.valid = 1,

.name = "On-Chip BootROM",

},

};

从上面可以看出,内核将整个存储空间分为10个区域,每个区域的序号可以用下面的宏来表示。

enum {

ZERO_P, L1I_MEM, L1D_MEM, L2_MEM, SDRAM_KERN, SDRAM_RAM_MTD, SDRAM_DMAZ, RES_MEM, ASYNC_MEM, OCB_ROM

};

cplb_data这个全局变量的定义在arch/blackfin/kernel/cplb-nommu/cplb_init.c文件中,从这个全局变量可以看出内核对整个存储区域的划分。

static struct cplb_desc cplb_data[] = {

{

.start = 0,

.end = SIZE_1K,

.psize = SIZE_1K,

.attr = INITIAL_T | SWITCH_T | I_CPLB | D_CPLB,

.i_conf = SDRAM_OOPS,

.d_conf = SDRAM_OOPS,

#if defined(CONFIG_DEBUG_HUNT_FOR_ZERO)

.valid = 1,

#else

.valid = 0,

#endif

.name = "Zero Pointer Guard Page",

},

{

.start = 0, /* dyanmic */

.end = 0, /* dynamic */

.psize = SIZE_4M,

.attr = INITIAL_T | SWITCH_T | I_CPLB,

.i_conf = L1_IMEMORY,

.d_conf = 0,

.valid = 1,

.name = "L1 I-Memory",

},

{

.start = 0, /* dynamic */

.end = 0, /* dynamic */

.psize = SIZE_4M,

.attr = INITIAL_T | SWITCH_T | D_CPLB,

.i_conf = 0,

.d_conf = L1_DMEMORY,

#if ((L1_DATA_A_LENGTH > 0) || (L1_DATA_B_LENGTH > 0))

.valid = 1,

#else

.valid = 0,

#endif

.name = "L1 D-Memory",

},

{

#if defined(CONFIG_BF561) || defined(CONFIG_BF54x)

.start = L2_START,

.end = L2_START+L2_LENGTH,

.psize = SIZE_1M,

.attr = L2_ATTR,

.i_conf = L2_MEMORY,

.d_conf = L2_MEMORY,

.valid = 1,

#else

.valid = 0,

#endif

.name = "L2 Memory",

},

{

.start = 0,

.end = 0, /* dynamic */

.psize = 0,

.attr = INITIAL_T | SWITCH_T | I_CPLB | D_CPLB,

.i_conf = SDRAM_IGENERIC,

.d_conf = SDRAM_DGENERIC,

.valid = 1,

.name = "Kernel Memory",

},

{

.start = 0, /* dynamic */

.end = 0, /* dynamic */

.psize = 0,

.attr = INITIAL_T | SWITCH_T | D_CPLB,

.i_conf = SDRAM_IGENERIC,

.d_conf = SDRAM_DNON_CHBL,

.valid = 1,

.name = "uClinux MTD Memory",

},

{

.start = 0, /* dynamic */

.end = 0, /* dynamic */

.psize = SIZE_1M,

.attr = INITIAL_T | SWITCH_T | D_CPLB,

.d_conf = SDRAM_DNON_CHBL,

.valid = 1,

.name = "Uncached DMA Zone",

},

{

.start = 0, /* dynamic */

.end = 0, /* dynamic */

.psize = 0,

.attr = SWITCH_T | D_CPLB,

.i_conf = 0, /* dynamic */

.d_conf = 0, /* dynamic */

.valid = 1,

.name = "Reserved Memory",

},

{

.start = ASYNC_BANK0_BASE,

.end = ASYNC_BANK3_BASE + ASYNC_BANK3_SIZE,

.psize = 0,

.attr = SWITCH_T | D_CPLB,

.d_conf = SDRAM_EBIU,

.valid = 1,

.name = "Asynchronous Memory Banks",

},

{

.start = BOOT_ROM_START,

.end = BOOT_ROM_START + BOOT_ROM_LENGTH,

.psize = SIZE_1M,

.attr = SWITCH_T | I_CPLB | D_CPLB,

.i_conf = SDRAM_IGENERIC,

.d_conf = SDRAM_DGENERIC,

.valid = 1,

.name = "On-Chip BootROM",

},

};

从上面可以看出,内核将整个存储空间分为10个区域,每个区域的序号可以用下面的宏来表示。

enum {

ZERO_P, L1I_MEM, L1D_MEM, L2_MEM, SDRAM_KERN, SDRAM_RAM_MTD, SDRAM_DMAZ, RES_MEM, ASYNC_MEM, OCB_ROM

};

cplb_data这个全局变量的定义在arch/blackfin/kernel/cplb-nommu/cplb_init.c文件中,从这个全局变量可以看出内核对整个存储区域的划分。

static struct cplb_desc cplb_data[] = {

{

.start = 0,

.end = SIZE_1K,

.psize = SIZE_1K,

.attr = INITIAL_T | SWITCH_T | I_CPLB | D_CPLB,

.i_conf = SDRAM_OOPS,

.d_conf = SDRAM_OOPS,

#if defined(CONFIG_DEBUG_HUNT_FOR_ZERO)

.valid = 1,

#else

.valid = 0,

#endif

.name = "Zero Pointer Guard Page",

},

{

.start = 0, /* dyanmic */

.end = 0, /* dynamic */

.psize = SIZE_4M,

.attr = INITIAL_T | SWITCH_T | I_CPLB,

.i_conf = L1_IMEMORY,

.d_conf = 0,

.valid = 1,

.name = "L1 I-Memory",

},

{

.start = 0, /* dynamic */

.end = 0, /* dynamic */

.psize = SIZE_4M,

.attr = INITIAL_T | SWITCH_T | D_CPLB,

.i_conf = 0,

.d_conf = L1_DMEMORY,

#if ((L1_DATA_A_LENGTH > 0) || (L1_DATA_B_LENGTH > 0))

.valid = 1,

#else

.valid = 0,

#endif

.name = "L1 D-Memory",

},

{

#if defined(CONFIG_BF561) || defined(CONFIG_BF54x)

.start = L2_START,

.end = L2_START+L2_LENGTH,

.psize = SIZE_1M,

.attr = L2_ATTR,

.i_conf = L2_MEMORY,

.d_conf = L2_MEMORY,

.valid = 1,

#else

.valid = 0,

#endif

.name = "L2 Memory",

},

{

.start = 0,

.end = 0, /* dynamic */

.psize = 0,

.attr = INITIAL_T | SWITCH_T | I_CPLB | D_CPLB,

.i_conf = SDRAM_IGENERIC,

.d_conf = SDRAM_DGENERIC,

.valid = 1,

.name = "Kernel Memory",

},

{

.start = 0, /* dynamic */

.end = 0, /* dynamic */

.psize = 0,

.attr = INITIAL_T | SWITCH_T | D_CPLB,

.i_conf = SDRAM_IGENERIC,

.d_conf = SDRAM_DNON_CHBL,

.valid = 1,

.name = "uClinux MTD Memory",

},

{

.start = 0, /* dynamic */

.end = 0, /* dynamic */

.psize = SIZE_1M,

.attr = INITIAL_T | SWITCH_T | D_CPLB,

.d_conf = SDRAM_DNON_CHBL,

.valid = 1,

.name = "Uncached DMA Zone",

},

{

.start = 0, /* dynamic */

.end = 0, /* dynamic */

.psize = 0,

.attr = SWITCH_T | D_CPLB,

.i_conf = 0, /* dynamic */

.d_conf = 0, /* dynamic */

.valid = 1,

.name = "Reserved Memory",

},

{

.start = ASYNC_BANK0_BASE,

.end = ASYNC_BANK3_BASE + ASYNC_BANK3_SIZE,

.psize = 0,

.attr = SWITCH_T | D_CPLB,

.d_conf = SDRAM_EBIU,

.valid = 1,

.name = "Asynchronous Memory Banks",

},

{

.start = BOOT_ROM_START,

.end = BOOT_ROM_START + BOOT_ROM_LENGTH,

.psize = SIZE_1M,

.attr = SWITCH_T | I_CPLB | D_CPLB,

.i_conf = SDRAM_IGENERIC,

.d_conf = SDRAM_DGENERIC,

.valid = 1,

.name = "On-Chip BootROM",

},

};

从上面可以看出,内核将整个存储空间分为10个区域,每个区域的序号可以用下面的宏来表示。

enum {

ZERO_P, L1I_MEM, L1D_MEM, L2_MEM, SDRAM_KERN, SDRAM_RAM_MTD, SDRAM_DMAZ, RES_MEM, ASYNC_MEM, OCB_ROM

};