第一部分:

High-level Synthesis Vendors

来自:https://blog.csdn.net/changan2001/article/details/5625316 PICO from SynforaAutoPilot from AutoESL

C-to-Silicon from Cadence Design Systems

Synphony HLS from Synopsys

PowerOpt from ChipVision

Cynthesizer from Forte Design Systems

Catapult C from Mentor Graphics

CyberWorkBench from NEC

C-to-Verilog from C-to-Verilog.com

C2R from CebaTech

CoDeveloper from Impulse Accelerated Technologies

eXCite from Y Explorations

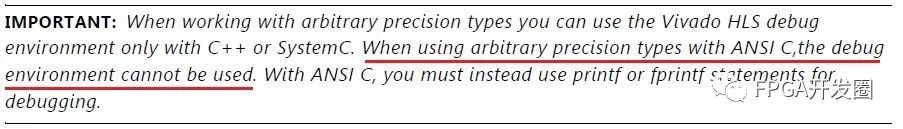

Synfora发展了这么多年,工具做的不错,是AutoESL的主要竞争对手。 AutoESL绝对是后起之秀,并且有长江后浪推前浪,一代更比一代强的趋势。能够做到比手写RTL 的QoR更好的效果绝不是浪得虚名。 Catapult C是江湖元老,各方面比较成熟,但是价格也不菲啊,在国内这种处处都是廉价劳动力的环境下,很难赢得企业的青睐。这也是其他所有HLS工具面临的挑战。 Forte在SystemC方面是老大,发展很早,但是不支持C/C++,受到很大的局限。 其他几个工具不说也罢,表现平平。 来自:http://www.sohu.com/a/216404161_505803 第二部分 用好Vivado HLS ,这三大误区要避免! 目前,在高层次综合(HLS, High Level Synthesis)领域,Vivado HLS可谓独树一帜。它有效地拉近了软件工程师与FPGA之间的距离,加速了算法开发的进程,缩短了产品上市时间。对于工程师,尤其是软件工程师而言是一个福音。在实际工程中,如何利用好这一工具仍值得考究。本文将介绍使用Vivado HLS时的几个误区。 误区1 只要是C或者C++描述的算法都是可综合(可转换成RTL)的。 HLS的可综合功能是有限的,并不是所有的C或者C++语句都可转换成相应的RTL代码。下面这些情形是不可综合的。 1. 动态内存分配 2. 涉及操作系统层面的操作 3. 递归函数 4. 数组规模可变 误区2 既然Vivado HLS支持C、C++和System C,那么用三者任意一种都行。 尽管 Vivado HLS支持C、C++和System C,但支持力度是不一样的。在v2017.4版本ug871 第56页有如下描述。可见,当设计中如果使用到任意精度的数据类型时,采用C++ 和System C 是可以使用Vivado HLS的调试环境的,但是C 描述的算法却是不可以的。而实际上很多真实的硬件模型都要使用任意进度的数据类型,所以要想使用Vivado HLS 的调试功能, 建议最好采用 C++和System

误区3

只要有源代码即可,没有Test bench也行。

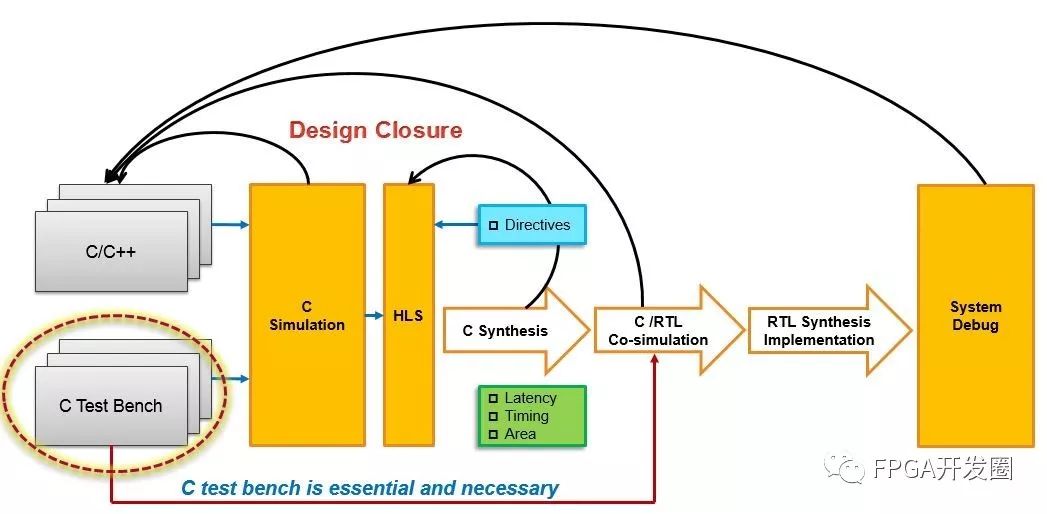

在HLS设计开发中,C Test bench起着举足轻重的作用。C层面算法功能的验证需要用到它;当生成RTL代码时,C和RTL的协同仿真也要用到它。如下图所示。实际上,协同仿真时,RTL代码的输入激励就是由C Test bench生成的。由此可见,C Test bench是整个设计不可或缺的一部分。

误区3

只要有源代码即可,没有Test bench也行。

在HLS设计开发中,C Test bench起着举足轻重的作用。C层面算法功能的验证需要用到它;当生成RTL代码时,C和RTL的协同仿真也要用到它。如下图所示。实际上,协同仿真时,RTL代码的输入激励就是由C Test bench生成的。由此可见,C Test bench是整个设计不可或缺的一部分。