更多精彩内容,请微信搜索“FPGAer俱乐部”关注我们。首先,先来科普一下,什么是CORDIC:CORDIC(Coordinate Rotation Digital Computer)算法即坐标旋转数字计算方法,是J.D.Volder1于1959年首次提出,主要用于三角函数、双曲线、指数、对数的计算。该算法通过基本的加和移位运算代替乘法运算,使得矢量的旋转和定向的计算不再需要三角函数、乘法、开方、反三角、指数等函数。各大FPGA厂商都提供了相关的CORDIC的Soft IP(详见本文最后的,主要参考资料部分),其中,Lattice和Altera提供的IP在功能和使用上都比较类似,主要提供了如下四种功能: CORDIC的思想是,将旋转theta度,拆分为多个步骤,依次迭代进行。其中,某一个步骤的计算等式如下:

CORDIC的思想是,将旋转theta度,拆分为多个步骤,依次迭代进行。其中,某一个步骤的计算等式如下:

这里的theta i的取值是有讲究的,需要满足如下等式:

这里的theta i的取值是有讲究的,需要满足如下等式:

上式中,i为正整数,i的最大值就是迭代的次数。显然i的最大值越大,计算得到的结果将越精确。但是在实际的情况下,i不可能取无穷大的,一般取16左右,就能得到较为精确的值了(取16时,大约可以精确到小数点后3-4位,Lattice的IP最高可以取值为32)。此时,显然有:

上式中,i为正整数,i的最大值就是迭代的次数。显然i的最大值越大,计算得到的结果将越精确。但是在实际的情况下,i不可能取无穷大的,一般取16左右,就能得到较为精确的值了(取16时,大约可以精确到小数点后3-4位,Lattice的IP最高可以取值为32)。此时,显然有:

将cos theta表示为Ki,则有:

将cos theta表示为Ki,则有:

需要注意的是,关于Ki的值,Lattice与Xilinx并未明确指出,而Altera则取的是一个定值(常量),值为1.6467602……。个人觉得应该处理方法是相似的,具体可以看:http://blog.chinaaet.com/justlxy/p/5100052282实际上,无论是哪一家都可以通过IP配置时的scale factor compensation选项进行自动消除K值的影响。上面的介绍可能不太直观,下面再来看一个网友提供的更为直观的栗子,以加深理解:

需要注意的是,关于Ki的值,Lattice与Xilinx并未明确指出,而Altera则取的是一个定值(常量),值为1.6467602……。个人觉得应该处理方法是相似的,具体可以看:http://blog.chinaaet.com/justlxy/p/5100052282实际上,无论是哪一家都可以通过IP配置时的scale factor compensation选项进行自动消除K值的影响。上面的介绍可能不太直观,下面再来看一个网友提供的更为直观的栗子,以加深理解: 即,如果需要计算cos45°或者sin45°,则需要进行N次迭代,每次theta的取值如图中黄 {MOD}部分所示。二、Lattice的CORDIC IP使用说明

即,如果需要计算cos45°或者sin45°,则需要进行N次迭代,每次theta的取值如图中黄 {MOD}部分所示。二、Lattice的CORDIC IP使用说明

下面来聊一聊Lattice的CORDIC的IP的四个模式的基本使用方法和注意事项。首先看一下,CORDIC的结构框图: 下面依次介绍一下各个模块的作用:

下面依次介绍一下各个模块的作用:

其中CORDIC Arithmetic Unit的基本结构图为: 接下来接着介绍,前面说提到的四种功能:

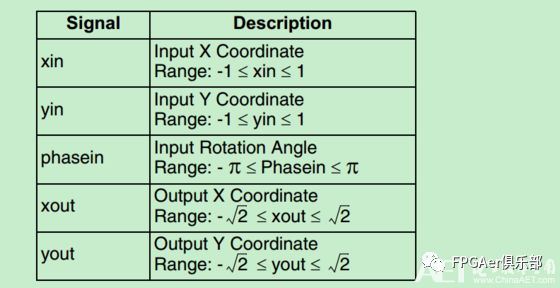

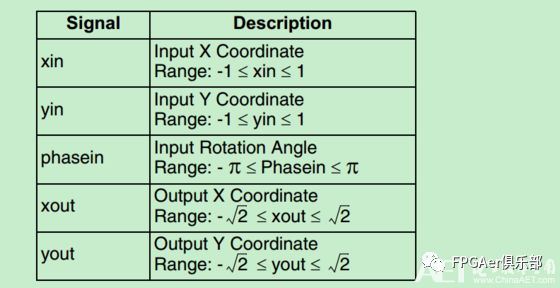

接下来接着介绍,前面说提到的四种功能: 信号描述如下图所示:

信号描述如下图所示:

xin和yin为输入,即(x,y),xout和yout为输出,即(x0,y0)。V0的模中的K可以通过前面介绍的方法来消除。

xin和yin为输入,即(x,y),xout和yout为输出,即(x0,y0)。V0的模中的K可以通过前面介绍的方法来消除。

信号描述为:

信号描述为: 同理,可以通过前面介绍的方式消除K值,以获得真实的极坐标信息,但是如果只是需求得到极坐标的角度信息,而并不需求得到极坐标的模长信息,则可以禁止相关模块,以节省资源。

同理,可以通过前面介绍的方式消除K值,以获得真实的极坐标信息,但是如果只是需求得到极坐标的角度信息,而并不需求得到极坐标的模长信息,则可以禁止相关模块,以节省资源。

此外,还需要注意的是数据格式,以及数据格式与是否使能Compensation功能的关系等内容。该部分内容比较简单,这里就不详细介绍了……

主要参考资料:1、百度百科:https://baike.baidu.com/item/CORDIC/5189325?fr=aladdin2、网友 乐富道的博客:http://www.cnblogs.com/touchblue/p/3535968.html 3、Lattice CORDIC IP的User Guide: CORDICIPCoreUsersGuide.PDF4、Altera CORDIC IP的User Guide:

CORDICIPCoreUsersGuide.PDF4、Altera CORDIC IP的User Guide: ALTERA_CORDIC IP Core User Guide.pdf5、Xilinx CORDIC IP的User Guide:

ALTERA_CORDIC IP Core User Guide.pdf5、Xilinx CORDIC IP的User Guide: CORDIC v6.0 LogiCORE IP Product Guide.pdf6、维基百科:https://en.wikipedia.org/wiki/CORDIC

CORDIC v6.0 LogiCORE IP Product Guide.pdf6、维基百科:https://en.wikipedia.org/wiki/CORDIC

本文转载自http://blog.chinaaet.com/justlxy/p/5100052271,如涉及侵权,请私信小编删除。============华 丽 的 分 割 线============

想加入我们FPGA学习交流群吗?可以长按或扫描以下二维码,审核通过后我们邀请您加入。这些微信群旨在打造一个提供给FPGA工程开发人员及兴趣爱好者(统称“FPGAer”)进行技术交流、答疑解惑和学习的平台。而且我们也将会通过网络举办FPGA技术讲座,分享相关研究文献。

了解更多FPGA知识可以长按或扫描以下二维码关注“FPGAer俱乐部”。

- Vector Rotation:主要用于极坐标到直角坐标的转换

- Vector Translation:主要用于直角坐标到极坐标的转换

- Sin & Cos:主要用于计算正弦和余弦

- Arctan:主要用用于计算反正切函数

CORDIC的思想是,将旋转theta度,拆分为多个步骤,依次迭代进行。其中,某一个步骤的计算等式如下:

CORDIC的思想是,将旋转theta度,拆分为多个步骤,依次迭代进行。其中,某一个步骤的计算等式如下: 这里的theta i的取值是有讲究的,需要满足如下等式:

这里的theta i的取值是有讲究的,需要满足如下等式:

上式中,i为正整数,i的最大值就是迭代的次数。显然i的最大值越大,计算得到的结果将越精确。但是在实际的情况下,i不可能取无穷大的,一般取16左右,就能得到较为精确的值了(取16时,大约可以精确到小数点后3-4位,Lattice的IP最高可以取值为32)。此时,显然有:

上式中,i为正整数,i的最大值就是迭代的次数。显然i的最大值越大,计算得到的结果将越精确。但是在实际的情况下,i不可能取无穷大的,一般取16左右,就能得到较为精确的值了(取16时,大约可以精确到小数点后3-4位,Lattice的IP最高可以取值为32)。此时,显然有:

将cos theta表示为Ki,则有:

将cos theta表示为Ki,则有: 需要注意的是,关于Ki的值,Lattice与Xilinx并未明确指出,而Altera则取的是一个定值(常量),值为1.6467602……。个人觉得应该处理方法是相似的,具体可以看:http://blog.chinaaet.com/justlxy/p/5100052282实际上,无论是哪一家都可以通过IP配置时的scale factor compensation选项进行自动消除K值的影响。上面的介绍可能不太直观,下面再来看一个网友提供的更为直观的栗子,以加深理解:

需要注意的是,关于Ki的值,Lattice与Xilinx并未明确指出,而Altera则取的是一个定值(常量),值为1.6467602……。个人觉得应该处理方法是相似的,具体可以看:http://blog.chinaaet.com/justlxy/p/5100052282实际上,无论是哪一家都可以通过IP配置时的scale factor compensation选项进行自动消除K值的影响。上面的介绍可能不太直观,下面再来看一个网友提供的更为直观的栗子,以加深理解: 即,如果需要计算cos45°或者sin45°,则需要进行N次迭代,每次theta的取值如图中黄 {MOD}部分所示。二、Lattice的CORDIC IP使用说明

即,如果需要计算cos45°或者sin45°,则需要进行N次迭代,每次theta的取值如图中黄 {MOD}部分所示。二、Lattice的CORDIC IP使用说明下面来聊一聊Lattice的CORDIC的IP的四个模式的基本使用方法和注意事项。首先看一下,CORDIC的结构框图:

下面依次介绍一下各个模块的作用:

下面依次介绍一下各个模块的作用:- In Register:这个没什么好说的;

- Pre-Processor:默认的CORDIC只能处理输入角度范围为(-π/2,π/2)之间的旋转或者三角运算。如果用户需要计算超过这个范围的角度,则需要使能这个模块(在IP配置界面有一个复选框,默认选中)。显然,如果选中该模块则意味着需要更多的资源……

- CORDIC Arithmetic Unit:算法核心模块。有两种配置方式,分别是parallel (with single-cycle data throughput) and word-serial (with multiple-cycle throughput)。其中,并行配置模式使用了流水线结构,适合与批量处理数据;而Word-serial则使用了较少的资源。

- Arctan ROM:用于存放tan-1(2-i)值的ROM。

- Controller:控制器,用于控制迭代次数,ROM寻址,产生rfi信号(ready for input)和outvalid(输出有效信号)。

- Post-Processor:可以通过IP的配置界面,使能或者禁止使用该模块。对于Lattice的IP,可选LUT Based或者DSP Based的Compensation方式。该模块主要用于去除迭代过程中所带来的向量(x,y)模(Magnitude)的增益,对于不需要使用向量模的场合,可以直接禁止该模块。

- Rounding:该模块提供了四种进位取整的模式,详见下图:

其中CORDIC Arithmetic Unit的基本结构图为:

接下来接着介绍,前面说提到的四种功能:

接下来接着介绍,前面说提到的四种功能:- 首先是Vector Rotation,该功能主要用于极坐标到直角坐标的转换。如下图所示

信号描述如下图所示:

信号描述如下图所示: xin和yin为输入,即(x,y),xout和yout为输出,即(x0,y0)。V0的模中的K可以通过前面介绍的方法来消除。

xin和yin为输入,即(x,y),xout和yout为输出,即(x0,y0)。V0的模中的K可以通过前面介绍的方法来消除。- Vector Translation:该模式主要用于将直角坐标转换为极坐标。如下图所示:

信号描述为:

信号描述为: 同理,可以通过前面介绍的方式消除K值,以获得真实的极坐标信息,但是如果只是需求得到极坐标的角度信息,而并不需求得到极坐标的模长信息,则可以禁止相关模块,以节省资源。

同理,可以通过前面介绍的方式消除K值,以获得真实的极坐标信息,但是如果只是需求得到极坐标的角度信息,而并不需求得到极坐标的模长信息,则可以禁止相关模块,以节省资源。- sin & cos

- Arctan

此外,还需要注意的是数据格式,以及数据格式与是否使能Compensation功能的关系等内容。该部分内容比较简单,这里就不详细介绍了……

主要参考资料:1、百度百科:https://baike.baidu.com/item/CORDIC/5189325?fr=aladdin2、网友 乐富道的博客:http://www.cnblogs.com/touchblue/p/3535968.html 3、Lattice CORDIC IP的User Guide:

CORDICIPCoreUsersGuide.PDF4、Altera CORDIC IP的User Guide:

CORDICIPCoreUsersGuide.PDF4、Altera CORDIC IP的User Guide: ALTERA_CORDIC IP Core User Guide.pdf5、Xilinx CORDIC IP的User Guide:

ALTERA_CORDIC IP Core User Guide.pdf5、Xilinx CORDIC IP的User Guide: CORDIC v6.0 LogiCORE IP Product Guide.pdf6、维基百科:https://en.wikipedia.org/wiki/CORDIC

CORDIC v6.0 LogiCORE IP Product Guide.pdf6、维基百科:https://en.wikipedia.org/wiki/CORDIC本文转载自http://blog.chinaaet.com/justlxy/p/5100052271,如涉及侵权,请私信小编删除。============华 丽 的 分 割 线============

想加入我们FPGA学习交流群吗?可以长按或扫描以下二维码,审核通过后我们邀请您加入。这些微信群旨在打造一个提供给FPGA工程开发人员及兴趣爱好者(统称“FPGAer”)进行技术交流、答疑解惑和学习的平台。而且我们也将会通过网络举办FPGA技术讲座,分享相关研究文献。

了解更多FPGA知识可以长按或扫描以下二维码关注“FPGAer俱乐部”。