DM8148 通过编译例程打印得到Processor List:

procId =0, procName=DSP

procId =1, procName=VIDEO-M3

procId =2, procName=VPSS-M3

procId =3, procName=HOST 在实际应用中,

DSP核用作算法处理 video-m3是用作编码解码的 vpss-m3是用作视频捕获、nsf、dei和显示等模块处理的 HOST用于控制

The HDVICP2 supports resolutions up to 1080 p/i with full performance of 60 fps (or 120 fields). The

HDVICP2 subsystem supports the following codec standards natively; that is, all functions of standards

are accelerated (without any intervention of the digital signal processor [Media Controller]):

• H.264: BP/MP/HP Encode and Decode

• H.264: Fast Profile/RCDO Encode and Decode

• MPEG-4: SP/ASP Encode/Decode (No support for GMC)

• DivX 5.x & higher Encode/Decode (No lower version; for example, 3.11 and 4.x)

• H.263: Profile 0 and 3 for Decode, Profile 0 for Encode

• Sorenson Spark: V0 and V1 Decode (No encode support)

• MPEG-2 SP/MP Encode/Decode

• MPEG-1 Encode/Decode

• VC1/WMV9/RTV : SP/MP/AP Encode and Decode

• ON2 VP6/VP7 Decode

• RV 8/9/10 Decode

• AVS 1.0 Encode and Decode

• JPEG (also MJPEG) Baseline Encode/Decode

• H264 Annex H (MVC)

procId =0, procName=DSP

procId =1, procName=VIDEO-M3

procId =2, procName=VPSS-M3

procId =3, procName=HOST 在实际应用中,

DSP核用作算法处理 video-m3是用作编码解码的 vpss-m3是用作视频捕获、nsf、dei和显示等模块处理的 HOST用于控制

HD Video Coprocessor Subsystem

The HDVICP2 is the image and video imaging hardware accelerator subsystem.The HDVICP2 supports resolutions up to 1080 p/i with full performance of 60 fps (or 120 fields). The

HDVICP2 subsystem supports the following codec standards natively; that is, all functions of standards

are accelerated (without any intervention of the digital signal processor [Media Controller]):

• H.264: BP/MP/HP Encode and Decode

• H.264: Fast Profile/RCDO Encode and Decode

• MPEG-4: SP/ASP Encode/Decode (No support for GMC)

• DivX 5.x & higher Encode/Decode (No lower version; for example, 3.11 and 4.x)

• H.263: Profile 0 and 3 for Decode, Profile 0 for Encode

• Sorenson Spark: V0 and V1 Decode (No encode support)

• MPEG-2 SP/MP Encode/Decode

• MPEG-1 Encode/Decode

• VC1/WMV9/RTV : SP/MP/AP Encode and Decode

• ON2 VP6/VP7 Decode

• RV 8/9/10 Decode

• AVS 1.0 Encode and Decode

• JPEG (also MJPEG) Baseline Encode/Decode

• H264 Annex H (MVC)

high definition video processing subsystem

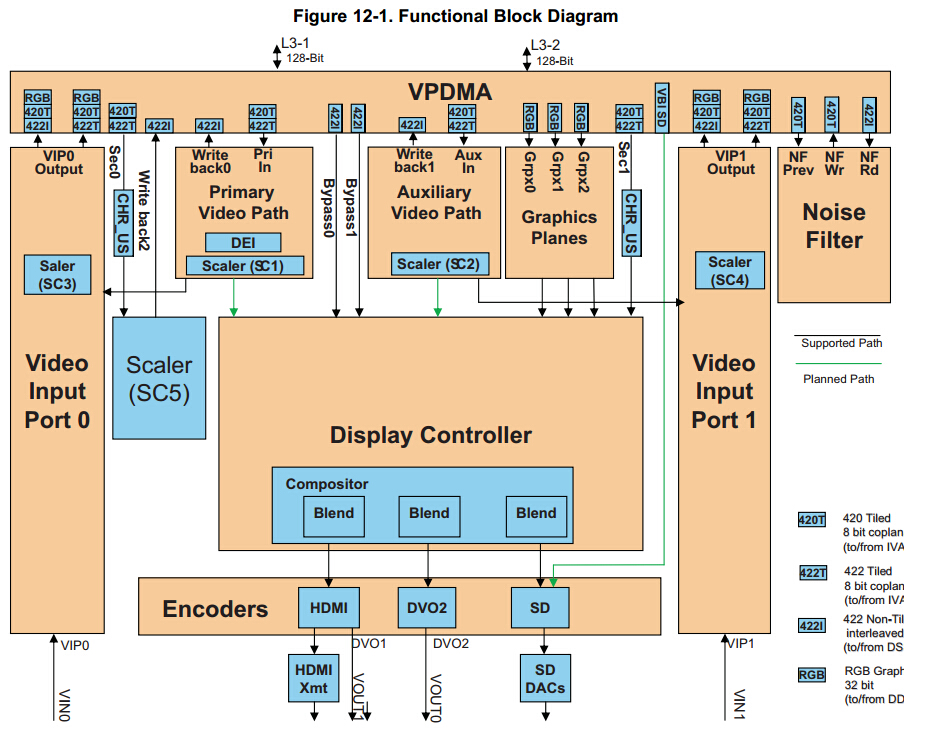

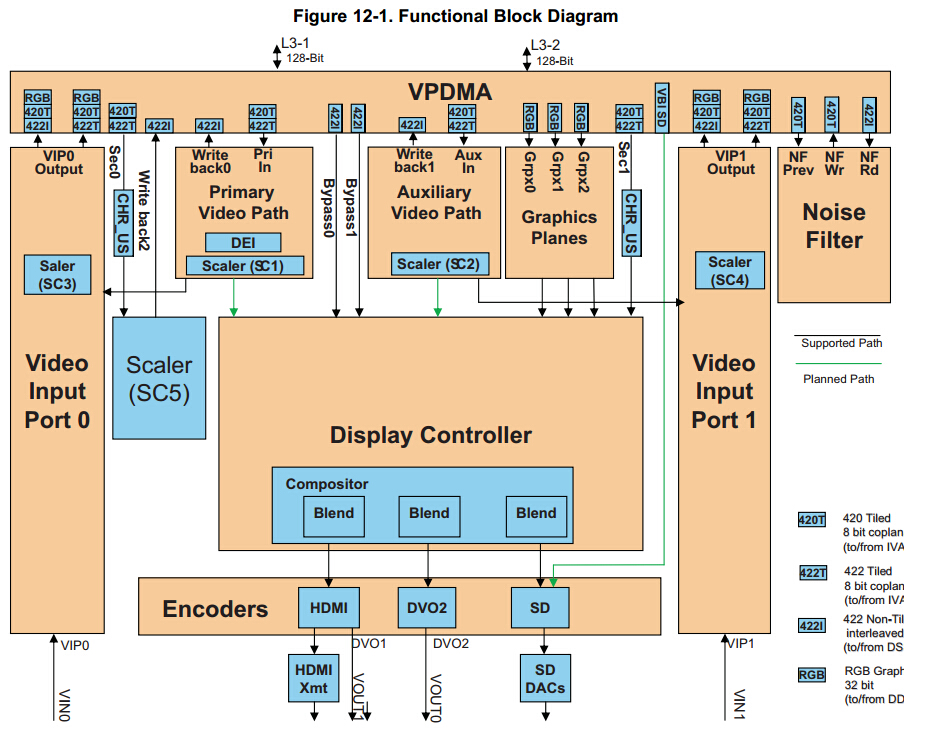

The high definition video processing subsystem (HDVPSS) includes video/graphics display and capture processing using the latest TI developed algorithms, flexible compositing and blending engine, and a full range of external video interfaces in order to deliver high quality video contents to the end devices.