I2C Serial EEPROM Family

一 功能介绍

1、能页操作,每页可达128字节。

2、具有的功能地址线,允许8个器件挂在同一总线上。高达4MBit的地址空间(64k x 8=512bit | 512bit x 8 = 4Mbit)

3、在512k范围内,可随机读和顺序读。

4、板级供电电压范围 1.7V to 5.5V。

二 引脚描述

引脚名

功能

A0

芯片选择(用户可配置)

A1

芯片选择(用户可配置)

A2

芯片选择(用户可配置)

NC

未连接

VSS

地

SDA

串行数据

SCL

串行时钟

WP

写保护输入

VCC

电源

二 引脚描述

引脚名

功能

A0

芯片选择(用户可配置)

A1

芯片选择(用户可配置)

A2

芯片选择(用户可配置)

NC

未连接

VSS

地

SDA

串行数据

SCL

串行时钟

WP

写保护输入

VCC

电源

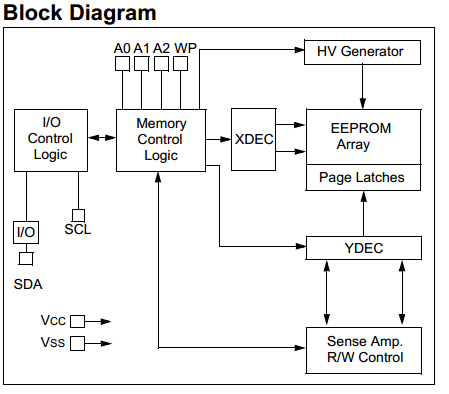

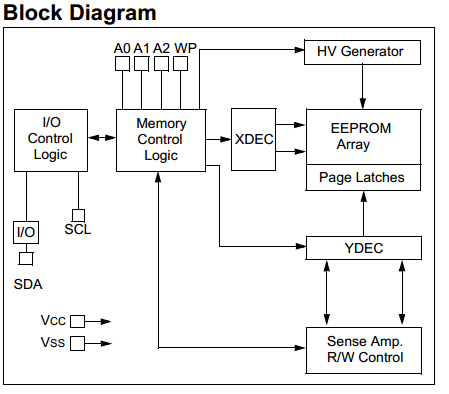

2.0 A0,A1 AND A2 芯片地址输入 n芯片地址引脚允许8个芯片挂在同一条总线上。当引脚的逻辑电平与芯片内部相应的设备地址相同时,芯片使能。 芯片引脚的输入使能时 VCC 和VSS n在大多数的应用中,地址线是被硬件拉高和拉低的。在那些引脚受 microcontroller 和可编程器件控制的应用中,在访问该EEPROM芯片之前,EEPROM的引脚要先拉高或拉低。 2.1 Serial Data (SDA) n 该双向引脚是用来传输数据和地址的。 该引脚是内部开漏,所以 SDA引脚要接一个上拉电阻到VCC( 典型的是 10kohm/100khz, 2kohm/400Khz,1Mhz). n 在数据传输中,SDA只有在SCL线为低时才发生改变。在 SCL线为高时SDA发生改变则被认为是开始或停止。 2.2 Serial Clock (SCL) 数据同步时钟 2.3 Write-Protect(WP) 写保护 该引脚只能连接 VCC 或者 VSS。 当连接VCC时,允许对芯片写操作,当连接VSS,对芯片写操作禁止。该引脚对芯片读操作没有任何影响。 三 功能描述 24XX512支持双向2线制总线和数据传输协议。在总线数据发送数据的成为发送方,接收数据的为接收方。 当24XX512为从设备时,串行时钟(SCL)由主设备产生,来控制总线的访问和产生开始和结束条件。 主设备和从设备都可以作为接收方和发送方,但是只有主设备才能决定处于那种模式。 四 总线特点 总线协议 1、总线在非忙状态下数据传输才会启动。 2、数据传输过程中,当时钟线为高时,数据线要保持 stable。在时钟线为高时,数据线状态发生改变则被认为是开始或结束条件。 总线不忙【 Bus Not Busy (A)】 数据线和时钟线为高电平 开始数据传输【Start Data Transfer (B)】 当时钟线为高时,数据线由高到低则表示开始数据传输。所有的命令都需要该开始条件。 停止数据传输【Stop Data Transfer (C)】 当时钟线为高时,数据线由低到高则表示开始数据传输。所有的操作都需要该停止条件。 数据有效【Data Valid (D)】 启动条件产生后数据开始传输,停止条件发生时则停止数据传输。 在时钟线为高电平时保持stable 在时钟线为低时发生改变。每个时钟脉冲传输一位数据。 应答信号

每个选中的从设备在接收完一个字节的数据之后都会产生一个应答信号。所以,每个主设备必须产生一个额外的时钟脉冲来匹配该应答位。在该时钟脉冲的高电平器件,SDA要保持stable low。建立时间和保持时间都要考虑。

在读操作时,主设备会发出一个数据结束信号给从设备,告知从设备不需在从设备 clock out的最后一个字节产生应答信号。在这种情况下,从设备(24xx512)会拉高数据线从而使从设备发出停止条件(有点没明白)。

应答信号

每个选中的从设备在接收完一个字节的数据之后都会产生一个应答信号。所以,每个主设备必须产生一个额外的时钟脉冲来匹配该应答位。在该时钟脉冲的高电平器件,SDA要保持stable low。建立时间和保持时间都要考虑。

在读操作时,主设备会发出一个数据结束信号给从设备,告知从设备不需在从设备 clock out的最后一个字节产生应答信号。在这种情况下,从设备(24xx512)会拉高数据线从而使从设备发出停止条件(有点没明白)。

应答开始:发送方必须释放SDA线,允许接收方将SDA拉低来产生应答信号。

应答结束:接收方必须释放SDA线,允许发送方继续发送数据。

五 设备寻址

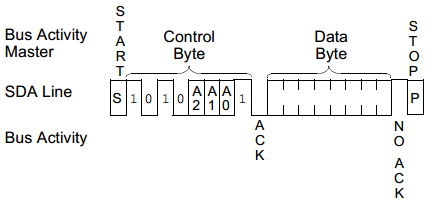

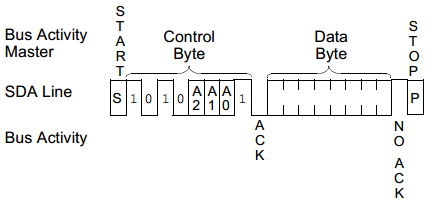

开始条件产生后低一个接受的字节就是控制字。控制字包括4个控制码,对于24XX512,4个控制位为‘1010’意味着读写操作。控制码之后的三个位就是地址位 A2,A1,A0,当A2,A1,A0与引脚逻辑状态一致,则该芯片就被选中可以访问了。地址之后就是一个读写控制位,‘0’为写,‘1’为读。如图所示

应答开始:发送方必须释放SDA线,允许接收方将SDA拉低来产生应答信号。

应答结束:接收方必须释放SDA线,允许发送方继续发送数据。

五 设备寻址

开始条件产生后低一个接受的字节就是控制字。控制字包括4个控制码,对于24XX512,4个控制位为‘1010’意味着读写操作。控制码之后的三个位就是地址位 A2,A1,A0,当A2,A1,A0与引脚逻辑状态一致,则该芯片就被选中可以访问了。地址之后就是一个读写控制位,‘0’为写,‘1’为读。如图所示

再之后的两个字节就是读写第一个字节的地址。

再之后的两个字节就是读写第一个字节的地址。

六 多器件的连续寻址

前面说过,三个地址为可以扩展到4Mbit的寻址空间,我们可以同过复用A2,A1,A0引脚来达到连续寻址这4Mbit空间。

可以把A0当做A16,A1当做A17,A2当做A18来实现。所以在这种方式下,对于当个器件访问时,如果地址超过了其当个器件的地址范围,我们就不能溢出读取了(即如果是64kb空间,当我访问的地址是65k时,如果是对单个器件而言,它实际访问的地址就是3kb地址,而多器件连续访问的就是65kb)。---这种仅仅是从逻辑上来考虑的。

七 写操作

7.1 字写

首先是启动信息->控制字->地址高字节+地址低字节->这设备发送数据。

六 多器件的连续寻址

前面说过,三个地址为可以扩展到4Mbit的寻址空间,我们可以同过复用A2,A1,A0引脚来达到连续寻址这4Mbit空间。

可以把A0当做A16,A1当做A17,A2当做A18来实现。所以在这种方式下,对于当个器件访问时,如果地址超过了其当个器件的地址范围,我们就不能溢出读取了(即如果是64kb空间,当我访问的地址是65k时,如果是对单个器件而言,它实际访问的地址就是3kb地址,而多器件连续访问的就是65kb)。---这种仅仅是从逻辑上来考虑的。

七 写操作

7.1 字写

首先是启动信息->控制字->地址高字节+地址低字节->这设备发送数据。

当WP为高时,如果对设备进行写操作,24XX512会发出应答信号,但不会产生写周期。而且24xx512将又处于接收下一个命令控制字状态。

7.2 页写(page write)

和字写操作顺序是一样的,只是在页写时,当传送完一个字节后,主设不是发出一个结束信号,二是继续传送另外的127个字节。当24xx512接收完一个数据之后,内部的地址指针会自动加1。

如果主设想传送多与一页的数据时,必须要在一页传送完成后产生一个停止位。不然的话,内部地址指针会溢出计数(roll over),这样的话之前写进去的数据就会被重写掉。

当WP为高时,如果对设备进行写操作,24XX512会发出应答信号,但不会产生写周期。而且24xx512将又处于接收下一个命令控制字状态。

当WP为高时,如果对设备进行写操作,24XX512会发出应答信号,但不会产生写周期。而且24xx512将又处于接收下一个命令控制字状态。

7.2 页写(page write)

和字写操作顺序是一样的,只是在页写时,当传送完一个字节后,主设不是发出一个结束信号,二是继续传送另外的127个字节。当24xx512接收完一个数据之后,内部的地址指针会自动加1。

如果主设想传送多与一页的数据时,必须要在一页传送完成后产生一个停止位。不然的话,内部地址指针会溢出计数(roll over),这样的话之前写进去的数据就会被重写掉。

当WP为高时,如果对设备进行写操作,24XX512会发出应答信号,但不会产生写周期。而且24xx512将又处于接收下一个命令控制字状态。

7.3 写保护

写保护引脚会在每个命令字的停止位时进行抽样。在停止位后改变WP PIN状态不会对写周期的执行产生影响。

7.4 应答轮询机制

如果使用I2C接口电路,可以路过。

八 读操作

读操作和写操作基本上是一致的,除了控制自理RW位为1之外。

有三种基本的读操作类型:当前地址读,随机读,顺序读。

8.1 当期地址读

24XX512颞部有一个地址指针,指向最后一个访问字节的地址,且访问完一个字节后能够自增1。因此,如果先前的访问地址是n(legal address),下一个当前地址就是 n+1 。

一旦接受到控制字且 RW为1,即读操作时,24xx512就会发出一个应答信号和8位数据。主设可以通过不发送应答信号而产生一个停止条件来终止连续传输。

7.3 写保护

写保护引脚会在每个命令字的停止位时进行抽样。在停止位后改变WP PIN状态不会对写周期的执行产生影响。

7.4 应答轮询机制

如果使用I2C接口电路,可以路过。

八 读操作

读操作和写操作基本上是一致的,除了控制自理RW位为1之外。

有三种基本的读操作类型:当前地址读,随机读,顺序读。

8.1 当期地址读

24XX512颞部有一个地址指针,指向最后一个访问字节的地址,且访问完一个字节后能够自增1。因此,如果先前的访问地址是n(legal address),下一个当前地址就是 n+1 。

一旦接受到控制字且 RW为1,即读操作时,24xx512就会发出一个应答信号和8位数据。主设可以通过不发送应答信号而产生一个停止条件来终止连续传输。

8.2 随机读

首先进行写操作,将随机读取的第一个字节地址发送到24xx512。

然后再进行读操作。

主设在接收完最后一个数据之后同过不发应答信号而是发出停止信号来停止连续传输。

8.3 顺序读

与随机读取不同的是,在传送完第一个字节之后,主设会发出应答位,从而使24xx512继续传输下一个数据。主设在接收完最后一个数据之后同过不发应答信号而是发出停止信号来停止连续传输。

为了支持顺序读,24xx512内部有个地址指针,能够在每次读取操作完成后自增1。这个地址指针能够在一次操作中寻址整个存储空间。 The internal Address Pointer will automatically roll over from address FFFF to address 0000 if the master acknowledges the byte received from the array address FFFF

8.2 随机读

首先进行写操作,将随机读取的第一个字节地址发送到24xx512。

然后再进行读操作。

主设在接收完最后一个数据之后同过不发应答信号而是发出停止信号来停止连续传输。

8.3 顺序读

与随机读取不同的是,在传送完第一个字节之后,主设会发出应答位,从而使24xx512继续传输下一个数据。主设在接收完最后一个数据之后同过不发应答信号而是发出停止信号来停止连续传输。

为了支持顺序读,24xx512内部有个地址指针,能够在每次读取操作完成后自增1。这个地址指针能够在一次操作中寻址整个存储空间。 The internal Address Pointer will automatically roll over from address FFFF to address 0000 if the master acknowledges the byte received from the array address FFFF

二 引脚描述

引脚名

功能

A0

芯片选择(用户可配置)

A1

芯片选择(用户可配置)

A2

芯片选择(用户可配置)

NC

未连接

VSS

地

SDA

串行数据

SCL

串行时钟

WP

写保护输入

VCC

电源

二 引脚描述

引脚名

功能

A0

芯片选择(用户可配置)

A1

芯片选择(用户可配置)

A2

芯片选择(用户可配置)

NC

未连接

VSS

地

SDA

串行数据

SCL

串行时钟

WP

写保护输入

VCC

电源

2.0 A0,A1 AND A2 芯片地址输入 n芯片地址引脚允许8个芯片挂在同一条总线上。当引脚的逻辑电平与芯片内部相应的设备地址相同时,芯片使能。 芯片引脚的输入使能时 VCC 和VSS n在大多数的应用中,地址线是被硬件拉高和拉低的。在那些引脚受 microcontroller 和可编程器件控制的应用中,在访问该EEPROM芯片之前,EEPROM的引脚要先拉高或拉低。 2.1 Serial Data (SDA) n 该双向引脚是用来传输数据和地址的。 该引脚是内部开漏,所以 SDA引脚要接一个上拉电阻到VCC( 典型的是 10kohm/100khz, 2kohm/400Khz,1Mhz). n 在数据传输中,SDA只有在SCL线为低时才发生改变。在 SCL线为高时SDA发生改变则被认为是开始或停止。 2.2 Serial Clock (SCL) 数据同步时钟 2.3 Write-Protect(WP) 写保护 该引脚只能连接 VCC 或者 VSS。 当连接VCC时,允许对芯片写操作,当连接VSS,对芯片写操作禁止。该引脚对芯片读操作没有任何影响。 三 功能描述 24XX512支持双向2线制总线和数据传输协议。在总线数据发送数据的成为发送方,接收数据的为接收方。 当24XX512为从设备时,串行时钟(SCL)由主设备产生,来控制总线的访问和产生开始和结束条件。 主设备和从设备都可以作为接收方和发送方,但是只有主设备才能决定处于那种模式。 四 总线特点 总线协议 1、总线在非忙状态下数据传输才会启动。 2、数据传输过程中,当时钟线为高时,数据线要保持 stable。在时钟线为高时,数据线状态发生改变则被认为是开始或结束条件。 总线不忙【 Bus Not Busy (A)】 数据线和时钟线为高电平 开始数据传输【Start Data Transfer (B)】 当时钟线为高时,数据线由高到低则表示开始数据传输。所有的命令都需要该开始条件。 停止数据传输【Stop Data Transfer (C)】 当时钟线为高时,数据线由低到高则表示开始数据传输。所有的操作都需要该停止条件。 数据有效【Data Valid (D)】 启动条件产生后数据开始传输,停止条件发生时则停止数据传输。 在时钟线为高电平时保持stable 在时钟线为低时发生改变。每个时钟脉冲传输一位数据。

应答信号

每个选中的从设备在接收完一个字节的数据之后都会产生一个应答信号。所以,每个主设备必须产生一个额外的时钟脉冲来匹配该应答位。在该时钟脉冲的高电平器件,SDA要保持stable low。建立时间和保持时间都要考虑。

在读操作时,主设备会发出一个数据结束信号给从设备,告知从设备不需在从设备 clock out的最后一个字节产生应答信号。在这种情况下,从设备(24xx512)会拉高数据线从而使从设备发出停止条件(有点没明白)。

应答信号

每个选中的从设备在接收完一个字节的数据之后都会产生一个应答信号。所以,每个主设备必须产生一个额外的时钟脉冲来匹配该应答位。在该时钟脉冲的高电平器件,SDA要保持stable low。建立时间和保持时间都要考虑。

在读操作时,主设备会发出一个数据结束信号给从设备,告知从设备不需在从设备 clock out的最后一个字节产生应答信号。在这种情况下,从设备(24xx512)会拉高数据线从而使从设备发出停止条件(有点没明白)。

应答开始:发送方必须释放SDA线,允许接收方将SDA拉低来产生应答信号。

应答结束:接收方必须释放SDA线,允许发送方继续发送数据。

五 设备寻址

开始条件产生后低一个接受的字节就是控制字。控制字包括4个控制码,对于24XX512,4个控制位为‘1010’意味着读写操作。控制码之后的三个位就是地址位 A2,A1,A0,当A2,A1,A0与引脚逻辑状态一致,则该芯片就被选中可以访问了。地址之后就是一个读写控制位,‘0’为写,‘1’为读。如图所示

应答开始:发送方必须释放SDA线,允许接收方将SDA拉低来产生应答信号。

应答结束:接收方必须释放SDA线,允许发送方继续发送数据。

五 设备寻址

开始条件产生后低一个接受的字节就是控制字。控制字包括4个控制码,对于24XX512,4个控制位为‘1010’意味着读写操作。控制码之后的三个位就是地址位 A2,A1,A0,当A2,A1,A0与引脚逻辑状态一致,则该芯片就被选中可以访问了。地址之后就是一个读写控制位,‘0’为写,‘1’为读。如图所示

再之后的两个字节就是读写第一个字节的地址。

再之后的两个字节就是读写第一个字节的地址。

六 多器件的连续寻址

前面说过,三个地址为可以扩展到4Mbit的寻址空间,我们可以同过复用A2,A1,A0引脚来达到连续寻址这4Mbit空间。

可以把A0当做A16,A1当做A17,A2当做A18来实现。所以在这种方式下,对于当个器件访问时,如果地址超过了其当个器件的地址范围,我们就不能溢出读取了(即如果是64kb空间,当我访问的地址是65k时,如果是对单个器件而言,它实际访问的地址就是3kb地址,而多器件连续访问的就是65kb)。---这种仅仅是从逻辑上来考虑的。

七 写操作

7.1 字写

首先是启动信息->控制字->地址高字节+地址低字节->这设备发送数据。

六 多器件的连续寻址

前面说过,三个地址为可以扩展到4Mbit的寻址空间,我们可以同过复用A2,A1,A0引脚来达到连续寻址这4Mbit空间。

可以把A0当做A16,A1当做A17,A2当做A18来实现。所以在这种方式下,对于当个器件访问时,如果地址超过了其当个器件的地址范围,我们就不能溢出读取了(即如果是64kb空间,当我访问的地址是65k时,如果是对单个器件而言,它实际访问的地址就是3kb地址,而多器件连续访问的就是65kb)。---这种仅仅是从逻辑上来考虑的。

七 写操作

7.1 字写

首先是启动信息->控制字->地址高字节+地址低字节->这设备发送数据。

当WP为高时,如果对设备进行写操作,24XX512会发出应答信号,但不会产生写周期。而且24xx512将又处于接收下一个命令控制字状态。

7.2 页写(page write)

和字写操作顺序是一样的,只是在页写时,当传送完一个字节后,主设不是发出一个结束信号,二是继续传送另外的127个字节。当24xx512接收完一个数据之后,内部的地址指针会自动加1。

如果主设想传送多与一页的数据时,必须要在一页传送完成后产生一个停止位。不然的话,内部地址指针会溢出计数(roll over),这样的话之前写进去的数据就会被重写掉。

当WP为高时,如果对设备进行写操作,24XX512会发出应答信号,但不会产生写周期。而且24xx512将又处于接收下一个命令控制字状态。

当WP为高时,如果对设备进行写操作,24XX512会发出应答信号,但不会产生写周期。而且24xx512将又处于接收下一个命令控制字状态。

7.2 页写(page write)

和字写操作顺序是一样的,只是在页写时,当传送完一个字节后,主设不是发出一个结束信号,二是继续传送另外的127个字节。当24xx512接收完一个数据之后,内部的地址指针会自动加1。

如果主设想传送多与一页的数据时,必须要在一页传送完成后产生一个停止位。不然的话,内部地址指针会溢出计数(roll over),这样的话之前写进去的数据就会被重写掉。

当WP为高时,如果对设备进行写操作,24XX512会发出应答信号,但不会产生写周期。而且24xx512将又处于接收下一个命令控制字状态。

7.3 写保护

写保护引脚会在每个命令字的停止位时进行抽样。在停止位后改变WP PIN状态不会对写周期的执行产生影响。

7.4 应答轮询机制

如果使用I2C接口电路,可以路过。

八 读操作

读操作和写操作基本上是一致的,除了控制自理RW位为1之外。

有三种基本的读操作类型:当前地址读,随机读,顺序读。

8.1 当期地址读

24XX512颞部有一个地址指针,指向最后一个访问字节的地址,且访问完一个字节后能够自增1。因此,如果先前的访问地址是n(legal address),下一个当前地址就是 n+1 。

一旦接受到控制字且 RW为1,即读操作时,24xx512就会发出一个应答信号和8位数据。主设可以通过不发送应答信号而产生一个停止条件来终止连续传输。

7.3 写保护

写保护引脚会在每个命令字的停止位时进行抽样。在停止位后改变WP PIN状态不会对写周期的执行产生影响。

7.4 应答轮询机制

如果使用I2C接口电路,可以路过。

八 读操作

读操作和写操作基本上是一致的,除了控制自理RW位为1之外。

有三种基本的读操作类型:当前地址读,随机读,顺序读。

8.1 当期地址读

24XX512颞部有一个地址指针,指向最后一个访问字节的地址,且访问完一个字节后能够自增1。因此,如果先前的访问地址是n(legal address),下一个当前地址就是 n+1 。

一旦接受到控制字且 RW为1,即读操作时,24xx512就会发出一个应答信号和8位数据。主设可以通过不发送应答信号而产生一个停止条件来终止连续传输。

8.2 随机读

首先进行写操作,将随机读取的第一个字节地址发送到24xx512。

然后再进行读操作。

主设在接收完最后一个数据之后同过不发应答信号而是发出停止信号来停止连续传输。

8.3 顺序读

与随机读取不同的是,在传送完第一个字节之后,主设会发出应答位,从而使24xx512继续传输下一个数据。主设在接收完最后一个数据之后同过不发应答信号而是发出停止信号来停止连续传输。

为了支持顺序读,24xx512内部有个地址指针,能够在每次读取操作完成后自增1。这个地址指针能够在一次操作中寻址整个存储空间。 The internal Address Pointer will automatically roll over from address FFFF to address 0000 if the master acknowledges the byte received from the array address FFFF

8.2 随机读

首先进行写操作,将随机读取的第一个字节地址发送到24xx512。

然后再进行读操作。

主设在接收完最后一个数据之后同过不发应答信号而是发出停止信号来停止连续传输。

8.3 顺序读

与随机读取不同的是,在传送完第一个字节之后,主设会发出应答位,从而使24xx512继续传输下一个数据。主设在接收完最后一个数据之后同过不发应答信号而是发出停止信号来停止连续传输。

为了支持顺序读,24xx512内部有个地址指针,能够在每次读取操作完成后自增1。这个地址指针能够在一次操作中寻址整个存储空间。 The internal Address Pointer will automatically roll over from address FFFF to address 0000 if the master acknowledges the byte received from the array address FFFF