1. 背景介绍

1.1. Tensilica介绍

Tensilica 是一个迅速成长的公司,公司主要产品是在专业性应用程序

微处理器上,为现今高容量

嵌入式系统提供最优良的解决方案。公司成立于1997年7月,该公司的投资者包括三家声名卓著的创投公司:Oak Investment Partners, Worldview Technology Partners 和 Foundation Capital, 与高科技电子业内著名的五家公司:Cisco Systems,Inc,Matsushita Electric Industrial Company Ltd, Altera Corporation,NEC Corporation 和 Conexant Systems。Tensilica的创始人为Chris Rowen,同时也是第一任CEO,他原来曾任职于Intel,Stanford,MIPS,SGI和Synopsys,同时他也是可重构处理思想的提出者和实践者。

Tensilica公司创立的目的则是提供一种可以实现可重构的、核基于ASIC的、拥有对应软件开发工具的专用微处理器解决方法。通过前期技术上的发展以及三轮融资,Xtensa处理器诞生了。图1展示了Tensilica公司创业起步阶段的发展状况:

图1:Tensilica公司创业起步阶段的发展状况

Tensilica公司于2013年3月被Cadence公司以3.8亿的价格收购,为Cadence在当时最大的一次收购。Tensilica公司2012年销售额为4400万美元,收购价超过其营业额的八倍,这也充分显示了Tensilica公司的价值。

1.2. SOC处理器

在如今复杂的SOC设计中可以看到有很多种的嵌入式处理器,从通用的处理器到专用的处理器。

通用的嵌入式处理器虽然可以很好的处理各种的控制任务,但当遇到像神经网路处理、基带数据包处理、图像处理、音频处理以及信息加密处理这中复杂的大数据处理时,它们的结构、处理方法以及带宽的限制使其显示出极大地劣势。而且对于内存大小、cache尺寸和总线接口等的可选择性较小,一般是通过提升频率来提高性能,限制较大。

芯片设计者也曾将目光转向硬接线逻辑(设计RTL级blocks)来提升某些主要功能的性能。不过RTL设计的设计周期很长,而且验证所花费的时间更长,同时它也缺少必要的可编程性和灵活性。

Xtensa LX系列处理器具有很强的可重构性和可拓展性,是进行复杂密集型数字信号处理应用的理想之选,而一个固化的RTL应用也只能作为其他选择。Xtensa 处理器具有不同于其它传统式的

嵌入式处理器核心,改变了单芯片系统的设计规则。采用 Xtensa 的技术时,

系统设计工程师可以挑选所需的单元架构,再加上自创的新指令与硬件执行单元,就可以设计出比其它传统方式强大数倍的处理器核心。Xtensa 生产器可以针对每一个处理器的特殊组合,自动有效地产生出一套包括操作系统,完善周全的软件工具。可以自由装组的 Xtensa 处理器,其设计方式弹性大,功效高,是所有高合成的单芯片系统的最佳选择。它采用硬件可重构加软件编程的方式,既提升了处理器的运算性能又通过软件便于实现控制[1]。

2. Xtensa处理器的结构

对于Xtensa处理器结构,接下来分硬件结构和指令集架构两部分分别介绍。

2.1. Xtensa处理器的硬件结构

纯硬件的系统便于进行计算,不便于实现控制,而软件系统则正好相反(如图2),Xtensa处理器正好利用了两者的优势来进行处理器设计,它采用硬件可重构加软件编程的方式,既提升了处理器的运算性能又通过软件便于实现控制。

图2 软硬件在计算和控制方面的优劣势[2]

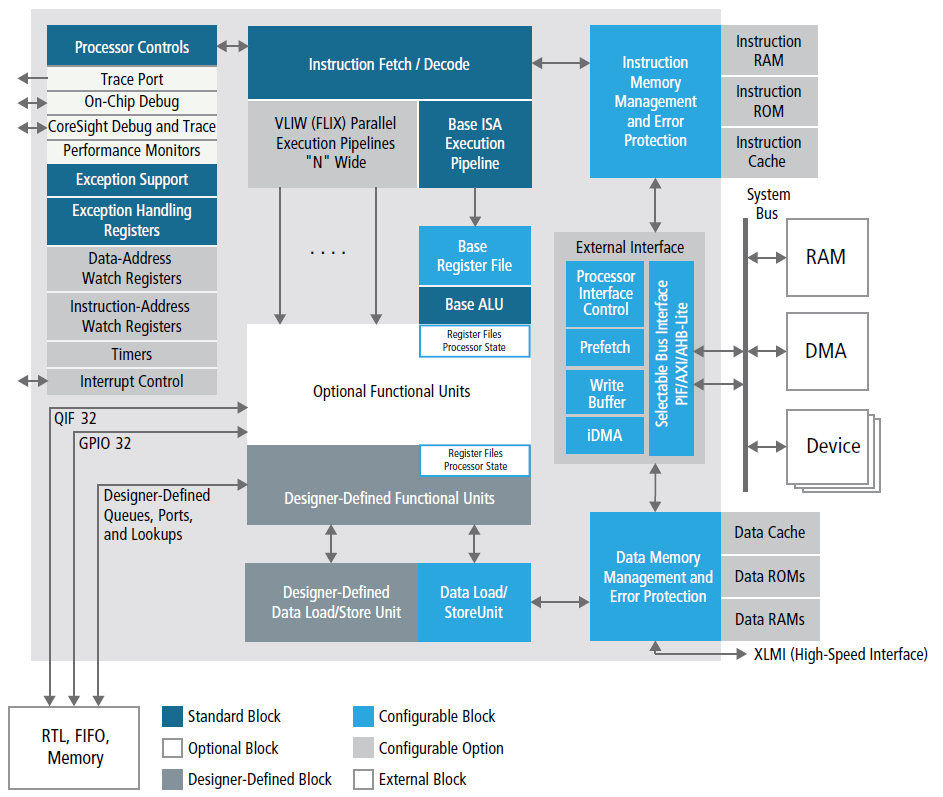

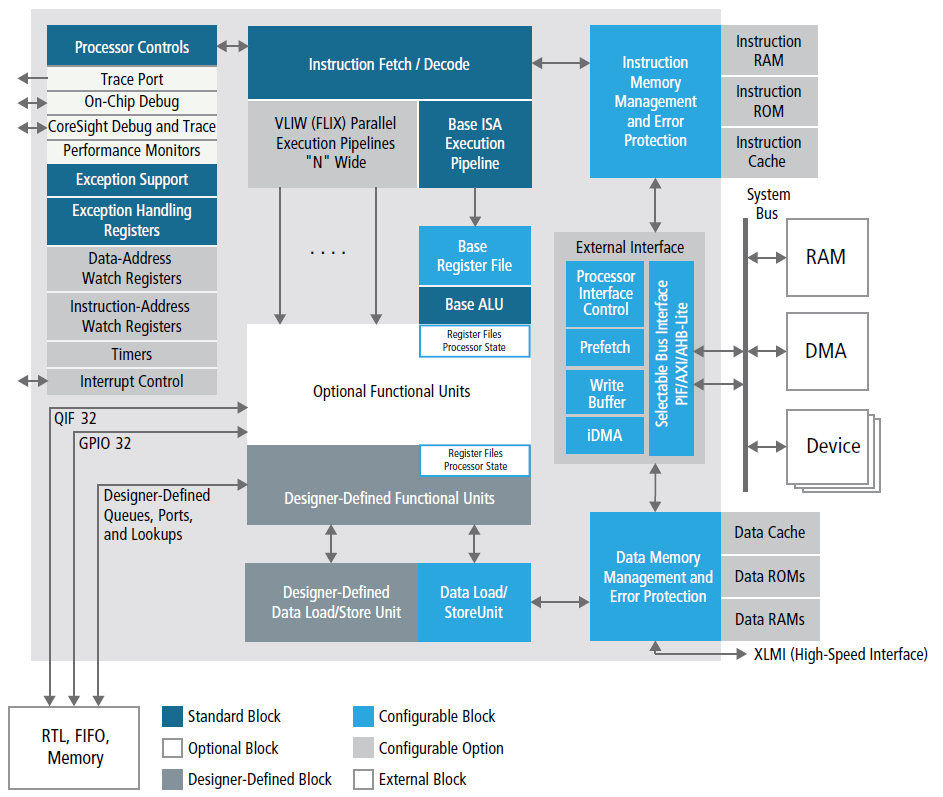

Xtensa LX7处理器结构如图3所示。

图3 Xtensa LX7处理器结构图[3]

由上图可以看到,Xtensa LX7处理器的硬件结构包含基本模块、可重构模块、可选择模块、用户定义模块、功能模块、以及拓展模块。Xtensa LX7处理器以基本模块为核心,SOC开发者可以根据需要的功能在功能模块通过编码或者图形界面选择相应的模块进行组合或者对可重构模块进行对应重构来优化运算的性能,并能够使用户在较短的时间内设计出面向特定应用的处理器。

基本模块包含Instruction Fetch/Decode模块,用来进行指令的抓取和译码;Base ALU模块,是一个基本的32位的ALU;控制模块和一些寄存器模块,用来实现控制和寄存。

可重构模块包含Instruction/Data Memory Management and Error Protection模块,用来实现对指令和数据存储器尺寸、奇偶校验和ECC的重构;Data Load/Store模块,用来重构Load/Store通路的位宽以及单双向;Base Register File模块,可重构Register的尺寸;Processor Interface Control模块,可以实现对接口不再对系统总线进行依赖,可以实现对interface、port和queue的重构;Write Buffer 模块,可以实现对1-32个buffer的选择;iDMA模块,通过重构实现接口直接读取处理器的本地数据;还有Instruction/Data 的一些存储(Cache、RAMs和ROMs)、一些寄存器(Data-Address Watch Rrgisters、Instruction-Address Watch Register)以及timer和中断控制同样是可充配置的。

用户自定义模块包含Designer-Defined Functional Units,用来实现基础功能之外的用户自定义的一些功能;Designer-Defined Data Load/Store Unit,可以实现多路的Load/Store通路,提升性能。

外部模块包含连接在数据总线上的一些外设包括RAM、DMA、Device以及一些与端口接口相连的Memory。

2.2. Xtensa处理器的ISA

这个32位的Xtensa LX7处理器的结构特 {MOD}是有一套专门为嵌入式系统设计、精简而高效能的16与24位指令集。其基本结构拥有80个 RISC 指令,其中包括32位基本的ALU,6个管理特殊功能的寄存器,32或64个普通功能32位寄存器。这些32位寄存器都设有加速运作功能的窗口。下面分别介绍一些Xtensa处理器ISA的特性。

2.2.1. 基础性质

Xtensa处理器有大量的可重构的选项,可以让用户获取实现所需功能和性能的逻辑;高效能的16/24位指令集和用户自定义的可变长度指令集(长度为4-16bytes的任意值)使内存长度和性能达到最佳状态;选用5-7级ISA流水来对不同的内存进行加速;拓展的DSP也可实现最高31级流水;可选择的队列(FIFO)、端口(GPIO)和查找接口有着几乎无限的I/O带宽来进行数据的传输,不受系统带宽的影响;可以选择通过硬件的预取来降低内存的延迟;自动生成细粒度的门控时钟可以实现功耗的降低;可以通过FLIX来实现指令的并行。

2.2.2. 兼容性

兼容性是Xtensa处理器ISA的根本,因为只有具有很强的兼容性才能很好的应用到第三方的应用软件和开发工具上去。所有的可重构、可拓展的Xtensa处理器都对主要的操作系统、调试工具以及输入校验设备兼容。同时所有版本的处理器都向上兼容,同时用户自定义的指令可以重复使用。

2.2.3. 拓展性

Xtensa处理器可以很方便的将指令无缝的添加到处理器的数据通路中。任何相关的C数据类型、软件工具链和需要的进行综合的EDA脚本都是自动生成。数据通路、相关的指令以及C数据类型都是用TIE(Tensilica Instruction Extension)语言来写的。

2.2.4. 可重构性

Xtensa处理器提供预验证的模块,当用户的设计需要时随时可以将其添加到设计中去,可以又快又好的实现所需设计。所有可重构的选项如图4所示。由图可知可重构的部分包含:在不同的应用下选用不同的DSP (HiFi DSPs for Audio/Voice/Speech,Vision P5 and P6 DSPs for Imaging and Vision,ConnX BBE16EP, BBE32EP and BBE64EP DSPs,Fusion F1 DSP,Fusion G3 DSP),实现DSP的重构;多重自定义长度的GPIO ports对外设进行控制和监测;Queue中的接口宽度可选择;32位乘法器与16位的乘法器和MAC;单精度/双精度,标量/矢量浮点数模块的选择;对于VLIW和一般的指令可以通过三路64位的FLIX实现交叉存取。

图4 Xtensa LX7 处理器最大范围的可重构选项

2.2.5. 其他性能

高低字节排序的可选择;1或2个通用的load/store unit,每个的尺寸为32-,64-,128-,256-,512-bits可选;1-32个输入可选择输入buffer; 多重自定义长度的接口是数据通过FIFO进出;FLIX的长度可选,最高128bits;数据和指定的Cache采用4路组相连,最大为128K,运用write-back和write-through的cache写入协议;可选择的对本地内存的奇偶校验和ECC。

动态功耗和漏电流功耗较小;通过中断控制来进行片上调试;可选择的16位处理器ID,支持大规模并行阵列结构;支持第三方的JTAG debug probe进行片上调试的硬件。

3. 通过Xtensa处理器为SOC设计增加灵活性和拓展性

Cadence为Soc设计者提供可以通过软件编程使其设计更加灵活性和长寿命的解决方案,以及对于特定的应用提供定制处理器。现在用户可以通过TIE(Tensilica Instruction Extension)语言设计一款功能、指令设定可拓展原始处理器设计者从未想过的特性。

TIE语言可以描述指令、寄存器、拓展单元和I/O,然后这些会自动生成并添加到处理器中。TIE语言与verilog类似,用来描述希望的指令、操作数、编码和执行语义。TIE文件是Xtensa处理器发生器的输入文件,处理器发生器自动的建立重构的处理器和完整的软件工具链,该软件工具链包含所有的可重构的功能和新的TIE指令。

TIE语言可以让用户将产品性能提升和创造其独特性。Xtensa处理器的拓展性可以将优化的特性添加或者应用到任何需要优化处理器成本、功耗、应用性能的平台上。

3.1. 灵活性

就像你可以从一系列预先确定的功能选项中选择特定的功能来提升处理器的性能,现在可以创造可以提升标准或者自定义算法指令以及更大的带宽的数据接口。通过使用提供的工具,应用的热点可以被定义,同时添加用来更高性能处理这些热点的指令,从而不再需要提升时钟频率或者重写大量的软件。

3.2. 独一性

对于通用处理器固化的功能,不同算法运算可能性能会有差异。通用处理器在进行通用计算时有优势,但是不擅长计算任何一个特定的算法。Xtensa处理器为用户提供了通过能够加速特定算法的硬件来区别的高性能的执行各种算法(其思想如图5所示)。这意味着只要用户定义的处理器达到了在相同软件上执行的性能,该设计就不可能被复制。

图5 Xtensa LX7处理器提供的添加用户定义的功能和接口的思想

3.3. 通过FLIX进行并行操作

由图5可知,用户自定义功能的实现是通过FLIX。FLIX结构使得Xtensa LX7处理器称为一个VLIW处理器,如果需要可以实现2-30的并行。FLIX指令的长度为4bytes到16bytes之间的任意值。这种可变长度的FLIX指令可以与Xtensa处理器标准的16/32 bits指令无缝混合,所以不会有模式转换上的损失。图6展示了用户使用FLIX创造VLIW进行2-30级的并行操作

通过FLIX(可变长度指令字)Xtensa处理器可以除去在使用VLIW时指令寄存器的冗余损失。事实上,使用FLIX的Xtensa可以同时提供高性能和晓得代码长度。使用FLIX的损失是很小的,只是增加了2000个门用来进行指令的控制和译码,但是带来的好处是很大的。

Xtensa的C/C++编译器自动的从源代码中提取出并行操作并将多种操作加到FLIX中,所以即使不通过额外的软件资源同样可以获得并行计算好处。通过这种方法,一个three-issue的Xtensa LX7处理器在一个较低的频率下运行也可以达到对应其他设备在相当高时钟频率下的性能。

图6. 用户使用FLIX创造VLIW进行2-30级的并行操作

还有关于接口的可重构方法,以及对应的软件部分由同组其他成员调研,在此不做讲解。

4. 总结

Xtensa 处理器的实现了对硬件和软件的共同设计,通过硬件重构进行高性能的计算,通过软件编程进行高效率的控制。而且Xtensa 处理器结构技术先进、指令精简,可以帮助系统设计师大量缩减编码的长度,从而提高指令的密集度并降低能耗。这对于高合成的单芯片系统 ASIC 而言,是减低成本的重要关健。

图1:Tensilica公司创业起步阶段的发展状况

Tensilica公司于2013年3月被Cadence公司以3.8亿的价格收购,为Cadence在当时最大的一次收购。Tensilica公司2012年销售额为4400万美元,收购价超过其营业额的八倍,这也充分显示了Tensilica公司的价值。

1.2. SOC处理器

在如今复杂的SOC设计中可以看到有很多种的嵌入式处理器,从通用的处理器到专用的处理器。

通用的嵌入式处理器虽然可以很好的处理各种的控制任务,但当遇到像神经网路处理、基带数据包处理、图像处理、音频处理以及信息加密处理这中复杂的大数据处理时,它们的结构、处理方法以及带宽的限制使其显示出极大地劣势。而且对于内存大小、cache尺寸和总线接口等的可选择性较小,一般是通过提升频率来提高性能,限制较大。

芯片设计者也曾将目光转向硬接线逻辑(设计RTL级blocks)来提升某些主要功能的性能。不过RTL设计的设计周期很长,而且验证所花费的时间更长,同时它也缺少必要的可编程性和灵活性。

Xtensa LX系列处理器具有很强的可重构性和可拓展性,是进行复杂密集型数字信号处理应用的理想之选,而一个固化的RTL应用也只能作为其他选择。Xtensa 处理器具有不同于其它传统式的嵌入式处理器核心,改变了单芯片系统的设计规则。采用 Xtensa 的技术时,系统设计工程师可以挑选所需的单元架构,再加上自创的新指令与硬件执行单元,就可以设计出比其它传统方式强大数倍的处理器核心。Xtensa 生产器可以针对每一个处理器的特殊组合,自动有效地产生出一套包括操作系统,完善周全的软件工具。可以自由装组的 Xtensa 处理器,其设计方式弹性大,功效高,是所有高合成的单芯片系统的最佳选择。它采用硬件可重构加软件编程的方式,既提升了处理器的运算性能又通过软件便于实现控制[1]。

图1:Tensilica公司创业起步阶段的发展状况

Tensilica公司于2013年3月被Cadence公司以3.8亿的价格收购,为Cadence在当时最大的一次收购。Tensilica公司2012年销售额为4400万美元,收购价超过其营业额的八倍,这也充分显示了Tensilica公司的价值。

1.2. SOC处理器

在如今复杂的SOC设计中可以看到有很多种的嵌入式处理器,从通用的处理器到专用的处理器。

通用的嵌入式处理器虽然可以很好的处理各种的控制任务,但当遇到像神经网路处理、基带数据包处理、图像处理、音频处理以及信息加密处理这中复杂的大数据处理时,它们的结构、处理方法以及带宽的限制使其显示出极大地劣势。而且对于内存大小、cache尺寸和总线接口等的可选择性较小,一般是通过提升频率来提高性能,限制较大。

芯片设计者也曾将目光转向硬接线逻辑(设计RTL级blocks)来提升某些主要功能的性能。不过RTL设计的设计周期很长,而且验证所花费的时间更长,同时它也缺少必要的可编程性和灵活性。

Xtensa LX系列处理器具有很强的可重构性和可拓展性,是进行复杂密集型数字信号处理应用的理想之选,而一个固化的RTL应用也只能作为其他选择。Xtensa 处理器具有不同于其它传统式的嵌入式处理器核心,改变了单芯片系统的设计规则。采用 Xtensa 的技术时,系统设计工程师可以挑选所需的单元架构,再加上自创的新指令与硬件执行单元,就可以设计出比其它传统方式强大数倍的处理器核心。Xtensa 生产器可以针对每一个处理器的特殊组合,自动有效地产生出一套包括操作系统,完善周全的软件工具。可以自由装组的 Xtensa 处理器,其设计方式弹性大,功效高,是所有高合成的单芯片系统的最佳选择。它采用硬件可重构加软件编程的方式,既提升了处理器的运算性能又通过软件便于实现控制[1]。

图2 软硬件在计算和控制方面的优劣势[2]

Xtensa LX7处理器结构如图3所示。

图2 软硬件在计算和控制方面的优劣势[2]

Xtensa LX7处理器结构如图3所示。

图3 Xtensa LX7处理器结构图[3]

由上图可以看到,Xtensa LX7处理器的硬件结构包含基本模块、可重构模块、可选择模块、用户定义模块、功能模块、以及拓展模块。Xtensa LX7处理器以基本模块为核心,SOC开发者可以根据需要的功能在功能模块通过编码或者图形界面选择相应的模块进行组合或者对可重构模块进行对应重构来优化运算的性能,并能够使用户在较短的时间内设计出面向特定应用的处理器。

基本模块包含Instruction Fetch/Decode模块,用来进行指令的抓取和译码;Base ALU模块,是一个基本的32位的ALU;控制模块和一些寄存器模块,用来实现控制和寄存。

可重构模块包含Instruction/Data Memory Management and Error Protection模块,用来实现对指令和数据存储器尺寸、奇偶校验和ECC的重构;Data Load/Store模块,用来重构Load/Store通路的位宽以及单双向;Base Register File模块,可重构Register的尺寸;Processor Interface Control模块,可以实现对接口不再对系统总线进行依赖,可以实现对interface、port和queue的重构;Write Buffer 模块,可以实现对1-32个buffer的选择;iDMA模块,通过重构实现接口直接读取处理器的本地数据;还有Instruction/Data 的一些存储(Cache、RAMs和ROMs)、一些寄存器(Data-Address Watch Rrgisters、Instruction-Address Watch Register)以及timer和中断控制同样是可充配置的。

用户自定义模块包含Designer-Defined Functional Units,用来实现基础功能之外的用户自定义的一些功能;Designer-Defined Data Load/Store Unit,可以实现多路的Load/Store通路,提升性能。

外部模块包含连接在数据总线上的一些外设包括RAM、DMA、Device以及一些与端口接口相连的Memory。

2.2. Xtensa处理器的ISA

这个32位的Xtensa LX7处理器的结构特 {MOD}是有一套专门为嵌入式系统设计、精简而高效能的16与24位指令集。其基本结构拥有80个 RISC 指令,其中包括32位基本的ALU,6个管理特殊功能的寄存器,32或64个普通功能32位寄存器。这些32位寄存器都设有加速运作功能的窗口。下面分别介绍一些Xtensa处理器ISA的特性。

2.2.1. 基础性质

Xtensa处理器有大量的可重构的选项,可以让用户获取实现所需功能和性能的逻辑;高效能的16/24位指令集和用户自定义的可变长度指令集(长度为4-16bytes的任意值)使内存长度和性能达到最佳状态;选用5-7级ISA流水来对不同的内存进行加速;拓展的DSP也可实现最高31级流水;可选择的队列(FIFO)、端口(GPIO)和查找接口有着几乎无限的I/O带宽来进行数据的传输,不受系统带宽的影响;可以选择通过硬件的预取来降低内存的延迟;自动生成细粒度的门控时钟可以实现功耗的降低;可以通过FLIX来实现指令的并行。

2.2.2. 兼容性

兼容性是Xtensa处理器ISA的根本,因为只有具有很强的兼容性才能很好的应用到第三方的应用软件和开发工具上去。所有的可重构、可拓展的Xtensa处理器都对主要的操作系统、调试工具以及输入校验设备兼容。同时所有版本的处理器都向上兼容,同时用户自定义的指令可以重复使用。

2.2.3. 拓展性

Xtensa处理器可以很方便的将指令无缝的添加到处理器的数据通路中。任何相关的C数据类型、软件工具链和需要的进行综合的EDA脚本都是自动生成。数据通路、相关的指令以及C数据类型都是用TIE(Tensilica Instruction Extension)语言来写的。

2.2.4. 可重构性

Xtensa处理器提供预验证的模块,当用户的设计需要时随时可以将其添加到设计中去,可以又快又好的实现所需设计。所有可重构的选项如图4所示。由图可知可重构的部分包含:在不同的应用下选用不同的DSP (HiFi DSPs for Audio/Voice/Speech,Vision P5 and P6 DSPs for Imaging and Vision,ConnX BBE16EP, BBE32EP and BBE64EP DSPs,Fusion F1 DSP,Fusion G3 DSP),实现DSP的重构;多重自定义长度的GPIO ports对外设进行控制和监测;Queue中的接口宽度可选择;32位乘法器与16位的乘法器和MAC;单精度/双精度,标量/矢量浮点数模块的选择;对于VLIW和一般的指令可以通过三路64位的FLIX实现交叉存取。

图3 Xtensa LX7处理器结构图[3]

由上图可以看到,Xtensa LX7处理器的硬件结构包含基本模块、可重构模块、可选择模块、用户定义模块、功能模块、以及拓展模块。Xtensa LX7处理器以基本模块为核心,SOC开发者可以根据需要的功能在功能模块通过编码或者图形界面选择相应的模块进行组合或者对可重构模块进行对应重构来优化运算的性能,并能够使用户在较短的时间内设计出面向特定应用的处理器。

基本模块包含Instruction Fetch/Decode模块,用来进行指令的抓取和译码;Base ALU模块,是一个基本的32位的ALU;控制模块和一些寄存器模块,用来实现控制和寄存。

可重构模块包含Instruction/Data Memory Management and Error Protection模块,用来实现对指令和数据存储器尺寸、奇偶校验和ECC的重构;Data Load/Store模块,用来重构Load/Store通路的位宽以及单双向;Base Register File模块,可重构Register的尺寸;Processor Interface Control模块,可以实现对接口不再对系统总线进行依赖,可以实现对interface、port和queue的重构;Write Buffer 模块,可以实现对1-32个buffer的选择;iDMA模块,通过重构实现接口直接读取处理器的本地数据;还有Instruction/Data 的一些存储(Cache、RAMs和ROMs)、一些寄存器(Data-Address Watch Rrgisters、Instruction-Address Watch Register)以及timer和中断控制同样是可充配置的。

用户自定义模块包含Designer-Defined Functional Units,用来实现基础功能之外的用户自定义的一些功能;Designer-Defined Data Load/Store Unit,可以实现多路的Load/Store通路,提升性能。

外部模块包含连接在数据总线上的一些外设包括RAM、DMA、Device以及一些与端口接口相连的Memory。

2.2. Xtensa处理器的ISA

这个32位的Xtensa LX7处理器的结构特 {MOD}是有一套专门为嵌入式系统设计、精简而高效能的16与24位指令集。其基本结构拥有80个 RISC 指令,其中包括32位基本的ALU,6个管理特殊功能的寄存器,32或64个普通功能32位寄存器。这些32位寄存器都设有加速运作功能的窗口。下面分别介绍一些Xtensa处理器ISA的特性。

2.2.1. 基础性质

Xtensa处理器有大量的可重构的选项,可以让用户获取实现所需功能和性能的逻辑;高效能的16/24位指令集和用户自定义的可变长度指令集(长度为4-16bytes的任意值)使内存长度和性能达到最佳状态;选用5-7级ISA流水来对不同的内存进行加速;拓展的DSP也可实现最高31级流水;可选择的队列(FIFO)、端口(GPIO)和查找接口有着几乎无限的I/O带宽来进行数据的传输,不受系统带宽的影响;可以选择通过硬件的预取来降低内存的延迟;自动生成细粒度的门控时钟可以实现功耗的降低;可以通过FLIX来实现指令的并行。

2.2.2. 兼容性

兼容性是Xtensa处理器ISA的根本,因为只有具有很强的兼容性才能很好的应用到第三方的应用软件和开发工具上去。所有的可重构、可拓展的Xtensa处理器都对主要的操作系统、调试工具以及输入校验设备兼容。同时所有版本的处理器都向上兼容,同时用户自定义的指令可以重复使用。

2.2.3. 拓展性

Xtensa处理器可以很方便的将指令无缝的添加到处理器的数据通路中。任何相关的C数据类型、软件工具链和需要的进行综合的EDA脚本都是自动生成。数据通路、相关的指令以及C数据类型都是用TIE(Tensilica Instruction Extension)语言来写的。

2.2.4. 可重构性

Xtensa处理器提供预验证的模块,当用户的设计需要时随时可以将其添加到设计中去,可以又快又好的实现所需设计。所有可重构的选项如图4所示。由图可知可重构的部分包含:在不同的应用下选用不同的DSP (HiFi DSPs for Audio/Voice/Speech,Vision P5 and P6 DSPs for Imaging and Vision,ConnX BBE16EP, BBE32EP and BBE64EP DSPs,Fusion F1 DSP,Fusion G3 DSP),实现DSP的重构;多重自定义长度的GPIO ports对外设进行控制和监测;Queue中的接口宽度可选择;32位乘法器与16位的乘法器和MAC;单精度/双精度,标量/矢量浮点数模块的选择;对于VLIW和一般的指令可以通过三路64位的FLIX实现交叉存取。

图4 Xtensa LX7 处理器最大范围的可重构选项

2.2.5. 其他性能

高低字节排序的可选择;1或2个通用的load/store unit,每个的尺寸为32-,64-,128-,256-,512-bits可选;1-32个输入可选择输入buffer; 多重自定义长度的接口是数据通过FIFO进出;FLIX的长度可选,最高128bits;数据和指定的Cache采用4路组相连,最大为128K,运用write-back和write-through的cache写入协议;可选择的对本地内存的奇偶校验和ECC。

动态功耗和漏电流功耗较小;通过中断控制来进行片上调试;可选择的16位处理器ID,支持大规模并行阵列结构;支持第三方的JTAG debug probe进行片上调试的硬件。

图4 Xtensa LX7 处理器最大范围的可重构选项

2.2.5. 其他性能

高低字节排序的可选择;1或2个通用的load/store unit,每个的尺寸为32-,64-,128-,256-,512-bits可选;1-32个输入可选择输入buffer; 多重自定义长度的接口是数据通过FIFO进出;FLIX的长度可选,最高128bits;数据和指定的Cache采用4路组相连,最大为128K,运用write-back和write-through的cache写入协议;可选择的对本地内存的奇偶校验和ECC。

动态功耗和漏电流功耗较小;通过中断控制来进行片上调试;可选择的16位处理器ID,支持大规模并行阵列结构;支持第三方的JTAG debug probe进行片上调试的硬件。

图5 Xtensa LX7处理器提供的添加用户定义的功能和接口的思想

3.3. 通过FLIX进行并行操作

由图5可知,用户自定义功能的实现是通过FLIX。FLIX结构使得Xtensa LX7处理器称为一个VLIW处理器,如果需要可以实现2-30的并行。FLIX指令的长度为4bytes到16bytes之间的任意值。这种可变长度的FLIX指令可以与Xtensa处理器标准的16/32 bits指令无缝混合,所以不会有模式转换上的损失。图6展示了用户使用FLIX创造VLIW进行2-30级的并行操作

通过FLIX(可变长度指令字)Xtensa处理器可以除去在使用VLIW时指令寄存器的冗余损失。事实上,使用FLIX的Xtensa可以同时提供高性能和晓得代码长度。使用FLIX的损失是很小的,只是增加了2000个门用来进行指令的控制和译码,但是带来的好处是很大的。

Xtensa的C/C++编译器自动的从源代码中提取出并行操作并将多种操作加到FLIX中,所以即使不通过额外的软件资源同样可以获得并行计算好处。通过这种方法,一个three-issue的Xtensa LX7处理器在一个较低的频率下运行也可以达到对应其他设备在相当高时钟频率下的性能。

图5 Xtensa LX7处理器提供的添加用户定义的功能和接口的思想

3.3. 通过FLIX进行并行操作

由图5可知,用户自定义功能的实现是通过FLIX。FLIX结构使得Xtensa LX7处理器称为一个VLIW处理器,如果需要可以实现2-30的并行。FLIX指令的长度为4bytes到16bytes之间的任意值。这种可变长度的FLIX指令可以与Xtensa处理器标准的16/32 bits指令无缝混合,所以不会有模式转换上的损失。图6展示了用户使用FLIX创造VLIW进行2-30级的并行操作

通过FLIX(可变长度指令字)Xtensa处理器可以除去在使用VLIW时指令寄存器的冗余损失。事实上,使用FLIX的Xtensa可以同时提供高性能和晓得代码长度。使用FLIX的损失是很小的,只是增加了2000个门用来进行指令的控制和译码,但是带来的好处是很大的。

Xtensa的C/C++编译器自动的从源代码中提取出并行操作并将多种操作加到FLIX中,所以即使不通过额外的软件资源同样可以获得并行计算好处。通过这种方法,一个three-issue的Xtensa LX7处理器在一个较低的频率下运行也可以达到对应其他设备在相当高时钟频率下的性能。

图6. 用户使用FLIX创造VLIW进行2-30级的并行操作

还有关于接口的可重构方法,以及对应的软件部分由同组其他成员调研,在此不做讲解。

图6. 用户使用FLIX创造VLIW进行2-30级的并行操作

还有关于接口的可重构方法,以及对应的软件部分由同组其他成员调研,在此不做讲解。