`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2017/08/18 15:20:41

// Design Name:

// Module Name: devided

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module devided(

clk,

rst_n,

a,

b,

result,

remainder

);

input clk;

input rst_n;

input [15:0] a; // 被除数

input [7:0] b; //除数

output reg [15:0] result; // 商

output [7:0] remainder;//余数

reg [22:0] mid_a ;

reg [2:0] state;

reg [6:0] diff;

reg [4:0] cnt;

always@(posedge clk or negedge rst_n) begin

if(!rst_n)begin

mid_a <= {7'd0,a};

state <= 3'd0;

result <= 16'd0;

diff <= 7'd0;

cnt <= 5'd0;

end

else if( cnt == 5'd16) begin

mid_a <= mid_a;

state <= state ;

result <= result ;

diff <= diff ;

cnt <= cnt;

end

else

case(state)

3'd0:begin

if(mid_a[22:15] < b)begin

state <= 3'd2;

end

else begin

state <= 3'd1;

end

end

3'd1:begin

result <= { result[14:0], 1'd1};

diff <= mid_a[22:15] - b;

state <= 3'd3;

end

3'd2:begin

result <= { result[14:0], 1'd0};

state <= 3'd4;

end

3'd3:begin

mid_a <= { diff,mid_a[14:0],1'd0};

cnt <= cnt + 5'd1;

state <= 3'd0;

end

3'd4:begin

if(mid_a[22]) begin

result <= { result[14:0], 1'd1};

diff <= mid_a[22:14] - b;

cnt <= cnt +5'd1;

state <= 3'd3;

end

else begin

diff <= mid_a[21:15];

state <= 3'd3;

end

end

// 3'd4:begin

// if( ! mid_a)

// result << 1;

// else

// result <= result;

// end

default: state <= 3'd0;

endcase

end

assign remainder = diff;

endmodule

工程所用算法:计算时先将计算的被除数向前扩展7位,随后由高位向低位逐8位递减,滚动记录差值。

首先被减数16位在前边拼接7位0,拼接后不会改变被除数的大小,而且方便向下操作。拼接后将此23位数称为mid。之后取mid的高8位与除数作比较,若大于除数,则减去除数,结果低位拼接一。若小于除数,则验证最高位是不是0,若是则左移一位,结果拼接0.若不是则用高九位减去除数,结果拼接两个0.然后将差和后15位以及末尾一个0拼接,实现结果循环向前。在计算的同时用计数器计数来确定运行到的位数。在进行以上操作,最终得到结果。

实际算法和平常做除法竖式原理相同,只是为了速度将一些操作合并在同一时刻进行,加快了运算速度。资源利用表

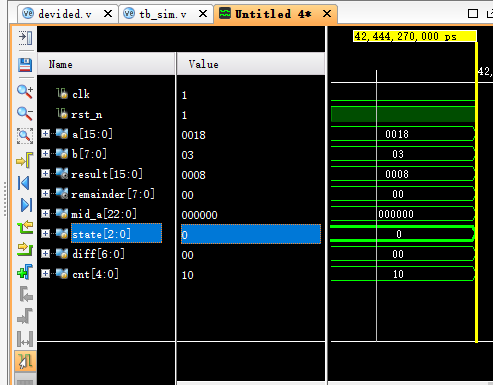

仿真图state为状态机的转移状态,被除数a为24,b为3,当状态机运行结束时得到答案8.即result。余数remainder为0.运算正确。

仿真图state为状态机的转移状态,被除数a为24,b为3,当状态机运行结束时得到答案8.即result。余数remainder为0.运算正确。