在嵌入式系统设计过程中,由于主控芯片(如ARM、PPC、MIPS等)片上的存储空间不够大,经常需要外接存储器芯片(如ROM、SRAM、SDRAM、DDR2、Nand Flash等),因此,弄清楚主控芯片与外界存储芯片的引脚连接原理至关重要,由于Nand Flash的引脚连接比较简单,不涉及地址线的连接,而SDRAM和DDR2访问原理与ROM和SRAM有一些不同,故以后再专门讲述,这里我将主要介绍ARM与ROM、SRAM这两种存储芯片的连接。

首先,我们看一个电路图。

这个电路图为三星公司的ARM芯片s3c2440与1片128KB的SRAM芯片的连接原理图。其中,SRAM芯片的引脚与图中芯片方框图中所标示,而ARM芯片的引脚则为导线上的标号。

初学者可能会有几个疑问,为什么SRAM芯片的A0地址引脚连接的是ARM芯片的A1引脚呢?那什么情况下SRAM芯片的A0连接ARM芯片的A0引脚呢?

首先,我们分析一下图中的 SRAM芯片,该芯片有A0~A15一共16根地址线,有D0~D15一共16根数据线,故其存储空间为 2^16 * 16 bit = 2^17 * 8 bit = 2^17 byte = 128KB

我们知道,要寻址 128KB 需要 17 根地址线(128 = 2^17 ),然而SRAM芯片的地址引脚却只有16根,ARM端该如何给地址线呢?

由图可以看出,SRAM芯片的数据总线是16位宽,即一次传输2个字节的数据。因此,我们可以这样理解,即一个地址空间其实对应着2个字节的数据,实际上真正的寻址空间只有64KB而已,16根地址线足够。这样ARM端并不需要将17根地址线全部连接到SRAM芯片上,只需要给出高16位地址(A1~A16),然后,SRAM芯片即根据这16根地址找到对应的地址空间,将该地址空间的2个字节发送到数据总线上,然后ARM端根据未连接到SRAM芯片的A0的电平,来决定具体是取高字节,还是低字节。

由这些分析可以推出一个规律,即 ARM端的地址线到底是 A0 、A1 还是 A2 连接 存储芯片的 A0,取决于存储系统的数据总线位宽,如果是 8位则A0->A0,如果是16位则A1->A0,如果是32位则A2->A0。

大致搞清楚了上面的原理后,ARM与存储芯片的连接方法也就很清晰了,下面给几张分别描述了各种情况下的ARM与存储芯片的连接示意图(截取自s3c2440的datasheet)。

这个电路图为三星公司的ARM芯片s3c2440与1片128KB的SRAM芯片的连接原理图。其中,SRAM芯片的引脚与图中芯片方框图中所标示,而ARM芯片的引脚则为导线上的标号。

初学者可能会有几个疑问,为什么SRAM芯片的A0地址引脚连接的是ARM芯片的A1引脚呢?那什么情况下SRAM芯片的A0连接ARM芯片的A0引脚呢?

首先,我们分析一下图中的 SRAM芯片,该芯片有A0~A15一共16根地址线,有D0~D15一共16根数据线,故其存储空间为 2^16 * 16 bit = 2^17 * 8 bit = 2^17 byte = 128KB

我们知道,要寻址 128KB 需要 17 根地址线(128 = 2^17 ),然而SRAM芯片的地址引脚却只有16根,ARM端该如何给地址线呢?

由图可以看出,SRAM芯片的数据总线是16位宽,即一次传输2个字节的数据。因此,我们可以这样理解,即一个地址空间其实对应着2个字节的数据,实际上真正的寻址空间只有64KB而已,16根地址线足够。这样ARM端并不需要将17根地址线全部连接到SRAM芯片上,只需要给出高16位地址(A1~A16),然后,SRAM芯片即根据这16根地址找到对应的地址空间,将该地址空间的2个字节发送到数据总线上,然后ARM端根据未连接到SRAM芯片的A0的电平,来决定具体是取高字节,还是低字节。

由这些分析可以推出一个规律,即 ARM端的地址线到底是 A0 、A1 还是 A2 连接 存储芯片的 A0,取决于存储系统的数据总线位宽,如果是 8位则A0->A0,如果是16位则A1->A0,如果是32位则A2->A0。

大致搞清楚了上面的原理后,ARM与存储芯片的连接方法也就很清晰了,下面给几张分别描述了各种情况下的ARM与存储芯片的连接示意图(截取自s3c2440的datasheet)。

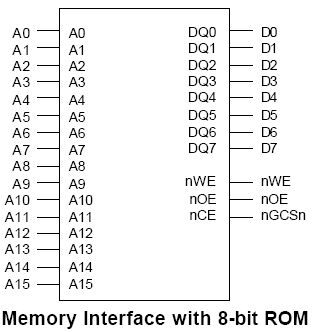

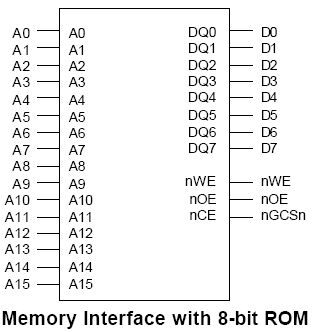

【说明】:上图的ROM为 2^16 x 8 bit = 64KB ,由于数据总线为8位宽,故一个地址空间对应着1个字节,故ARM端的A0连接ROM的A0

【说明】:上图的ROM为 2^16 x 8 bit = 64KB ,由于数据总线为8位宽,故一个地址空间对应着1个字节,故ARM端的A0连接ROM的A0

【说明】:上图中,由两片8位宽64KB的ROM构成了一个16位宽的存储系统。

【说明】:上图中,由两片8位宽64KB的ROM构成了一个16位宽的存储系统。

【说明】:上图中,由四片8位宽的ROM构成了一个32位宽的存储系统。

【说明】:上图中,由四片8位宽的ROM构成了一个32位宽的存储系统。

那么,留一个小问题供大家思考,如果将ARM的A0~A15引脚连接一个16位宽的SRAM的A0~A15引脚,会发生什么现象?

注,本文讨论的ARM芯片是没有类似SDRAM Controller这样的存储器控制器的ARM芯片,对于有类似SDRAM Controller模块的ARM芯片,它会根据寄存器配置的外接DDR芯片数据位宽,在硬件上将ARM的地址线引脚进行的左移操作,例如当数据位宽为16位时,硬件上将ARM的A1脚的电平移至A0,依次类推。所以,这样的ARM芯片不需要根据本文的方法连接,而直接将ARM端的A0~Ax 连接到存储器的 A0~Ax 即可。

后记:最近研究了一下嵌入式存储系统,包括SRAM,SDRAM,DDR2等,准备写几篇总结的文章,本文为第一篇,简单讲述了一下SRAM和ROM芯片与ARM的地址线连接,如果有写得不清楚或者不正确的地方,希望各位不吝赐教,留言或者发送邮件到lujun.hust@gmail.com探讨。

本文出自 “对影成三人” 博客,非常感谢他, 原文出处http://ticktick.blog.51cto.com/823160/686049

那么,留一个小问题供大家思考,如果将ARM的A0~A15引脚连接一个16位宽的SRAM的A0~A15引脚,会发生什么现象?

注,本文讨论的ARM芯片是没有类似SDRAM Controller这样的存储器控制器的ARM芯片,对于有类似SDRAM Controller模块的ARM芯片,它会根据寄存器配置的外接DDR芯片数据位宽,在硬件上将ARM的地址线引脚进行的左移操作,例如当数据位宽为16位时,硬件上将ARM的A1脚的电平移至A0,依次类推。所以,这样的ARM芯片不需要根据本文的方法连接,而直接将ARM端的A0~Ax 连接到存储器的 A0~Ax 即可。

后记:最近研究了一下嵌入式存储系统,包括SRAM,SDRAM,DDR2等,准备写几篇总结的文章,本文为第一篇,简单讲述了一下SRAM和ROM芯片与ARM的地址线连接,如果有写得不清楚或者不正确的地方,希望各位不吝赐教,留言或者发送邮件到lujun.hust@gmail.com探讨。

本文出自 “对影成三人” 博客,非常感谢他, 原文出处http://ticktick.blog.51cto.com/823160/686049

这个电路图为三星公司的ARM芯片s3c2440与1片128KB的SRAM芯片的连接原理图。其中,SRAM芯片的引脚与图中芯片方框图中所标示,而ARM芯片的引脚则为导线上的标号。

初学者可能会有几个疑问,为什么SRAM芯片的A0地址引脚连接的是ARM芯片的A1引脚呢?那什么情况下SRAM芯片的A0连接ARM芯片的A0引脚呢?

首先,我们分析一下图中的 SRAM芯片,该芯片有A0~A15一共16根地址线,有D0~D15一共16根数据线,故其存储空间为 2^16 * 16 bit = 2^17 * 8 bit = 2^17 byte = 128KB

我们知道,要寻址 128KB 需要 17 根地址线(128 = 2^17 ),然而SRAM芯片的地址引脚却只有16根,ARM端该如何给地址线呢?

由图可以看出,SRAM芯片的数据总线是16位宽,即一次传输2个字节的数据。因此,我们可以这样理解,即一个地址空间其实对应着2个字节的数据,实际上真正的寻址空间只有64KB而已,16根地址线足够。这样ARM端并不需要将17根地址线全部连接到SRAM芯片上,只需要给出高16位地址(A1~A16),然后,SRAM芯片即根据这16根地址找到对应的地址空间,将该地址空间的2个字节发送到数据总线上,然后ARM端根据未连接到SRAM芯片的A0的电平,来决定具体是取高字节,还是低字节。

由这些分析可以推出一个规律,即 ARM端的地址线到底是 A0 、A1 还是 A2 连接 存储芯片的 A0,取决于存储系统的数据总线位宽,如果是 8位则A0->A0,如果是16位则A1->A0,如果是32位则A2->A0。

大致搞清楚了上面的原理后,ARM与存储芯片的连接方法也就很清晰了,下面给几张分别描述了各种情况下的ARM与存储芯片的连接示意图(截取自s3c2440的datasheet)。

这个电路图为三星公司的ARM芯片s3c2440与1片128KB的SRAM芯片的连接原理图。其中,SRAM芯片的引脚与图中芯片方框图中所标示,而ARM芯片的引脚则为导线上的标号。

初学者可能会有几个疑问,为什么SRAM芯片的A0地址引脚连接的是ARM芯片的A1引脚呢?那什么情况下SRAM芯片的A0连接ARM芯片的A0引脚呢?

首先,我们分析一下图中的 SRAM芯片,该芯片有A0~A15一共16根地址线,有D0~D15一共16根数据线,故其存储空间为 2^16 * 16 bit = 2^17 * 8 bit = 2^17 byte = 128KB

我们知道,要寻址 128KB 需要 17 根地址线(128 = 2^17 ),然而SRAM芯片的地址引脚却只有16根,ARM端该如何给地址线呢?

由图可以看出,SRAM芯片的数据总线是16位宽,即一次传输2个字节的数据。因此,我们可以这样理解,即一个地址空间其实对应着2个字节的数据,实际上真正的寻址空间只有64KB而已,16根地址线足够。这样ARM端并不需要将17根地址线全部连接到SRAM芯片上,只需要给出高16位地址(A1~A16),然后,SRAM芯片即根据这16根地址找到对应的地址空间,将该地址空间的2个字节发送到数据总线上,然后ARM端根据未连接到SRAM芯片的A0的电平,来决定具体是取高字节,还是低字节。

由这些分析可以推出一个规律,即 ARM端的地址线到底是 A0 、A1 还是 A2 连接 存储芯片的 A0,取决于存储系统的数据总线位宽,如果是 8位则A0->A0,如果是16位则A1->A0,如果是32位则A2->A0。

大致搞清楚了上面的原理后,ARM与存储芯片的连接方法也就很清晰了,下面给几张分别描述了各种情况下的ARM与存储芯片的连接示意图(截取自s3c2440的datasheet)。

【说明】:上图的ROM为 2^16 x 8 bit = 64KB ,由于数据总线为8位宽,故一个地址空间对应着1个字节,故ARM端的A0连接ROM的A0

【说明】:上图的ROM为 2^16 x 8 bit = 64KB ,由于数据总线为8位宽,故一个地址空间对应着1个字节,故ARM端的A0连接ROM的A0

【说明】:上图中,由两片8位宽64KB的ROM构成了一个16位宽的存储系统。

【说明】:上图中,由两片8位宽64KB的ROM构成了一个16位宽的存储系统。

【说明】:上图中,由四片8位宽的ROM构成了一个32位宽的存储系统。

【说明】:上图中,由四片8位宽的ROM构成了一个32位宽的存储系统。

那么,留一个小问题供大家思考,如果将ARM的A0~A15引脚连接一个16位宽的SRAM的A0~A15引脚,会发生什么现象?

注,本文讨论的ARM芯片是没有类似SDRAM Controller这样的存储器控制器的ARM芯片,对于有类似SDRAM Controller模块的ARM芯片,它会根据寄存器配置的外接DDR芯片数据位宽,在硬件上将ARM的地址线引脚进行的左移操作,例如当数据位宽为16位时,硬件上将ARM的A1脚的电平移至A0,依次类推。所以,这样的ARM芯片不需要根据本文的方法连接,而直接将ARM端的A0~Ax 连接到存储器的 A0~Ax 即可。

后记:最近研究了一下嵌入式存储系统,包括SRAM,SDRAM,DDR2等,准备写几篇总结的文章,本文为第一篇,简单讲述了一下SRAM和ROM芯片与ARM的地址线连接,如果有写得不清楚或者不正确的地方,希望各位不吝赐教,留言或者发送邮件到lujun.hust@gmail.com探讨。

本文出自 “对影成三人” 博客,非常感谢他, 原文出处http://ticktick.blog.51cto.com/823160/686049

那么,留一个小问题供大家思考,如果将ARM的A0~A15引脚连接一个16位宽的SRAM的A0~A15引脚,会发生什么现象?

注,本文讨论的ARM芯片是没有类似SDRAM Controller这样的存储器控制器的ARM芯片,对于有类似SDRAM Controller模块的ARM芯片,它会根据寄存器配置的外接DDR芯片数据位宽,在硬件上将ARM的地址线引脚进行的左移操作,例如当数据位宽为16位时,硬件上将ARM的A1脚的电平移至A0,依次类推。所以,这样的ARM芯片不需要根据本文的方法连接,而直接将ARM端的A0~Ax 连接到存储器的 A0~Ax 即可。

后记:最近研究了一下嵌入式存储系统,包括SRAM,SDRAM,DDR2等,准备写几篇总结的文章,本文为第一篇,简单讲述了一下SRAM和ROM芯片与ARM的地址线连接,如果有写得不清楚或者不正确的地方,希望各位不吝赐教,留言或者发送邮件到lujun.hust@gmail.com探讨。

本文出自 “对影成三人” 博客,非常感谢他, 原文出处http://ticktick.blog.51cto.com/823160/686049