这部分将参看相关的毕业论文设计来讲一下 DM368 的硬件部分。参看:相关论文扩展:TechV-DM365开发板使用说明书基于 DM368 的高清视频监控系统设计与实现 -- 文波

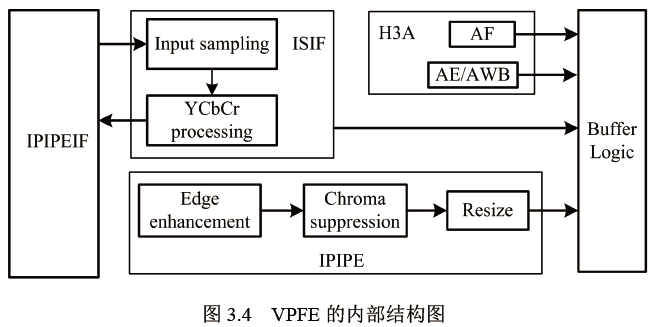

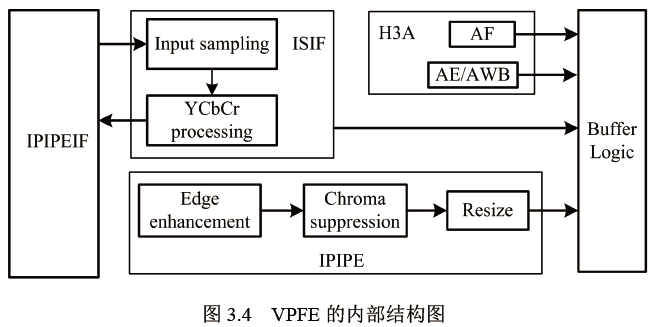

视频处理前端VPFE 提供了ISIF 和CMOS 图像传感器和视频解码器接口,主要负责处理不同图像视频传感器设备采集的图像数据。VPFE 支持的格式包含以下几种:原始视频RAW 格式、通用视频YCbCr 格式以及ITU BT.656/BT.1120 格式。视频处理前端VPFE 的内部结构图如图3.4 所示。

从图中可知,VPFE 包含以下4 个模块:

(1)图像信号接口ISIF(Image Signal Interface)

ISIF 主要提供了两种接口,分别为图像传感器接口和数字视频源接口。图像传感器接口主要接受图像传感器(CCD/CMOS) 输出的 Bayer 格式的 RAW 原始数据,数字视频源接口主要接受视频解码器输出的多种 YUV 数据。ISIF 支持 master 主模式和 slave 从模式两种工作状态,在 master 模式下图像的 PCLK、VD 和HD 信号由 DM368 向外发出,而 salve 模式下由外部设备提供 PCLK、VD 和HD 信号给 DM368,在大多数的实际应用中采用slave 模式。

(2)图像管道接口IPIPEIF(Image Pipe Interface)

IPIPEIF 是图像信号接口 ISIF 和图像管道 IPIPE 之间的图像同步信号和数据接口,可以接受图像传感器输入的并行数据、ISIF 和 SDRAM 的数据,根据需要对这些数据进行预处理后传送到 ISIF 和 IPIPE。预处理包括对图像信号PCLK、HD 和VD 的重新调整使得进入到 ISIF 和 IPIPE 中的图像像素大小符合要求。(3)图像管道IPIPE(Image Pipe)

IPIPE 是一个参数化的硬件处理模块[37],通过参数设置可以将 CCD/CMOS 输出的 RAW 原始数据转换成 YCbCr4:2:2 格式或 YCbCr4:2:0 格式,同时还可以显示视频帧率和记录视频。此外,IPIPE 还内置了一个Resizer(缩放器)模块,主要完成对图像缩放和图像存储格式的转换,如在 resize-only 模式下,可对 YCbCr 格式的数据进行16 位调谐。IPIPE 还具有一些额外的统计采集功能:直方图、边缘信号计算、运动矢量补偿等。

(4)硬件3A(H3A)

硬件 3A 是指自动对焦 AF(Atto Focus)、自动白平衡 AWB(Auto White Balance)和自动曝光 AE(Automatic Exposure)。它并不直接影响输入的图像原始数据信息,而是通过收集来自 ISIF 图像信号接口输入的原始图像/视频数据的信息进行统计来控制自动对焦、自动白平衡和自动曝光。自动对焦 AF 引擎实现对输入的原始图像/视频数据提

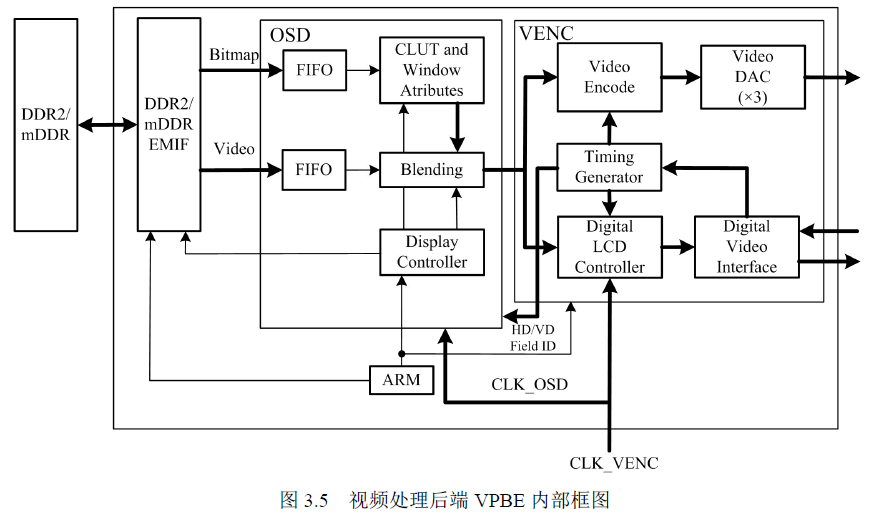

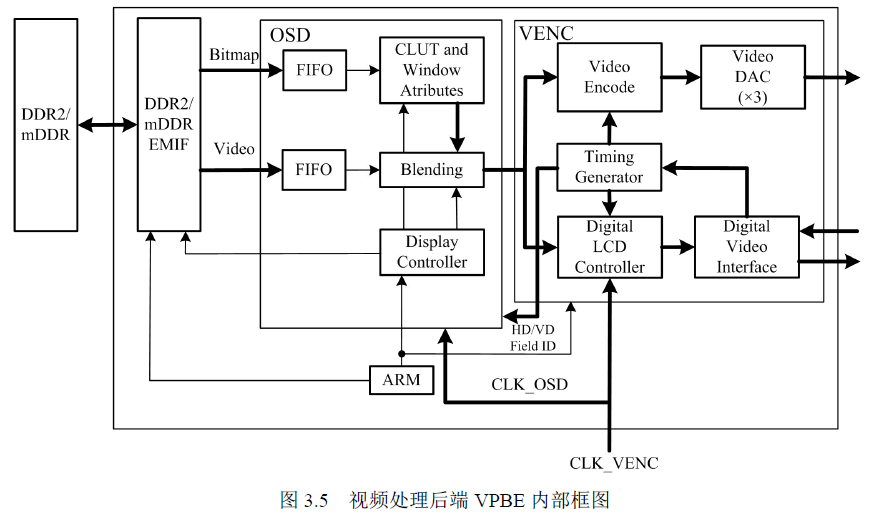

取和过滤每个绿 {MOD}像素,并对任一指定区域内的数据提供累加值或峰值数据。当使用自动对焦引擎时,指定区域是一个二维数据块,被称为一个 paxel。AWB/AE 引擎对视频数据进行子采样后提供累加值和检查饱和值。当使用AE/AWB 时,二维数据块称为一个窗口,AF Paxels 和 AE/AWB 窗口的数量、尺寸和位置均可以编程进行调节。视频处理后端 VPBE 包括屏幕时控系统 OSD 和视频编码器 VENC 两大模块,如图 3.5 所示。

1.屏幕视控系统OSD

OSD 主要任务是将外部DDR2/mDDR 里的视频和显示数据读取出来并将其转换为YCbCr 格式,然后传送给视频编码器VENC。OSD 同时管理不同数据格式的显示,不同显示窗口的数据需要混合成单个的显示帧,并转换为YUV 显示数据。窗口显示使用固定的显示优先级和可选的混合或透明规则将多个窗口混合起来。OSD 具有5 层窗户,分别为:CURSOR、OSDWIN1、OSDWIN0、VIDWIN1、VIDWIN0,优先级依次递减。若VIDWIN0 和VIDWIN1 窗口同时显示,可以在视频中呈现画中画的效果。而VIDWIN0窗口单独显示则为HD 显示效果。OSDWIN0 和OSDWIN1 作为位图窗口,允许用户在显示单元上显示图形或图标OSDWIN1 同时也可以定义为OSDWIN0 的属性窗口,可以与OSDWIN0 进行逐个像素混合。

2.视频数据编码VENC 和数字LCD 控制器

视频编码模块VENC 主要是对OSD 的显示帧转化成所期望的输出格式和信号,其内部集成了3 个通道HD 视频DAC 和单通道SD 视频缓冲,主要产生包括D/A 转化在内的模拟视频输出:SDTV 和HDTV。SDTV 支持的格式有composite NTSC-M、RGB、PAL-B/D/G/H/I 、component YPbPr 、S-Video ( Y/S )。HDTV 支持的格式有高清525p/625p/720p/1080i、RGB、componentYPbPr。数字LCD 控制器产生数字RGB/YCbCr 格式输出,支持多种数字LCD 显示格式和标准数字YUV 输出,可连接高清视频编码器或DVI/HDMI 接口设备。

(1)图像信号输入接口ISIF,支持CCD/CMOS。

(2)音频信号输入输出接口。

(3)模拟视频输出接口。

(4)存储器模块接口。

(5)DDR2/mDDR 模块接口。

(6)10/100Mbps/s 以太网网络接口。

(7)2 路UARTS 接口。

(8)5 路SPI 接口。

(9)2 路MMC/SD/SDIO。

(10)时钟模块25MHz 网络时钟,12.288MHz 音频时钟,14.31818MHz 和27MHz

视频时钟,32.768MHzRTC 时钟,24MHzDM368 时钟。

(11) 电源与复位模块

从以上三种异步存储器的优缺点并结合系统未来上层开发对存储器容量的需求,系统选用NAND FLASH 作为外部存储器。NAND FLASH 芯片采用Micron 公司生产的大小为2GB 的MT29F16G08FAAWC 芯片,主要用来存储数据,包括Uboot 启动代码、Linux操作系统、文件系统及系统运行时产生的配置文件等信息。MT29F16G08FAAWC 内部

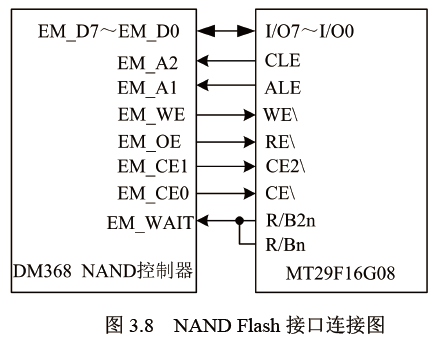

包含两片MT29F8G08FAAWC,通过片选信号CE和CE2进行片选使能。EM_D[15..0]为数据总线,本系统中NAND FLASH 选用8bit 模式,故只选用DM368 的低8 位进行地址、命令的输入以及数据输入输出。EM_A[13..0] 为DM368 的地址总线,MT29F16G08FAAWC 的ALE 和CLE 表示地址锁存信号和命令锁存信号,分别与EM_A1和EM_A2 连接。只有当ALE 和CLE 信号同时为高且在WE 信号的上升沿时,地址信号和命令信号才被锁存到内部的地址寄存器和命令寄存器。写使能信号EM_WE,上升沿有效。输出使能信号EM_OE 与FLASH 的RE 信号连接,下降沿后tREA 时间内数据有效。异步等待信号EM_WAIT 与FLASH 的R/B 信号相连,为低表示设备忙,为高表示设备已准备好。NAND Flash 与DM368 的存储器控制器连接如图3.8 所示。

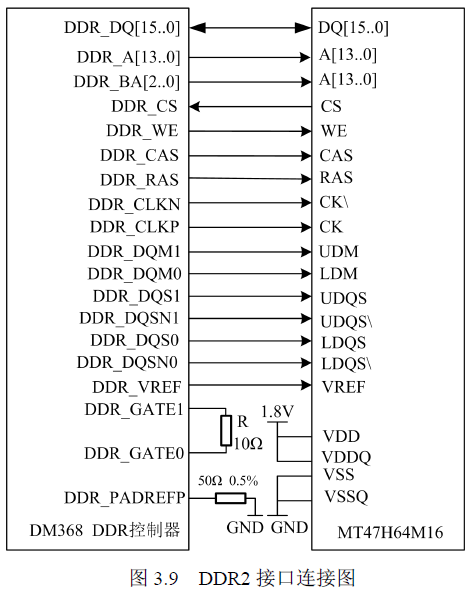

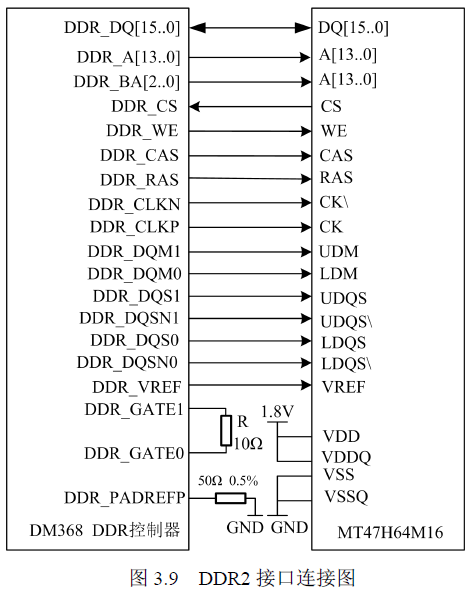

该芯片与DM368 的DDR2 存储控制器的引脚完全兼容,16 位数据线、14 位地址线和3 位块选择信号线均可以完全对应。由于采用双端差分模式的时钟信号(CKP 和CKN),该芯片同时具有高达800Mb/sde 双数据传输率,即在时钟信号CKP 的上升沿和CKN 的下降沿分别传输一次数据,即每个时钟传输2 个数据字。由于在DDR2 控制器内部没有集成与存储器终端相匹配的电阻,因此DM368 和DDR2 之间的数据线、地址线和控制线之间均需串接电阻。DDR2 中均为高速信号线,且布线密度较大,为减小布局、布线空间,设计中在不降低芯片驱动能力的情况下采用串接33 欧的等值排阻以减小信号的震荡和反射,使数据信号传输更加稳定。MT47H64M16 与DDR 控制器的连接图如图3.9 所示。

在MMC/SD 模式下,控制器支持单个或多个MMC/SD 卡,当多个卡被连接时,MMC/SD 控制器通过数据线识别广播选择其中一个。MMC/SD 控制器管脚如下:CMD:此管脚用于MMC/SD 控制器和卡之间的双向通信,MMC/SD 控制器通过此管脚传输命令给卡和存储卡驱动器的命令响应。DATA3~DATA0: MMC 卡只使用数据线DATA0 进行数据传输,SD 卡采用四根数据线进行数据传输。MMC 控制寄存器(MMCCTL)通过设置WDYH 位进行数据传输时使用的管脚数目(数据总线宽度)的设定。CLK:MMC/SD 控制器输出时钟给存储卡。

EMAC 控制模块是器件内核处理器和EMAC/MDIO 模块的主接口,其内置了8KB的内部RAM 用于保存EMAC 缓冲区中的外部操作描述符,同时其内部包含了必要的组件以使EMAC 高效使用器件内存。EMAC 模块提供高效的处理器和网络之间的通讯接口,支持半双工或全双工的10Base-T(10Mbits/s)和100BaseTX(100Mbits/s)以及全双工的100BaseT[45]。MDIO 模块可实现IEEE802.3 标准的网络协议串行管理接口,通过两线制的共享总线来查询和控制连接在器件上的PHY。通过MDIO 模块可配置物理层PHY 的参数,状态的监控和查询结果的接受,获得协商结果,配置EMAC 模块正确操作所需要的参数。

EMAC/MDIO 有以下特点:

1.同步10/100/1000Mbps 操作。

2.与物理层器件PHY 之间的G/MII 接口。

3.全双工Gbit 运行(Gbit 下不支持半双工)。

4.CRC 硬件错误处理。

5.8 个发送通道,支持Round-Robin 或固定优先级,保证数据传输服务质量。

6.8 个带有VLANtag 辨识的接受通道,保证数据接受质量。

7.可以在单个通道上选择接受广播帧和多播帧。

8.硬件数据流控制。

因DM368 内部已集成了网络的数据链路层,所以系统选用Micrel 公司生产的KS8001L 芯片实现网络的物理层协议,进而构成一个完整的网络底层。KS8001L 能够实现全部的10/100M 以太网物理层功能,工作电压为3.3V,核心电压为1.8V,内部集成了MII 接口和MDIO 配置接口。KS8001 与DM368 以太网控制模块的连接图如图3.12所示。

MII 接口包含三部分:数据接受接口(MTCLK、MTXD[3:0]、MTXEN),数据发送接口(MRCLK、MRXD[3:0]、MRXDV、MRXER),网络状态检测接口(MCOL、MCRS)。数据的发送和接受是两个独立的通道,有各自的时钟、数据和控制信号。MDIO 接口使用单独的管理数据时钟信号MDCLK,通过单根管理数据输入输出信号MDIO 实现PHY管理数据的发送和接受。

RJ-45 接口采用HR911105A 接口电路,其内部已集成了网络隔离变压器和状态指示灯,与KS8001 的6 根信号线相连:接受数据差分信号对(RX+,RX-)、发送数据差分信号对(TX+,TX-)、两个指示灯(Link 状态指示,全双工/半双工模式指示)。

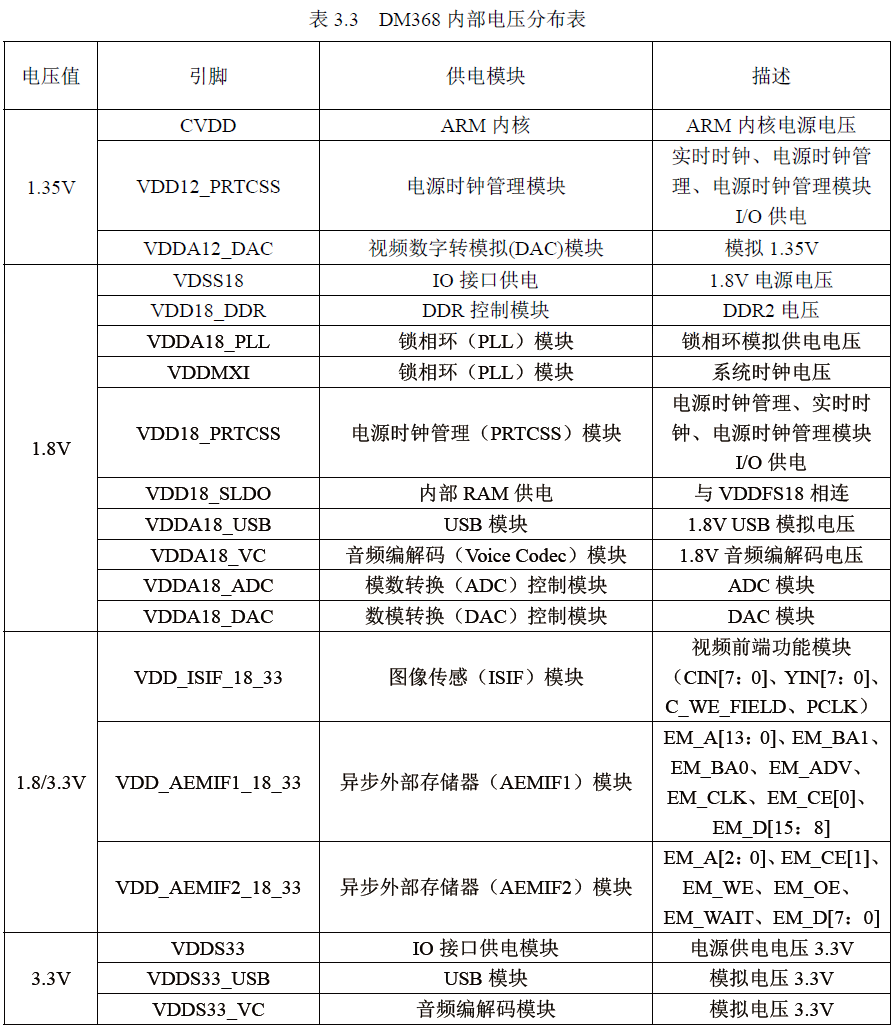

从表中可以看出,系统硬件部分共需要三种电压,分别为3.3V、1.8V 和1.35V,同时系统对DM368 芯片的的上、下电顺序有较为严格的要求,即上电顺序为先是内核电压1.35V,接着是1.8V,最后是3.3V,下电顺序与上电顺序正好相反。为了满足上述供电需求,选用TI 公司生产的电源芯片TPS3808G01 和TPS65053 进行电源设计。TPS65053 芯片的1.35V 输出端接入到TPS3808G01 芯片的使能端SENSE,作为1.8V 和3.3V 的输出使能。只有当TPS65053 输出1.35V 电压之后,才能使TPS3808G01 芯片的SENSE 端为高电平,TPS65053 的使能信号EN3V3 和EN1V8 有效,依次输出输出1.8V 和3.3V。

一、系统硬件电路详细设计

3.1 TMS320DM368 硬件平台简介

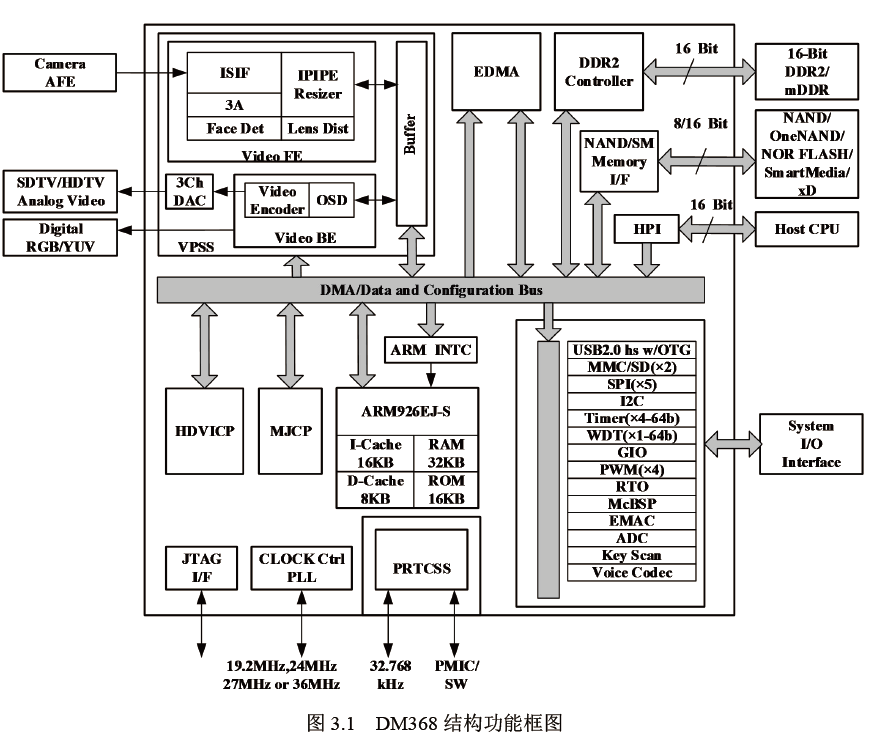

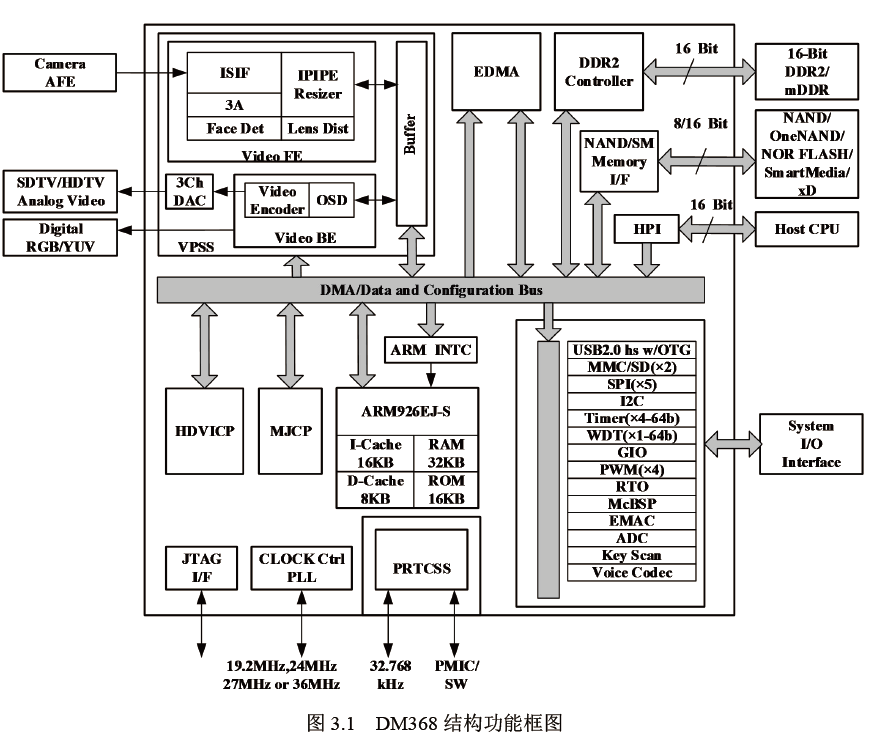

TMS320DM368 是德州仪器公司(TI)于2010 年4 月推出的新一代基于Davinci 技术的高清视频处理器,内部集成了一颗 ARM 内核和两个视频图像协处理器,同时内部还集成了一个视频处理子系统和丰富的系统外设[31]。芯片采用的 65nm 的制造工艺技术,性能稳定,成本低,单片价格约为 100RMB。ARM 内核是基于 ARM926EJ-S 的 RISC处理器,是整个 TMS320DM368 处理器的核心,执行整个系统的控制功能。两个视频图像协处理器分别为高清视频编解码处理器 HDVICP(HD Video Imagging Co-Processor)和 MJCP(MPEG-4 JPEG Co-Processor),支持 H.264、MPEG-2、MPEG-4、MJPEG 以及 VC1 等视频格式的编解码[32],HDVICP 最高可支持 1080p@30pfs 的高清视频 H.264 格式编码,MJCP 最高支持 1080p@25pfs 的 MPEG4 格式编码,功能十分强大。视频处理子系统 VPSS(Video Processing Subsystem)中包括视频处理前端 VPFE(Video Processing Front End)和视频处理后端 VPBF(Video Processing Back End)。视频处理前端包含有图像传感器接口、图像管道接口、图像管道,支持噪声过滤、视频稳定、自动白平衡、自动对焦、自动曝光、人脸检测以及边缘增强等影像增强技术,可显著提升视频处理的智能化水平[33]。视频处理后端包括屏幕显示、视频编码器和数字LCD控制器,不仅可将多个窗口的视频数据混合显示,同时还支持模拟 SDTV、数字 HDTV 和数字 LCD 等多种形式的视频输出。DM368 内部集成了多种常用的外设控制器,提供了丰富的外设接口,可实现视频编解码应用中与大多数外设器件的无缝连接。DM368的结构功能框图如图3.1 所示。

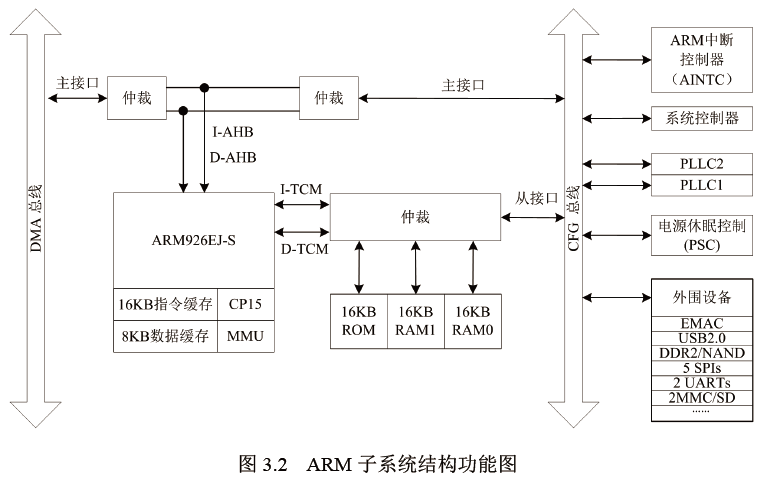

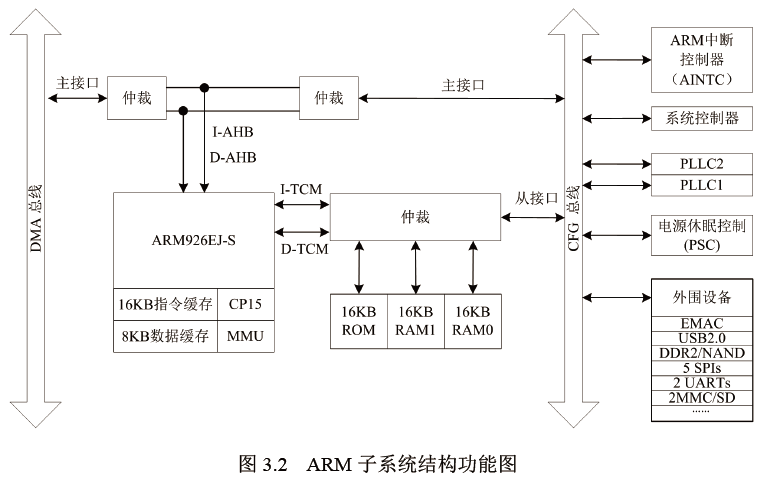

3.1.1 ARM 子系统

ARM 子系统中的核心处理器是 ARM926EJ-S,采用 32 位 RISC 精简指令集,它的主频高达 432MHz,支持 Thumb 扩展。同时内置了 16KB 的高速指令缓存、8KB 的高速数据缓存、32KB 的片内 RAM 和 16KB 的片内 ROM,内部资源非常丰富。ARM926EJ-S 可运行实时嵌入式 Linux 操作系统,最高可执行 32 位的指令和处理 32 位的数据,同时配备 Thumb 扩展。ARM 子系统主要用来管理和控制所有外设及其它子系统,并负责执行系统级的功能,如系统的初始化和设置、用户接口、用户命令执行等任务。由于处理器采用流水线操作技术,处理器和内存系统中的所有部分可以连续协同工作。ARM 核心中的系统控制协处理器 CP15 主要用于处理各种事务[34],例如配置和控制 ARM 处理器、指令和数据缓存,管理 MMU 以及控制其他一些 ARM 子系统。通过协处理器 CP15 和保护模块使得 ARM 内核体系结构得到进一步增强。ARM 核心还提供了内存管理单元 MMU(Memory Management Unit-MMU),具有查表预留缓冲区的数据和程序存储,可向 Symbian OS、Windows CE 和Linux 等操作系统提供其所需的虚拟存储,控制着虚拟地址到物理地址的转换、访问权限的检查、数据与指令对区域属性进行的访问。MMU 可进行控制逻辑访问、转换旁视缓冲区和转换表遍历硬件操作。另外,ARM 处理器通过 DMA 总线和 CFG 总线实现对各类控制器的管理,如时钟控制器、内存控制器、I2C 通信控制器、视频处理子系统等。DMA 总线负责完成各个系统和模块之间的数据传输,CFG 总线用于配置各模块的寄存器。ARM 子系统的结构功能图如图3.2 所示。

3.1.2 视频图像协处理器

DM368 内部集成了两个硬件化的视频图像协处理器:高清视频图像协处理器 HDVICP 处理器(HD Video Imagging Co-Processor)和 MJCP 处理器(MPEG-4 JPEGCo-Processor),支持包括 H.264、MPEG-4/MPEG-2、MJPEG、JPEG 等多种格式的视频压缩,最高支持 1080P,30fps 的高清视频数据压缩。硬件化的视频协处理器不仅有效的减轻了 ARM 主核在视频加速方面的压力,同时使得用户对视频压缩格式的选择提供了极大方便,能满足大多数视频压缩要求。3.1.3 视频处理子系统

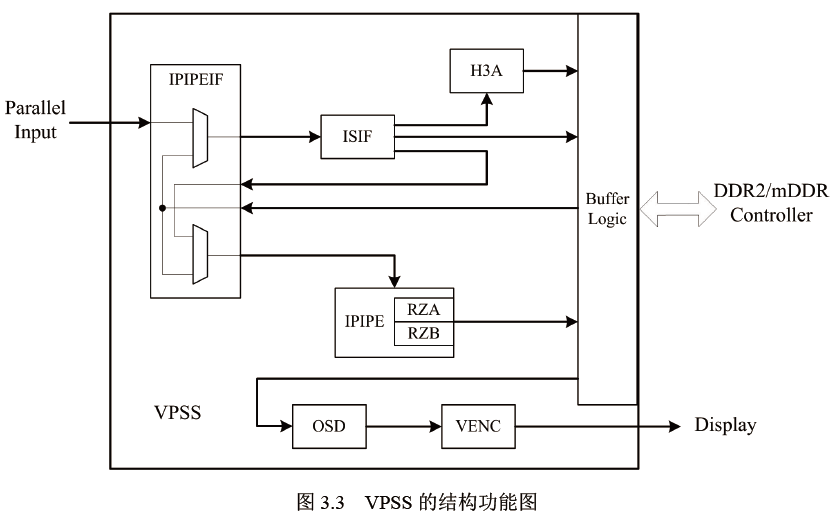

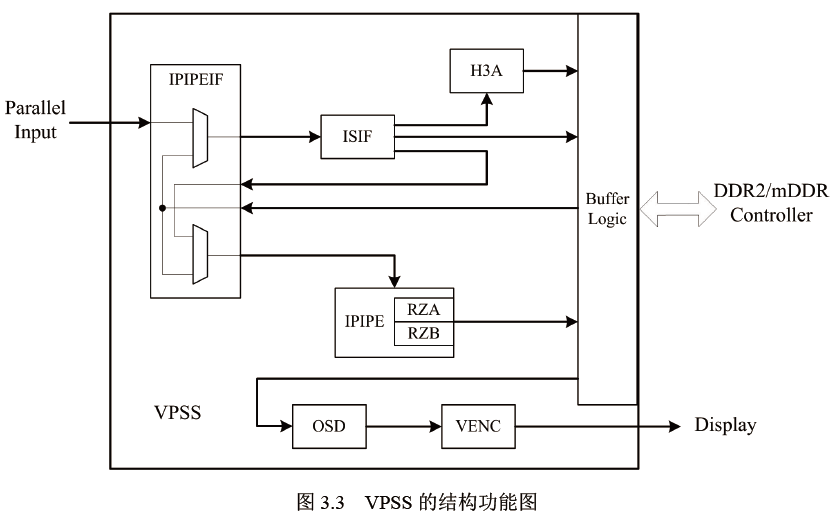

视频处理子系统 VPSS(Video Processing Subsystem)提供对输入的外部视频进行预处理的端口和对输出的压缩后的视频进行显示的端口,分别称为视频处理前端 VPFE[35](Video Processing Front End)和视频处理后端 VPBE[36](Video Processing Back End)。VPFE、VPBE 与DDR2/mDDR 控制器之间的数据传输主要依靠缓冲逻辑和 DMA 系统进行,缓冲逻辑和 DMA 系统之间通过 64 位带宽总线进行连接。VPSS 的结构功能图如图3.3 所示。

视频处理前端VPFE 提供了ISIF 和CMOS 图像传感器和视频解码器接口,主要负责处理不同图像视频传感器设备采集的图像数据。VPFE 支持的格式包含以下几种:原始视频RAW 格式、通用视频YCbCr 格式以及ITU BT.656/BT.1120 格式。视频处理前端VPFE 的内部结构图如图3.4 所示。

从图中可知,VPFE 包含以下4 个模块:

(1)图像信号接口ISIF(Image Signal Interface)

ISIF 主要提供了两种接口,分别为图像传感器接口和数字视频源接口。图像传感器接口主要接受图像传感器(CCD/CMOS) 输出的 Bayer 格式的 RAW 原始数据,数字视频源接口主要接受视频解码器输出的多种 YUV 数据。ISIF 支持 master 主模式和 slave 从模式两种工作状态,在 master 模式下图像的 PCLK、VD 和HD 信号由 DM368 向外发出,而 salve 模式下由外部设备提供 PCLK、VD 和HD 信号给 DM368,在大多数的实际应用中采用slave 模式。

(2)图像管道接口IPIPEIF(Image Pipe Interface)

IPIPEIF 是图像信号接口 ISIF 和图像管道 IPIPE 之间的图像同步信号和数据接口,可以接受图像传感器输入的并行数据、ISIF 和 SDRAM 的数据,根据需要对这些数据进行预处理后传送到 ISIF 和 IPIPE。预处理包括对图像信号PCLK、HD 和VD 的重新调整使得进入到 ISIF 和 IPIPE 中的图像像素大小符合要求。(3)图像管道IPIPE(Image Pipe)

IPIPE 是一个参数化的硬件处理模块[37],通过参数设置可以将 CCD/CMOS 输出的 RAW 原始数据转换成 YCbCr4:2:2 格式或 YCbCr4:2:0 格式,同时还可以显示视频帧率和记录视频。此外,IPIPE 还内置了一个Resizer(缩放器)模块,主要完成对图像缩放和图像存储格式的转换,如在 resize-only 模式下,可对 YCbCr 格式的数据进行16 位调谐。IPIPE 还具有一些额外的统计采集功能:直方图、边缘信号计算、运动矢量补偿等。

(4)硬件3A(H3A)

硬件 3A 是指自动对焦 AF(Atto Focus)、自动白平衡 AWB(Auto White Balance)和自动曝光 AE(Automatic Exposure)。它并不直接影响输入的图像原始数据信息,而是通过收集来自 ISIF 图像信号接口输入的原始图像/视频数据的信息进行统计来控制自动对焦、自动白平衡和自动曝光。自动对焦 AF 引擎实现对输入的原始图像/视频数据提

取和过滤每个绿 {MOD}像素,并对任一指定区域内的数据提供累加值或峰值数据。当使用自动对焦引擎时,指定区域是一个二维数据块,被称为一个 paxel。AWB/AE 引擎对视频数据进行子采样后提供累加值和检查饱和值。当使用AE/AWB 时,二维数据块称为一个窗口,AF Paxels 和 AE/AWB 窗口的数量、尺寸和位置均可以编程进行调节。视频处理后端 VPBE 包括屏幕时控系统 OSD 和视频编码器 VENC 两大模块,如图 3.5 所示。

1.屏幕视控系统OSD

OSD 主要任务是将外部DDR2/mDDR 里的视频和显示数据读取出来并将其转换为YCbCr 格式,然后传送给视频编码器VENC。OSD 同时管理不同数据格式的显示,不同显示窗口的数据需要混合成单个的显示帧,并转换为YUV 显示数据。窗口显示使用固定的显示优先级和可选的混合或透明规则将多个窗口混合起来。OSD 具有5 层窗户,分别为:CURSOR、OSDWIN1、OSDWIN0、VIDWIN1、VIDWIN0,优先级依次递减。若VIDWIN0 和VIDWIN1 窗口同时显示,可以在视频中呈现画中画的效果。而VIDWIN0窗口单独显示则为HD 显示效果。OSDWIN0 和OSDWIN1 作为位图窗口,允许用户在显示单元上显示图形或图标OSDWIN1 同时也可以定义为OSDWIN0 的属性窗口,可以与OSDWIN0 进行逐个像素混合。

2.视频数据编码VENC 和数字LCD 控制器

视频编码模块VENC 主要是对OSD 的显示帧转化成所期望的输出格式和信号,其内部集成了3 个通道HD 视频DAC 和单通道SD 视频缓冲,主要产生包括D/A 转化在内的模拟视频输出:SDTV 和HDTV。SDTV 支持的格式有composite NTSC-M、RGB、PAL-B/D/G/H/I 、component YPbPr 、S-Video ( Y/S )。HDTV 支持的格式有高清525p/625p/720p/1080i、RGB、componentYPbPr。数字LCD 控制器产生数字RGB/YCbCr 格式输出,支持多种数字LCD 显示格式和标准数字YUV 输出,可连接高清视频编码器或DVI/HDMI 接口设备。

3.1.4 丰富的外设接口

DM368 还提供了以下丰富的外设接口:(1)图像信号输入接口ISIF,支持CCD/CMOS。

(2)音频信号输入输出接口。

(3)模拟视频输出接口。

(4)存储器模块接口。

(5)DDR2/mDDR 模块接口。

(6)10/100Mbps/s 以太网网络接口。

(7)2 路UARTS 接口。

(8)5 路SPI 接口。

(9)2 路MMC/SD/SDIO。

(10)时钟模块25MHz 网络时钟,12.288MHz 音频时钟,14.31818MHz 和27MHz

视频时钟,32.768MHzRTC 时钟,24MHzDM368 时钟。

(11) 电源与复位模块

3.2 视频输入输出接口设计

3.2.1 视频输入接口设计

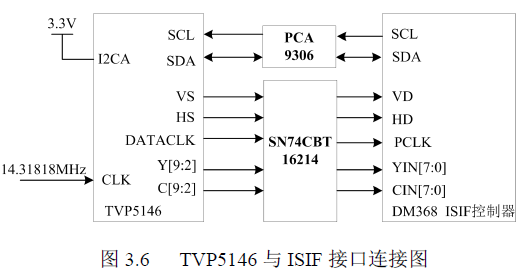

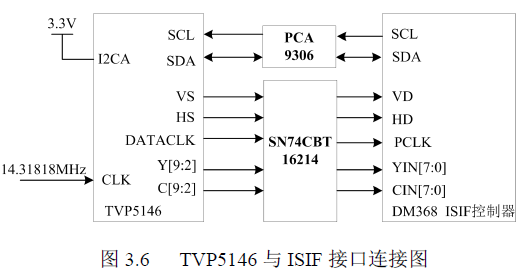

视频输入接口主要是负责对摄像头数据的采集, 其允许输入的图像信号有 CCD/CMOS 输出的 8/16bit 的 raw data 以及 8/16bit 的YCbCr 数据。本系统视频采集前端选用 CCD 摄像头,其输出为 PAL 制式模拟视频信号,需要采用视频解码芯片对信号进行模数转换。系统选用的 TVP5146 芯片作为前端摄像头的解码芯片,可将模拟视频信号PAL、SCVB、NTSC、S-video 转换为YCbCr 格式输出[38]。TVP5146 输出的 YCbCr 格式支持 10/20bit 精度,而 DM368 支持 8/16bit 精度的YCbCr 输入,所以 TVP5146 选用 8bit 精度 YCbCr4:2:2 格式输出,低两位像素信息舍去。TVP5146 解码后的视频信号不能直接送入 DM368 的 ISIF 接口,因为其输出信号的接口电压为 3.3V,而 DM368 端信号的电压为 1.8V,所以视频信号必须通过 SN74CBT16214 电压转换器转换才能送入 DM368 的图像传感器接口。TVP5146 与DM368 的 ISIF 接口连接图如图3.6 所示。

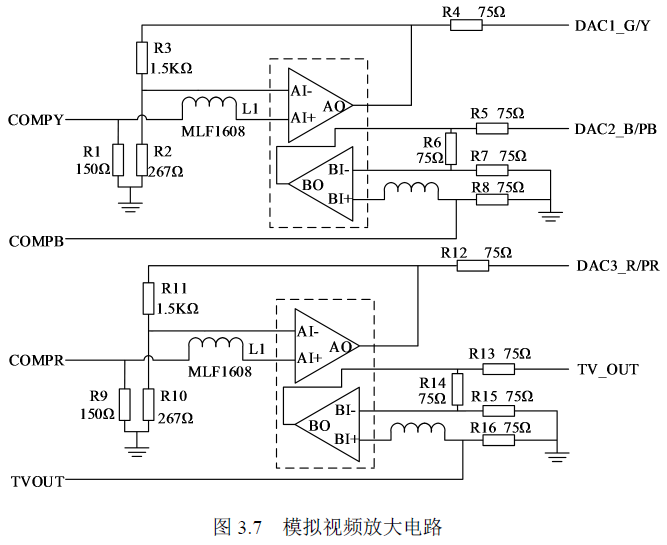

3.2.2 视频输出接口设计

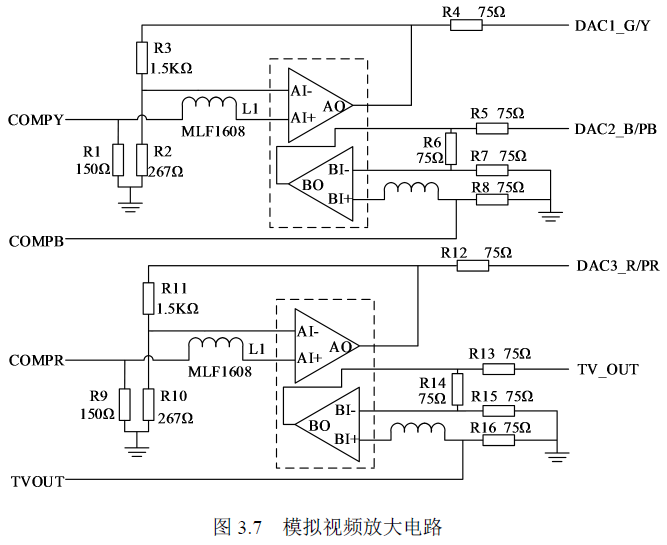

DM368 模拟视频的输出主要包括普通的BNC 输出和TV Composite 输出。DM368的模拟视频接口控制器输出的TVOUT 即为输出的电视信号,与BNC 接口的电视机连接。控制器输出的COMPY、COMPPB 和COMPPR 信号分别为高清模拟信号Y/Pb/Pr信号。由于DM368 输出的模拟视频信号无法直接驱动显示器,所以需要经过运算放大器进行放大后才能驱动显示。系统采用两片OPA2357 放大器芯片对COMPY、COMPPBCOMPPR 和TVOUT 进行放大后输出DAC1_G/Y、DAC2_B/PB、DAC3_R/PR 和TVOUT。模拟视频放大电路如图3.7 所示。

3.3 外部存储器模块设计

3.3.1 NAND 存储器模块接口设计

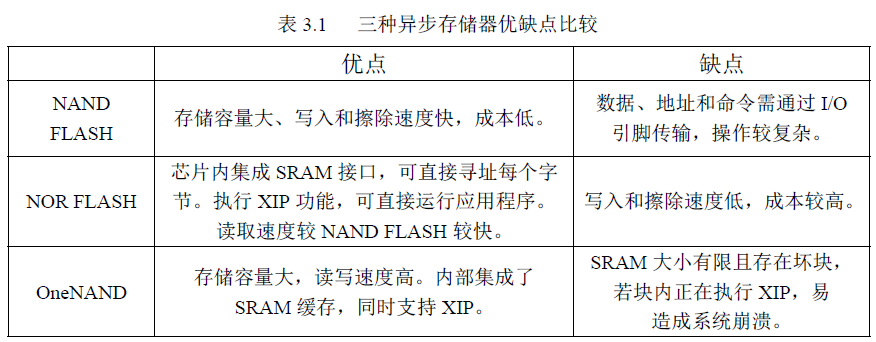

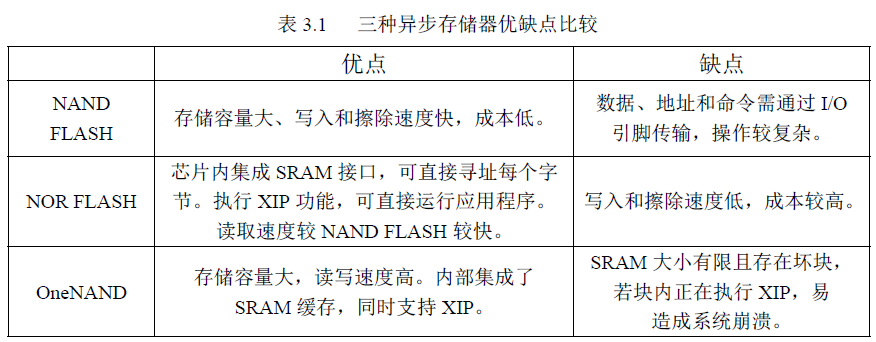

DM368 内部的AFMIF[39]控制器提供异步外围存储器接口,可进行3 种存储器的扩展,包括NAND FLASH、Nor FLASH 和OneFLASH。下面对三种异步存储器的优缺点做出分析,如下表3.1 所示。

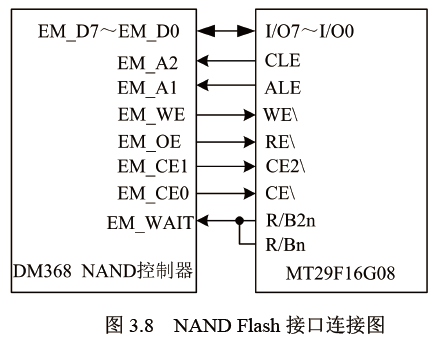

从以上三种异步存储器的优缺点并结合系统未来上层开发对存储器容量的需求,系统选用NAND FLASH 作为外部存储器。NAND FLASH 芯片采用Micron 公司生产的大小为2GB 的MT29F16G08FAAWC 芯片,主要用来存储数据,包括Uboot 启动代码、Linux操作系统、文件系统及系统运行时产生的配置文件等信息。MT29F16G08FAAWC 内部

包含两片MT29F8G08FAAWC,通过片选信号CE和CE2进行片选使能。EM_D[15..0]为数据总线,本系统中NAND FLASH 选用8bit 模式,故只选用DM368 的低8 位进行地址、命令的输入以及数据输入输出。EM_A[13..0] 为DM368 的地址总线,MT29F16G08FAAWC 的ALE 和CLE 表示地址锁存信号和命令锁存信号,分别与EM_A1和EM_A2 连接。只有当ALE 和CLE 信号同时为高且在WE 信号的上升沿时,地址信号和命令信号才被锁存到内部的地址寄存器和命令寄存器。写使能信号EM_WE,上升沿有效。输出使能信号EM_OE 与FLASH 的RE 信号连接,下降沿后tREA 时间内数据有效。异步等待信号EM_WAIT 与FLASH 的R/B 信号相连,为低表示设备忙,为高表示设备已准备好。NAND Flash 与DM368 的存储器控制器连接如图3.8 所示。

3.3.2 DDR2/mDDR 模块接口设计

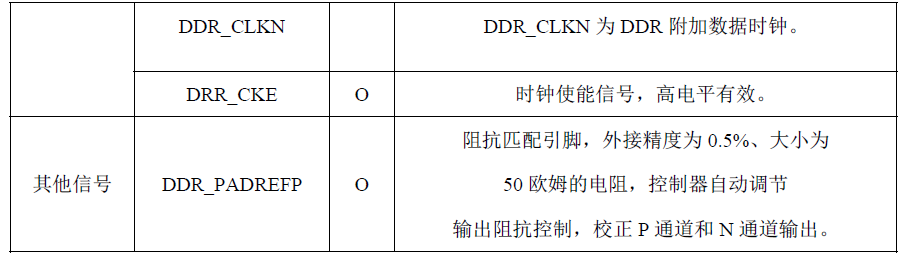

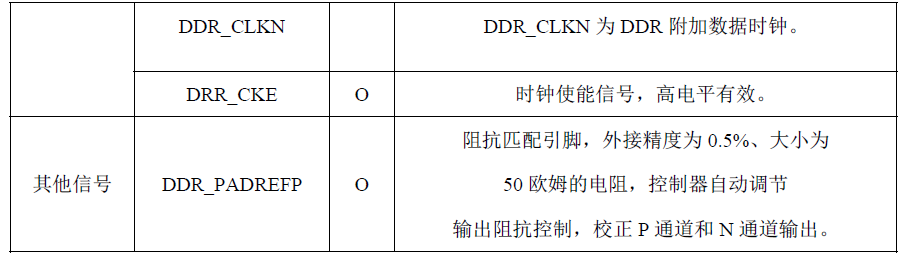

DM368 内部集成了DDR2/mDDR 存储控制器接口,这个接口支持JESD79D_2A 标准的DDR 2 SDRAM 和移动的DDR SDRAM[40]。SDRAM 不仅能够为Linux 系统的运行提供内存,如系统软件和应用软件资源都需存储在DDR2 内存中,并能为DSP 的正常运行提供连续的内存缓冲区。如对图像传感器CMOS/CCD 输出的视频图像数据的缓存;视频处理前端图像格式转换的中间缓存;视频数据的编解码缓存。系统运行过程中,DM368 片内的主动存取设备如ARM、DSP、外围主控设备、EDMA、VPSS 等均需通过DDR2 控制器接口对DDR2 内存进行存取[41],当DDR2 控制器同时接收到多个设备的存取请求时,将通过中央交换资源(SCR)按照设备的优先级实现分时存取。所以DDR2/mDDR SDRAM 在DM368 视频压缩系统中起着举足轻重的作用,直接决定系统的性能。DM368 内部集成的DDR2/mDDR 存储控制器支持最大容量为256Mbytes、最高时钟频率为200MHz 的DDR2 SDRAM。由于Linux 操作系统稳定而流畅的运行需要80MB的内存空间,应用层程序所开辟的缓存区大约需要30 MB 左右的内存空间[42],并综合考虑低功耗要求等因素,本系统选用Micron 公司生产的数据宽度为16 位、大小为128MBytes 的DDR2 800 芯片MT47H64M16HR 作为系统的“内存”芯片,并将其配置为8Mbit×16I/Os×8 banks=64M×16=1Gb 模式。MT47H64M16HR 芯片的管脚定义如下表3.2 所示。

该芯片与DM368 的DDR2 存储控制器的引脚完全兼容,16 位数据线、14 位地址线和3 位块选择信号线均可以完全对应。由于采用双端差分模式的时钟信号(CKP 和CKN),该芯片同时具有高达800Mb/sde 双数据传输率,即在时钟信号CKP 的上升沿和CKN 的下降沿分别传输一次数据,即每个时钟传输2 个数据字。由于在DDR2 控制器内部没有集成与存储器终端相匹配的电阻,因此DM368 和DDR2 之间的数据线、地址线和控制线之间均需串接电阻。DDR2 中均为高速信号线,且布线密度较大,为减小布局、布线空间,设计中在不降低芯片驱动能力的情况下采用串接33 欧的等值排阻以减小信号的震荡和反射,使数据信号传输更加稳定。MT47H64M16 与DDR 控制器的连接图如图3.9 所示。

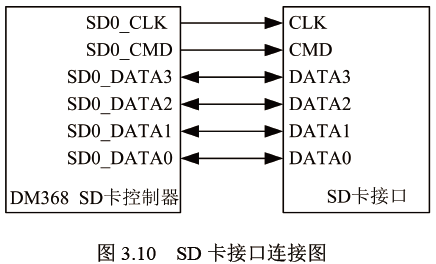

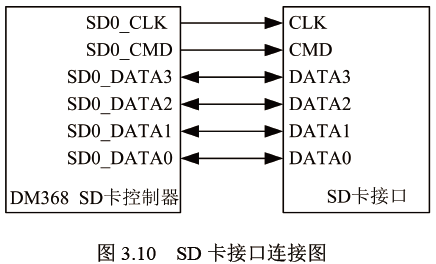

3.3.3 SD 卡模块接口设计

SD 卡作为新一代的的记忆设备,具有大容量、高性能、安全、体积小等优点,已被广泛应用于现代便携数码装置上,如个人数码相机、数码摄录机和多媒体播放器。DM368内部也集成了MMC/SD 控制器,其符合MMC V3.1、SD Part1 物理层V1.1 和SDIO V2.0标准,支持2 路SD 卡。MMC/SD 卡控制器负责ARM 和EDMA 控制器与MMC/SD 卡之间的数据传输。SD 主控制器可支持SD 卡和SPI 两种模式。在SD 卡模式下,时钟频率为0~25MHz,采用4 根数据线传输,速度更高,读写速度最高可达100Mbps,相比于USB 接口更快。SPI 模式采用SPI 接口传输数据,与SD 卡模式相比,速度很慢。本系统使用SD0 接口,采用SD 模式保证较快的视频数据存储。SD 卡接口的连接图如图3.10 所示。

在MMC/SD 模式下,控制器支持单个或多个MMC/SD 卡,当多个卡被连接时,MMC/SD 控制器通过数据线识别广播选择其中一个。MMC/SD 控制器管脚如下:CMD:此管脚用于MMC/SD 控制器和卡之间的双向通信,MMC/SD 控制器通过此管脚传输命令给卡和存储卡驱动器的命令响应。DATA3~DATA0: MMC 卡只使用数据线DATA0 进行数据传输,SD 卡采用四根数据线进行数据传输。MMC 控制寄存器(MMCCTL)通过设置WDYH 位进行数据传输时使用的管脚数目(数据总线宽度)的设定。CLK:MMC/SD 控制器输出时钟给存储卡。

3.4 外围接口硬件设计

3.4.1 以太网模块设计

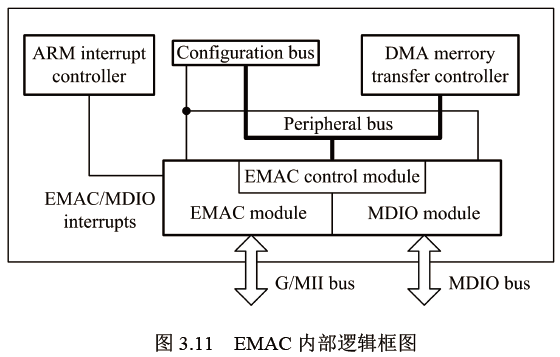

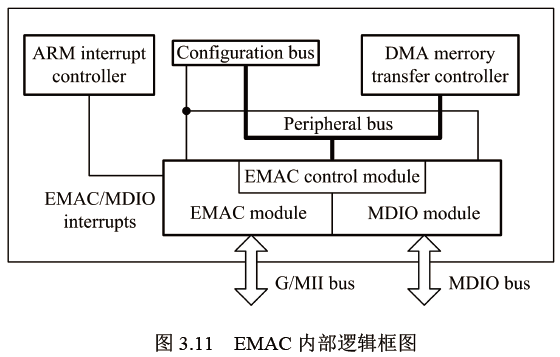

本系统中,Linux 内核的下载、远程访问Linux 主机端的TFTP/NFS(网络文件系统)以及压缩视频流的实时传输都需要以太网接口实现。以太网媒体存取控制器EMAC(Ethernet Media Access Controller)为压缩数据上传网络提供了有效的接口,使得DM368与上位机之间遵循以太网协议进行数据交换传输。以太网接口主要是由EMAC 控制器和物理层接口PHY(Physical Layer)两大部分组成。DM368 内部集成了以太网媒体存取控制器(Ethernet Media Access Controller,EMAC)和物理层设备管理数据输入输出模块(Management Data Input/Output,MDIO)。EMAC 用于控制系统与物理层(PHY)之间的数据包流,由于它属于OSI 七层模型中的数据链路层,因此还需要外接物理层接口芯片,即可实现网络通信[43]。EMAC 支持同步10/100Mbps 的传输速率,同时也支持硬件流控制。MDIO 用于PHY 的配置和状态监控。EMAC/MDIO 包含3 个主要的功能模块:EMAC 控制模块、EMAC 模块和MDIO 模块[44],三者之间的逻辑框图如图3.11 所示。

EMAC 控制模块是器件内核处理器和EMAC/MDIO 模块的主接口,其内置了8KB的内部RAM 用于保存EMAC 缓冲区中的外部操作描述符,同时其内部包含了必要的组件以使EMAC 高效使用器件内存。EMAC 模块提供高效的处理器和网络之间的通讯接口,支持半双工或全双工的10Base-T(10Mbits/s)和100BaseTX(100Mbits/s)以及全双工的100BaseT[45]。MDIO 模块可实现IEEE802.3 标准的网络协议串行管理接口,通过两线制的共享总线来查询和控制连接在器件上的PHY。通过MDIO 模块可配置物理层PHY 的参数,状态的监控和查询结果的接受,获得协商结果,配置EMAC 模块正确操作所需要的参数。

EMAC/MDIO 有以下特点:

1.同步10/100/1000Mbps 操作。

2.与物理层器件PHY 之间的G/MII 接口。

3.全双工Gbit 运行(Gbit 下不支持半双工)。

4.CRC 硬件错误处理。

5.8 个发送通道,支持Round-Robin 或固定优先级,保证数据传输服务质量。

6.8 个带有VLANtag 辨识的接受通道,保证数据接受质量。

7.可以在单个通道上选择接受广播帧和多播帧。

8.硬件数据流控制。

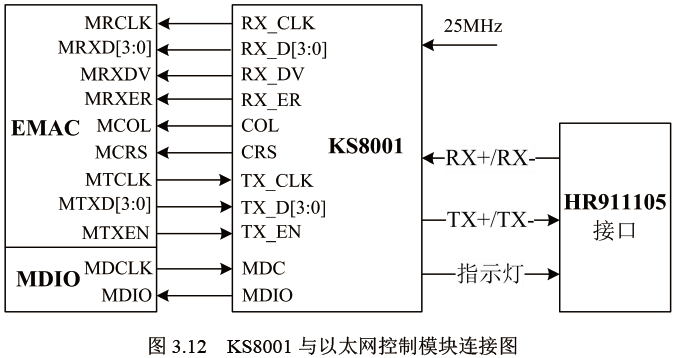

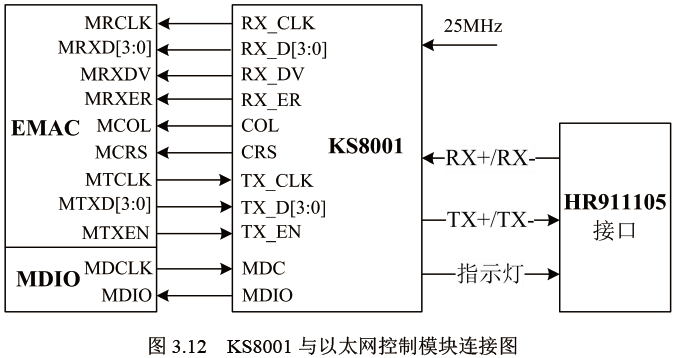

因DM368 内部已集成了网络的数据链路层,所以系统选用Micrel 公司生产的KS8001L 芯片实现网络的物理层协议,进而构成一个完整的网络底层。KS8001L 能够实现全部的10/100M 以太网物理层功能,工作电压为3.3V,核心电压为1.8V,内部集成了MII 接口和MDIO 配置接口。KS8001 与DM368 以太网控制模块的连接图如图3.12所示。

MII 接口包含三部分:数据接受接口(MTCLK、MTXD[3:0]、MTXEN),数据发送接口(MRCLK、MRXD[3:0]、MRXDV、MRXER),网络状态检测接口(MCOL、MCRS)。数据的发送和接受是两个独立的通道,有各自的时钟、数据和控制信号。MDIO 接口使用单独的管理数据时钟信号MDCLK,通过单根管理数据输入输出信号MDIO 实现PHY管理数据的发送和接受。

RJ-45 接口采用HR911105A 接口电路,其内部已集成了网络隔离变压器和状态指示灯,与KS8001 的6 根信号线相连:接受数据差分信号对(RX+,RX-)、发送数据差分信号对(TX+,TX-)、两个指示灯(Link 状态指示,全双工/半双工模式指示)。

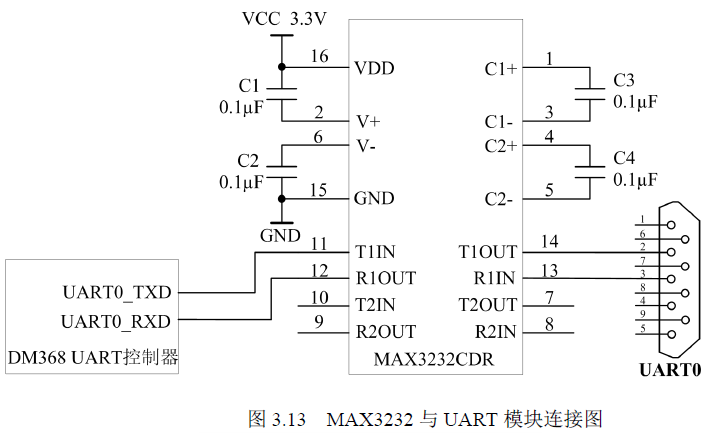

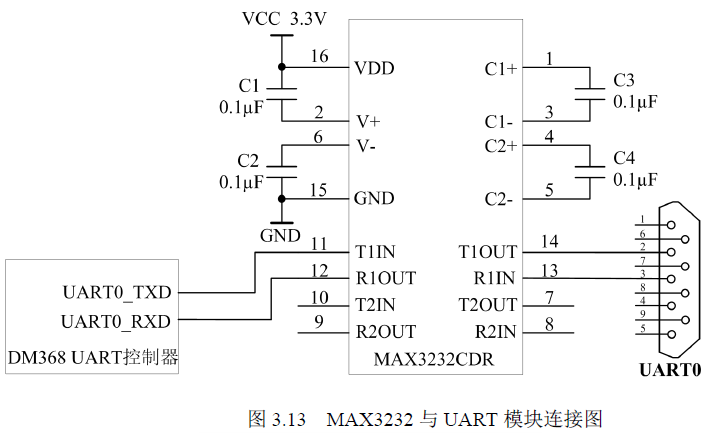

3.4.2 UART 模块设计

DM368 内部集成了2 路UART 串口[46],本系统选用UART0 作为RS232 接口,作为系统调试接口。采用MAX3232 芯片实现逻辑电平的转换,其连接图如下图3.13 所示。

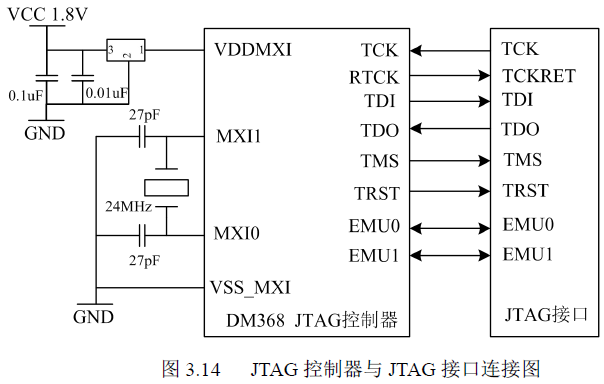

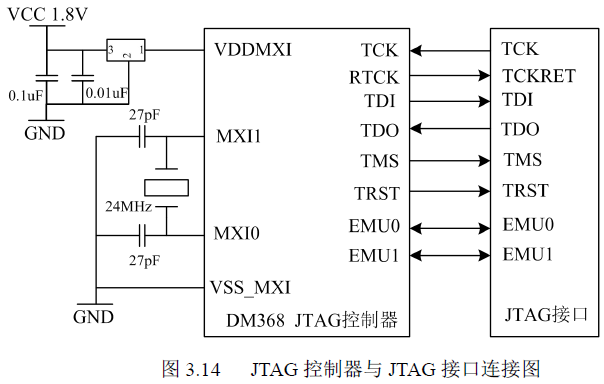

3.4.3 JTAG 模块设计

JTAG 接口在嵌入式系统开发中得到广泛应用,在目前的高端处理器(如FPGA、DSP、ARM 等)上都有配备。DM368 内部集成了14 针的JTAG 调试接口,可与XDS560仿真器上的JTAG 无缝连接,其电路连接图如图3.14 所示。

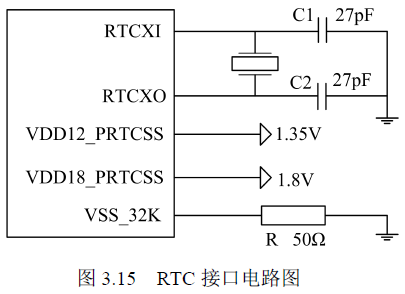

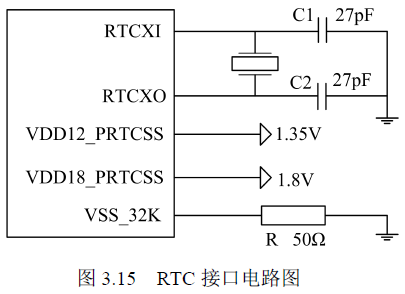

3.4.4 RTC 模块设计

RTC 控制器被集成到DM368 内部,主要应用于各种日历事件[47]。RTC 在本系统中独立供电,因此不受其他事件影响,比如在DM368 复位时其仍然能够正常工作。本系统中RTC 接口电路原理图如图3.15 所示。其中,RTCXI 和RTCXO 分别为RTC 晶体的输入和输出,大小为32.768KHz;电源1.35V 和1.8V 分别通过VDD12_PRTCSS 和VDD18_PRTCSS 口为PRTCSS 模块供电;VSS_32K 通过50 欧电阻接地。

3.4.5 电源模块设计

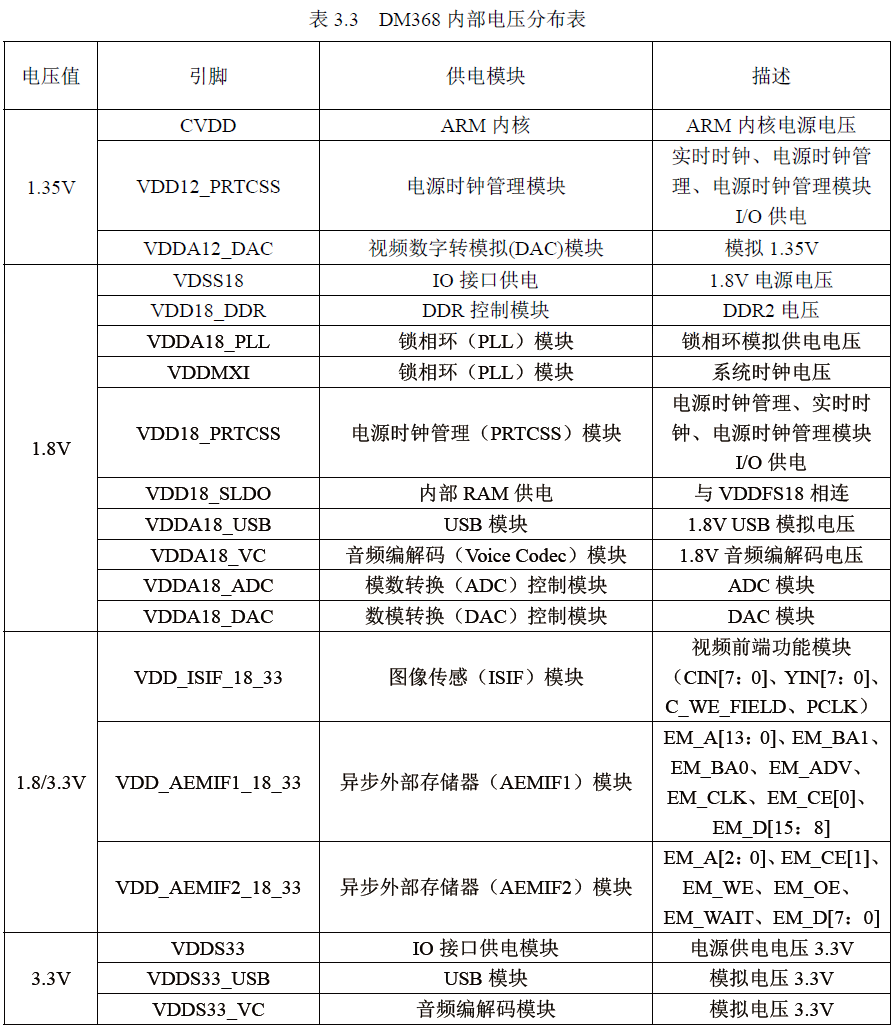

DM368 片上系统的电压值分布如下表3.3 所示。

从表中可以看出,系统硬件部分共需要三种电压,分别为3.3V、1.8V 和1.35V,同时系统对DM368 芯片的的上、下电顺序有较为严格的要求,即上电顺序为先是内核电压1.35V,接着是1.8V,最后是3.3V,下电顺序与上电顺序正好相反。为了满足上述供电需求,选用TI 公司生产的电源芯片TPS3808G01 和TPS65053 进行电源设计。TPS65053 芯片的1.35V 输出端接入到TPS3808G01 芯片的使能端SENSE,作为1.8V 和3.3V 的输出使能。只有当TPS65053 输出1.35V 电压之后,才能使TPS3808G01 芯片的SENSE 端为高电平,TPS65053 的使能信号EN3V3 和EN1V8 有效,依次输出输出1.8V 和3.3V。