2016-07-11

总结中断寄存器配置,存储映射1 中断寄存器配置

1.1 中断的分类和服务表的设置

硬件中断装置是中断系统的机制部分,负责捕获中断源发出的中断请求,以一定方式响应中断源,然后将处理器控制权交给特定的中断处理程序; 软件中断处理程序是中断系统的策略部分,负责辨别中断类型并作出相应的操作。引入中断的目地是解决主机与外设的并行工作问题,实现实时控制。 分类:RESET(复位)中断,不可屏蔽中断(NMI),可屏蔽中断(INT4-INT15)。优先级:复位中断>不可屏蔽中断>可屏蔽中断。 中断应答信号:IACK信号指出CPU已将开始处理一个中断,INUMx(INUM3-INUM0)信号指出正在处理的是哪一个中断,其四位值大小对应于IFR(中断标志寄存器)中的位的位置。 中断服务表:中断服务的地址表,表中包含中断服务代码的取址包。IST包含16个连续的中断取指包,在每一个中断取指包中,都具有8条指令,其中每条指令都包含32位指令字,表中是以32位字节进行增长的。

图1.1 中断服务表IST 中断服务表指针寄存器(ISTP): 该寄存器确定中断服务程序在中断服务表中的地址。

图1.2 ISTP结构

图1.3 ISTP各字段作用

1.2 中断的描述和相关寄存器配置

6813CPU支持16个优先级中断,最高优先级中断是INT_00(专用于复位),最低优先级中断时INT_15。前四个中断为非屏蔽和固定中断,其余的中断(4-15)为可屏蔽和默认中断源。 中断选择寄存器描述:

图1.4 中断选择寄存器描述 根据其地址在头文件中定义中断选择寄存器: // 定义中断选择寄存器 #define MUXH_REG 0x019C0000 #define MUXL_REG 0x019C0004 #define EXTPOL_REG 0x019C0008 所有中断控制寄存器描述:

图1.5 中断控制寄存器描述 状态控制寄存器(CSR): 状态控制寄存器有两个位用于控制中断:GIE和PGIE,GIE-全局中断使能(global interruppt enable)是状态控制寄存器的(CSR)的bit0,控制GIE的值可以使能或者禁止所有的可屏蔽中断。PGIE是控制寄存器(CSR)的bit1,PGIE包含之前的GIE,当处理可屏蔽中断期间PGIE保存GIE的值,而GIE被清零,这样在处理一个可屏蔽中断期间,就防止了另外一个可屏蔽中断的发送,当中断返回时,通过写程序指令把PGIE的值重新返回到GIE中。

图1.6 CSR结构图

图1.7 GIE和PGIE字段描述 禁止全局中断: CSR = 0x00000100; 使能全局中断: CSR = CSR | 1; 中断使能寄存器(IER): 中断使能寄存器(IER)控制每一个中断源是否被使能。通过IER中相应的个别中断为的置1或者清零可以使能或者禁止个别中断。

图1.8 IER结构 IER的bit0对应于复位,该位可读(读作1)不可写,由于bit0始终为1,所以复位总被使能。Bit IE4-IE15写1或者写0分别使能或禁止相关中断。NMIE = 0时,禁止所有非复位中断;NMIE = 1时,GIE和相应的IER位一起使能INT15-INT4中断,对NMIE写0无效。只有复位和NMI发生时清零,NMIE的置1靠执行B NRP指令和写1完成。 使能中断NMI和IE14-IE15: IER= 0x0000C003; 中断标志寄存器(IFR): 中断标志寄存器(IFR)包括INT4-INT15和NMI的状态。当一个中断发生时,IFR中的相应中断位被置1,否则为0。使用MVC指令读取IFR,可检查中断状态。

图1.9 IFR结构 中断设置寄存器(ISR): 中断设置寄存器(ISR)可以手动设置中断标志寄存器(IFR)中的可屏蔽中断位。对ISR的IS4-IS15位写1,则引起IFR对应中断标志位置1;对ISR任何为写0无效,设置ISR的任何位都不影响NMI和复位。进入的中断具有优先权,当同时ICR和ISR的同一位写入时,ISR写入优先。

图1.10 ISR结构 中断清除寄存器(ICR): 中断清除寄存器(ICR)可以手动清除中断标志寄存器(IFR)中的可屏蔽中断位。对ICR的IC4-IC15位写1,则引起IFR对应标志位置0。对ICR的任何位写0无效,清除ICR的任何位都不影响NMI和复位。

图11 ICR结构 清除所有中断标志位: ICR = 0xFFFF; 不可屏蔽中断返回指针寄存器(NRP): 不可屏蔽中断返回指针寄存器(NRP)包含从不可屏蔽中断返回时的指针,该指针引导CPU返回到原来程序执行的正确位置,当NMI复位完成时,为返回到被中断的源程序中,在中断服务程序结尾处,必须插入一条跳转到NRP的指令(即 BNRP)。不可屏蔽中断返回指针寄存器(NRP)包含由于NMI而未执行的程序流程中第一个执行包的32位地址。尽管可以对这个寄存器写值,但任何接下来的中断处理将刷新这个值。

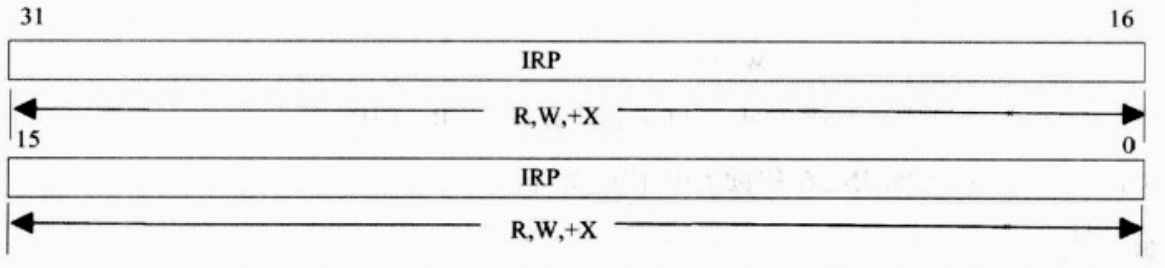

图12 NRP结构 可屏蔽中断返回指针寄存器(IRP): 可屏蔽中断返回指针寄存器(IRP)的功能与不可屏蔽中断返回指针寄存器(NRP)基本相同,不同的地方是中断源,该寄存器中为可屏蔽中断源。

图13 IRP结构

1.3 中断源与中断信号

6713的外设部分最多可以提供32种中断源,但是CPU只能利用其中的12个,用户是通过中断选择来定义中断源和中断信号之间的映射关系的,在中断选择中还可以定义外中断信号的极性。

图16 中断源与中断信号的映射关系 外部中断极性寄存器是用来定义外部中断的触发极性的。XIP4-XIP7分别控制EXT_INT4-EXT_INT7的触发极性,当XIP = 0时,外部中断信号为上升沿有效,当XIP = 1时,外部中断信号为下降沿有效。