SerDes宏和其配置

SRIO通过允许一个可扩展的非专有接口,为我们提供了许多好处。这个接口就是SerDes。通过使用SerDes宏,可以与外设交流,并且外设都可以扩充带宽。同一个外设可以用在V1.2版本的RapidIO 接口协议的四个频率下:1.25、2.5、3.125和5Gbps。这样就可以在整个系统中有一个协议就足够了,可以选择性地选取带宽。这种做法消除了使用用户自带协议的情况,减短了研发周期。由于SerDes是串行的,所以程序空间不限于一个板子上,它的应用空间是整个板子。(Because this interface is serial, the application space is not limited to a single board. It will propagate into backplane applications as well.)这些在ASIC(Application Specific Integrated Circuit 特定用途集成电路)或DSP上集成的宏可以减少板子上分立元件的数量,并且消除对总线驱动芯片的需求。TI SerDes宏附有一些有用的特点。1)可以唯一地管理系统优化,以针对个别客户的需求。例如,控制寄存器内的SerDes允许你调整TX的差分输出电压,这样就可以减少TX的摆动,进而省电。2)数据边缘率(data edge rates)可以类似地调整,以减少电磁干扰的影响。

3)不使用的连接可以不通电,减少功耗。SerDes宏是一个独立的宏,包含RX(接收寄存器),TX(传输寄存器),PLL(锁相环),时钟恢复模块,串行至并行模块(S2P),并行至串行模块(P2S)。内部锁相环可以为用户提供参考时钟,所有锁相环的环路滤波器都在片上。同样,差分RX和TX缓存也包含片上(on chip)终端电阻。唯一需要片外提供的是直流阻塞电容器。

使能锁相环(Enabling the PLL)

物理层SerDes有一个内置的锁相环,用于时钟恢复电路。该锁相环是为一个低速参考时钟做倍频的,这个低速参考时钟与串口数据没有任何时序关系,同时与CPU时钟是异步的。高速倍频时钟只在SerDes内部使用,不会分到周围的外设当中,也不是设备核的一个边缘信号(nor is it a boundary signal to the core of the device)。拥有一个高质量的参考时钟非常重要,同样,将时钟和锁相环与噪声隔离也非常重要。SerDes宏是通过这些寄存器进行配置的:SRIO_SERDES_CFGPLL, SRIO_SERDES_CFGRX[3-0], SRIO_SERDES_CFGTX[3-0],和SRIO_SERDES_RSVD。为了使能内部锁相环,SRIO_SERDES_CFGPLL的ENPLL位必须置1,置1之后等待1秒让稳定器使系统稳定,此后,如果RIOCLK存在并且RIOCLK稳定,锁相环将使用不超过200个参考时钟周期,来锁定所需的频率。为了确定锁相环是否已经稳定,可以看SRIO_SERDES_STS寄存器的lock位,1是已经稳定,0是未稳定。使能接收器(Enabling the Receiver)

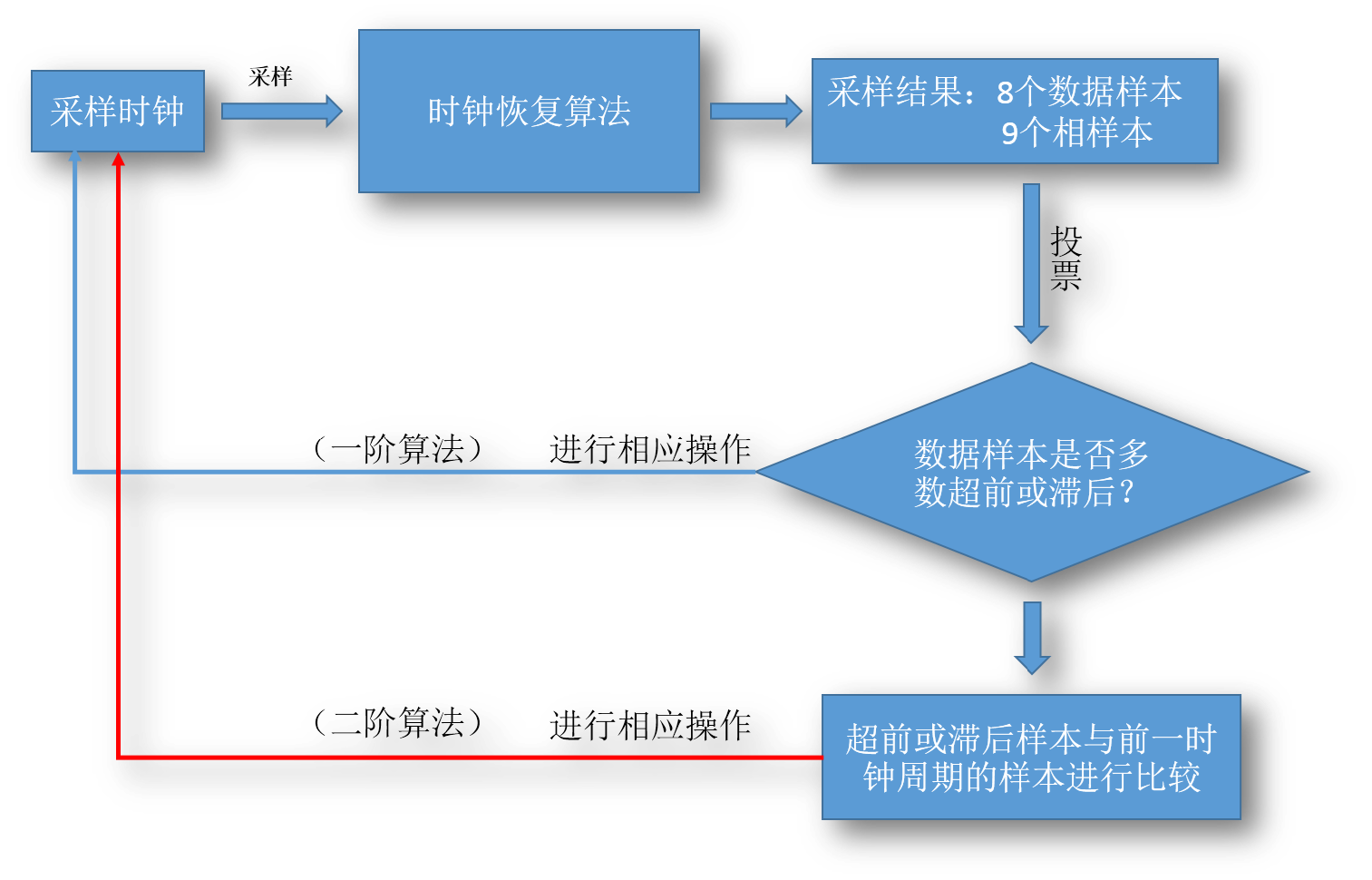

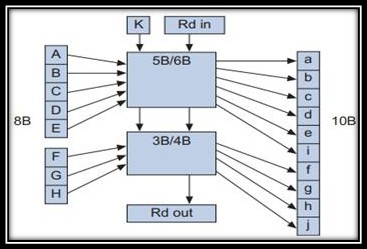

为了使能一个接收器来解串(deserialization),SERDES_CFGRXn_CNTL 寄存器的ENRX位必须置1。当ENRX位是0的时候,所有接收器中的数字电路将被禁用,时钟也会被锁定。除了相关的信号丢失检测器和IEEE1149.6边界扫描比较器,接收器的其它模块所有电流被完全切断。信号丢失断电(Loss of signal powerdown)是通过SERDES_CFGRXn_CNTL寄存器的Los位来控制的,如果将Los位使能,就开始监视接收到的差分信号,一旦检测到信号损失,时钟恢复算法将会被冻结,以防止恢复时钟的相位和频率被低电平噪声信号改动。对SERDES_CFGRXn_CNTL寄存器的CDR(clock/data recovery)位中列出的时钟恢复算法进行操作,对接收到的消息进行采样,这样数据样本在数据传输中途就会被拿到。【这里说的是一阶恢复算法】二阶时钟恢复算法(second order algorithm)可以选择性地禁用,并且时钟恢复算法都可以用来配置优化寄存器的动态性能。这两种算法的原理基本相同,它首先确定采样时钟的放置是否合适,如果没有放置合适,那么应该提前还是滞后,这都是它们首先要确定的问题。当检测到两个连续样品不一样,那么着两个样品之间的相样品也会被检测。每次检测结果中,都会被提取8个数据样本和9个相样本,利用这些样本综合评估是否需要提前或者滞后。这8个数据样本构成了部分评估窗口,如果这8个数据样本的多数提前或者滞后,就采样时钟进行相应的提前或滞后操作。一阶算法在每次综合评估后调整一次相位,二阶算法根据这一时钟多数票和前一时钟多数票的净差额,来不断调整相位,从而调整相位的变化率。示意图如下图所示。 把SERDES_CFGRXn_CNTL寄存器的Align域设置成01,该操作成功之后,数据会与包含在8b10b规则中的K28逗号标准对齐。那么什么是8b10b规则呢?为什么要使用8B10B编码呢?是因为8B10B编码的特性之一就是保证直流平衡,即编码后二进制数据流中“0”和“1”的数量基本保持一致,因为我们知道当高速串行流的逻辑1和逻辑0有多个位没有产生变化时(即所谓的长连0和长连1),信号的转换就会因为电压位阶的关系而造成信号错误,直流平衡最大好处就是可以克服这个问题。8B10B编码是怎么做到DC平衡的呢?转换的时候,连续的“0”或者“1”数量不超过5位,即每5个连续的“0”或者“1”后必须插入一位“1”或者“0”,从而保证信号DC平衡。这样可以保证串行数据可以在接收端被正确复原,同时利用一些特殊代码(K码)也可以帮助接收端进行复原工作,且可以在早期发现数据位传输错误,抑制错误继续发生。下图是8b10b编码示意图。

把SERDES_CFGRXn_CNTL寄存器的Align域设置成01,该操作成功之后,数据会与包含在8b10b规则中的K28逗号标准对齐。那么什么是8b10b规则呢?为什么要使用8B10B编码呢?是因为8B10B编码的特性之一就是保证直流平衡,即编码后二进制数据流中“0”和“1”的数量基本保持一致,因为我们知道当高速串行流的逻辑1和逻辑0有多个位没有产生变化时(即所谓的长连0和长连1),信号的转换就会因为电压位阶的关系而造成信号错误,直流平衡最大好处就是可以克服这个问题。8B10B编码是怎么做到DC平衡的呢?转换的时候,连续的“0”或者“1”数量不超过5位,即每5个连续的“0”或者“1”后必须插入一位“1”或者“0”,从而保证信号DC平衡。这样可以保证串行数据可以在接收端被正确复原,同时利用一些特殊代码(K码)也可以帮助接收端进行复原工作,且可以在早期发现数据位传输错误,抑制错误继续发生。下图是8b10b编码示意图。 如图所示,8bit(HGFEDCBA,H是MSB,A是LSB)原始数据会被分成两部分,低5bit进行5B6B编码,高3bit则进行3B4B编码,这已成约定俗成的标准,所以8bit数据(0到255)也被表示为Dx.y的形式,其中x就是低5bit对应的十进制数值,而y就是高3bit对应的十进制数值。例如8bit数“101 10101”,即十进制数181,这时候按照上述划分原则x=10101(21),y=101(5),所示这个数被表示为D21.5。这叫Code Notation。对于不能使用8b10b编码对齐的系统,单点对准慢跑能力(single bit alignment jog capability)提供了一种手段控制ASIC(特定用途集成电路)核中直接由逻辑实现的receiver(接收器)的符号重组特点,该逻辑可以设计支持任何对齐检测协议。SERDES_CFGRXn_CNTL寄存器的EQ位允许配置和使能所有接收通道内都有的自适应均衡器(adaptive equalizer),这些自适应均衡器能够通过衰减信号中的低频分量,来补偿通道插入损失(channel insertion loss),这样就会降低内部信号的干扰。在零频以上,增益每倍频程增加6dB,直到达到高频增益,当EQ位使能时,接收器的均衡逻辑分析数据模式和传输次数,以确定均衡器的低频增益是否应该增加或减少。对于完全自适应设置,即将EQ位设置成0001,如果低频增益达到最小值,零频就会被减少;同样,如果低频增益达到最大值,零频就会增加。这样的决定逻辑是通过以一种相对长时间分析(relatively long analysis interval)为基础的投票算法实现的。慢时间常数( slow time constant )降低了错误决定的可能性,同时补偿了通道相对稳定的响应。以下是EQ位中相应设置对应的解释,大家可以在文末的参考文献中详细了解。1)无自适应均衡

如图所示,8bit(HGFEDCBA,H是MSB,A是LSB)原始数据会被分成两部分,低5bit进行5B6B编码,高3bit则进行3B4B编码,这已成约定俗成的标准,所以8bit数据(0到255)也被表示为Dx.y的形式,其中x就是低5bit对应的十进制数值,而y就是高3bit对应的十进制数值。例如8bit数“101 10101”,即十进制数181,这时候按照上述划分原则x=10101(21),y=101(5),所示这个数被表示为D21.5。这叫Code Notation。对于不能使用8b10b编码对齐的系统,单点对准慢跑能力(single bit alignment jog capability)提供了一种手段控制ASIC(特定用途集成电路)核中直接由逻辑实现的receiver(接收器)的符号重组特点,该逻辑可以设计支持任何对齐检测协议。SERDES_CFGRXn_CNTL寄存器的EQ位允许配置和使能所有接收通道内都有的自适应均衡器(adaptive equalizer),这些自适应均衡器能够通过衰减信号中的低频分量,来补偿通道插入损失(channel insertion loss),这样就会降低内部信号的干扰。在零频以上,增益每倍频程增加6dB,直到达到高频增益,当EQ位使能时,接收器的均衡逻辑分析数据模式和传输次数,以确定均衡器的低频增益是否应该增加或减少。对于完全自适应设置,即将EQ位设置成0001,如果低频增益达到最小值,零频就会被减少;同样,如果低频增益达到最大值,零频就会增加。这样的决定逻辑是通过以一种相对长时间分析(relatively long analysis interval)为基础的投票算法实现的。慢时间常数( slow time constant )降低了错误决定的可能性,同时补偿了通道相对稳定的响应。以下是EQ位中相应设置对应的解释,大家可以在文末的参考文献中详细了解。1)无自适应均衡 均衡器在增益达到最大值的时候提供了一个平稳响应。如果接收器的剧烈抖动是由于两条线之间的互相干扰而不是频率损失,这种EQ设置模式是推荐的。2)完全自适应均衡

低频增益和零频位置都取决于分析接收到的数据中的数据模式和数据过渡位置。该设置推荐应用于大多数工程。3)部分自适应均衡

低频增益取决于分析接收到的数据中的数据模式和数据过渡位置,零频固定在8个零频中的一个位置。对于任何一个给定的应用,最好的设置是一个关于信号的损耗特性,信号的谱密度和信号的数据速率的函数,这意味着不可能只通过分析数据速率而得到最好的设置,尽管一般来说,数据速率越低,零频的位置就要越低。

使能传输器(Enabling the Transmitter)

为了使能一个传输器来串行化,SERDES_CFGTXn_CNTL寄存器的ENTX位必须要置,1,如果ENTX位是0,传输器内所有电路都被禁用,时钟都会被关闭,除了传输时钟输出(TXBCLK[n]),传输时钟输出会一如既往的继续正常工作。如果ENTX位是0,传输器内的所有电流源都会掉电(就是没电),除了电流模式逻辑驱动(current mode logic (CML) driver),如果边缘扫描开启,电流逻辑驱动就会继续工作。SerDes配置示例

Example 2-1 SerDes Configuration/* Set RX/TX config values based on the lane rate specified */

/* 基于特定的线速率配置RX/TX */

switch (linkRateGbps)

{

case srio_lane_rate_5p000Gbps: /* Pll setting determines 5.0 Gpbs or 3.125

Gbps (锁相环频率设置为5Gbps或3.125Gbps)*/

case srio_lane_rate_3p125Gbps: /* Same Tx and Rx settings for 5.0 Gbps or 3.125

Gbps(Tx和Rx频率设置为5Gbps或3.125Gbps) */

rxConfig = 0x00440495;/*该数等于二进制的:0000 0000 0100 0100 0000 0100 1001 0101*/

// (0) Enable Receiver 第0位是1,使能接收器

// (1-3) Bus Width 010b (20 bit)第1-3位是010,该位永远设置为010,指示总线为20bit宽度

// (4-5) Half rate. Two data samples per PLL output clock cycle第4-5位是01,每个锁相环输出时钟周期接收两个数据样本

// (6) Normal polarity 第6位是0,该位的作用是翻转极性,即将高电平有效翻转位低电平有效,反之亦然。设置为0为正常设置,即RIORX是高电平有效,RIORX头上带上划线(笔者不会输入这样的字符)位低电平有效。

// (7-9) Termination programmed to be 001 第7-9位是001,这三位永远设置为001,将这三位设置为001,会设置公共点位0.8VDDT,并且支持交流耦合系统使用电流模式逻辑传输器,传输器对接收器共模没有影响,接收器共模是设置用来优化接收器的输入敏感度的。共模终端通过50pF的电容与VSSA相连。

// (10-11) Comma Alignment enabled 第10-11位是01,这两位设置是用来进行符号对齐的。设置为01,即无论什么时候收到错位信号,符号对齐都会开始工作。

// (12-14) Loss of signal detection disabled 第12-14位是000,这三位设置是用来对信号丢失检测进行使能的。

// (15-17) First order. Phase offset tracking up to +-488 ppm第15-17位是000,这三位是对时钟|数据恢复算法进行配置的。

// (18-20) Fully adaptive equalization 18-20位是001,这三位用来配置自适应均衡器的,设置为001是全自适应均衡,对全自适应均衡解释请看上文中对EQ位的解释。(第21位默认为0)

// (22) Offset compensation enabled 第22位是1,这一位是用来使能采样器偏移补偿的。

// (23-24) Loopback disabled 这两位是0,功能为关闭loopback。如果这两位是11,就是打开loopback,同时如果Los是00,就将来自传输器的电流差分信号转化为电压信号,传递给接收器输入。如果Los是10,就将来自传输器的电流差分信号转化为电压信号,传递给信号检测器。

// (25-27) Test pattern mode disabled 这两位是0,即关闭测试模式。(目前还未搞懂Test pattern。后续会回来回答这个问题。)

// (28-31) Reserved 保留位,为0000

txConfig = 0x00180795;/*传输器的配置,其二进制数为:0000 0000 0001 1000 0000 0111 1001 0101*/

// (0) Enable Transmitter 第0位是0,使能传输器

// (1-3) Bus Width 010b (20 bit) 第1-3位是010,为时钟指明该并行总线宽度为20位,一般情况下这三位总是010

// (4-5) Half rate. Two data samples per PLL output clock cycle 第4-5位为01,这两位用来设置操作率,半率为每个锁相环输出周期接收两个数据样本

// (6) Normal polarity 第6位为0,该位的作用是翻转极性,即将高电平有效翻转位低电平有效,反之亦然。设置为0为正常设置,即RIORX是高电平有效,RIORX头上带上划线(笔者不会输入这样的字符)位低电平有效。

// (7-10) Swing max. 第7-10位是1111,这四位设置的是输出电压的最大振幅。涉及到信号精度的问题。

// (11-13) Precursor Tap weight 0% 第11-13位是000,由于传输信号可能会有高频衰减,所以加上一个补偿

// (14-18) Adjacent post cursor Tap weight 0% 原理同上 11-18位都是用来调整输出波形的

// (19) Transmitter pre and post cursor FIR filter update 11-18位的加补偿都是通过FIR滤波器实现的,这里是对这两个滤波器进行更新,如果SerDes的位时钟和这一位同时为高,那么FIR滤波器就会更新

// (20) Synchronization master 将这个频道设置成主线,如果是slave线的话该位就设置成0,如果应用只有一条线,就把这个位设置为1,如果是很多线的话,就要给唯一一个频道设置成1,并且这个主频道的号码必须是所有频道里最低的。

// (21-22) Loopback disabled 这两位是00,即禁止Loopback

// (23-25) Test pattern mode disabled 这两位是00,即关闭测试模式

// (26-31) Reserved 保留位

break;

/*下面都是针对不同的线速率给出的TX和RX的设置,不再细谈*/

case srio_lane_rate_2p500Gbps: /* Tx and Rx settings for 2.50 Gbps */

rxConfig = 0x004404A5;

// (4-5) Quarter rate. One data sample per PLL output clock cycle

txConfig = 0x001807A5;

// (4-5) Quarter rate. One data sample per PLL output clock cycle

break;

case srio_lane_rate_1p250Gbps: /* Tx and Rx settings for 1.25 Gbps */

rxConfig = 0x004404B5;

// (4-5) Eighth rate. One data sample every two PLL output clock cycles

txConfig = 0x001807B5;

// (4-5) Eighth rate. One data sample every two PLL output clock cycles

break;

default: /* Invalid SRIO lane rate specified */

return -1;

}- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

当设置成1X模式的时候,一个port使用一个传输器和接收器线,工作在普通线频率之下。

当设置为2X模式的时候,一个port使用两条线,工作在2倍的普通线频率之下。

4X也是同样的道理。但是怎样设置普通线频率的问题没有得到解决,希望在之后的学习之中可以看到。参考文献

http://www.tij.co.jp/jp/lit/an/sprabc1/sprabc1.pdf

http://www.ti.com/cn/litv/pdf/sprugw1b

http://bbs.ednchina.com/BLOG_ARTICLE_3015507.HTM