Timingdesigner timing designer 入门 基础 教程

冰三点水

Timingdesigner是一个灵活强大的画时序图软件,在fpga或dsp等开发中具有一定的应用价值,本帖介绍timingdesigner基本操作,包括时钟、信号、总线等绘制。转载请注明原创:http://blog.csdn.net/u013608300/article/details/78988523

1、安装

安装过程略,百度一堆,本教程使用版本为V9.103,图1为软件打开时界面,本次介绍添加信号、总线、时钟和分频时钟(add signal. add bus. add clock. add derived clock)的操作。(derived clock,在下理解为派生时钟,为了方便我叫她分频时钟,具体名称望各位指正)

图1 2、添加时钟 时序离不开时钟,在添加信号之前我们先来看看最直观的添加时钟操作,单击图2 add clock。弹出界面如图3

图2 图3是添加clock时弹出的对话框,时钟名称我叫做Clk_50M, 方向为输入,下面3可以设置信号的频率,4可以设置占空比和时钟抖动,抖动时间为0就可以。5为其他参数配置,很方便,大家自己摸索。点ok后波形如图4所示。

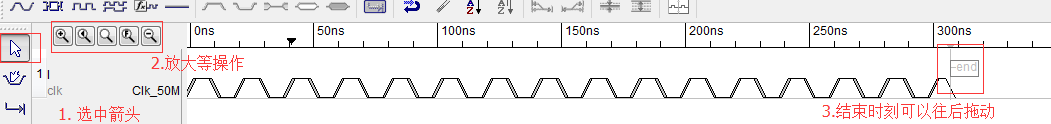

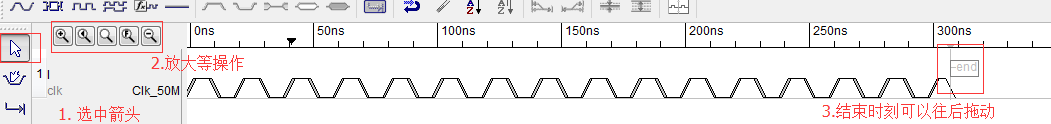

图3 图4是添加进来的时钟,在操作时钟或信号时,一般先选中1的箭头,可以通过2对波形放大等操作,(放大缩小的快捷键是+-),缩小后的波形见图4第二部分,双击图4第二部分中的1,又可以弹出图3,重新对时钟进行编辑。

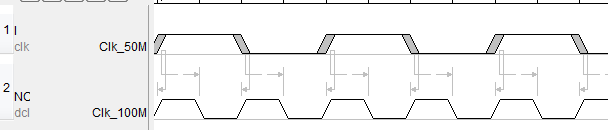

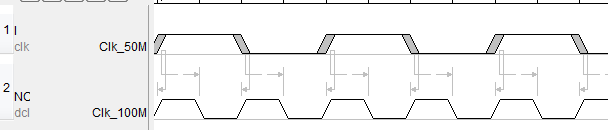

图4 3、分频时钟 添加玩时钟后我们再添加分频时钟,(add deirved clock 叫做分频时钟有点牵强,各位请指出合适的名称),单机 add derived clock,弹出图5。这次我得到一个100M的时钟,名称叫做Clk_100M,这个时钟是内部时钟,3是设置这个时钟的参考时钟,就是2中我们设置的Clk_50M这个时钟,50M/0.5,我们就得到了100M的时钟,延迟设置为0,单击ok效果见图6.

图5 图6我们可以看到这两个时钟为2倍频的关系。

图6 4、添加信号 加下来单击add signal,弹出图7对话框,这里我将信号命名为Rst_n(复位信号,低电平复位),端口方向为输入,初始电平为高

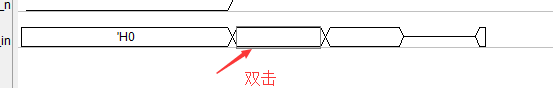

图7 图8为确认后的界面,在我们在箭头所指的地方单机,效果见图8中,我们可以拖动这个方框内的上升沿调整它的时刻位置。在Rst_n后面多单击几次试试。效果见图8下。

图8 5、添加总线 单击add bus,见图9,总线命名data_in, 方向输入,初始值为0(十进制),单击ok后见图10

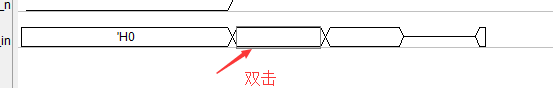

图9 此时图10中还没有bus的波形,在箭头处单击见图10中,图10中内的data_in不连续,先选中不连续处,然后点图10中的2,效果自己看吧

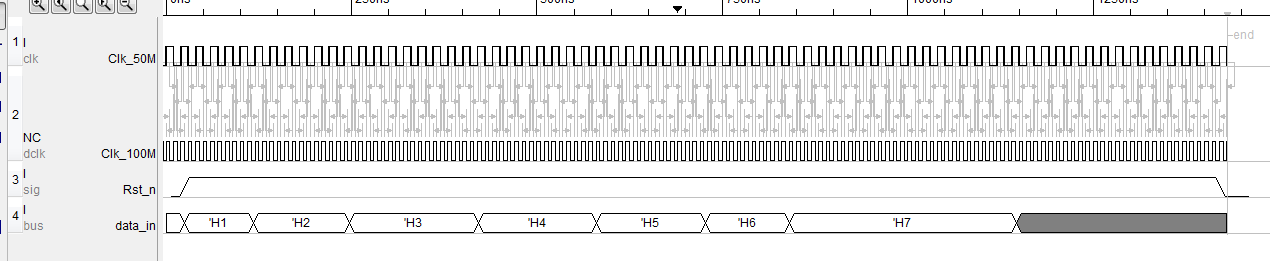

图10 选中图11,然后双击,就可以设置它的值,弹出图12对话框

图11 在图12中设置data_in的数值(十进制)

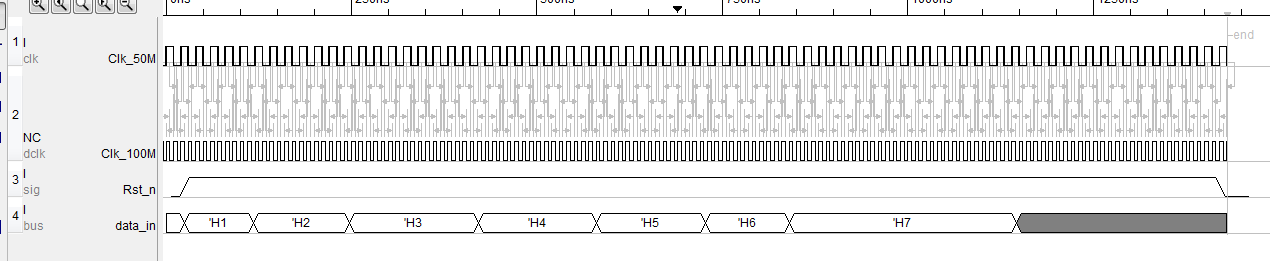

图12 最终效果见图13

图13 基本操作介绍结束,其它内容大家一起探索学习吧。 转帖请注明原创,谢谢。 2018年1月6日 冰三点水 天津

图1 2、添加时钟 时序离不开时钟,在添加信号之前我们先来看看最直观的添加时钟操作,单击图2 add clock。弹出界面如图3

图2 图3是添加clock时弹出的对话框,时钟名称我叫做Clk_50M, 方向为输入,下面3可以设置信号的频率,4可以设置占空比和时钟抖动,抖动时间为0就可以。5为其他参数配置,很方便,大家自己摸索。点ok后波形如图4所示。

图3 图4是添加进来的时钟,在操作时钟或信号时,一般先选中1的箭头,可以通过2对波形放大等操作,(放大缩小的快捷键是+-),缩小后的波形见图4第二部分,双击图4第二部分中的1,又可以弹出图3,重新对时钟进行编辑。

图4 3、分频时钟 添加玩时钟后我们再添加分频时钟,(add deirved clock 叫做分频时钟有点牵强,各位请指出合适的名称),单机 add derived clock,弹出图5。这次我得到一个100M的时钟,名称叫做Clk_100M,这个时钟是内部时钟,3是设置这个时钟的参考时钟,就是2中我们设置的Clk_50M这个时钟,50M/0.5,我们就得到了100M的时钟,延迟设置为0,单击ok效果见图6.

图5 图6我们可以看到这两个时钟为2倍频的关系。

图6 4、添加信号 加下来单击add signal,弹出图7对话框,这里我将信号命名为Rst_n(复位信号,低电平复位),端口方向为输入,初始电平为高

图7 图8为确认后的界面,在我们在箭头所指的地方单机,效果见图8中,我们可以拖动这个方框内的上升沿调整它的时刻位置。在Rst_n后面多单击几次试试。效果见图8下。

图8 5、添加总线 单击add bus,见图9,总线命名data_in, 方向输入,初始值为0(十进制),单击ok后见图10

图9 此时图10中还没有bus的波形,在箭头处单击见图10中,图10中内的data_in不连续,先选中不连续处,然后点图10中的2,效果自己看吧

图10 选中图11,然后双击,就可以设置它的值,弹出图12对话框

图11 在图12中设置data_in的数值(十进制)

图12 最终效果见图13

图13 基本操作介绍结束,其它内容大家一起探索学习吧。 转帖请注明原创,谢谢。 2018年1月6日 冰三点水 天津