http://www.eefocus.com/embedded/323223

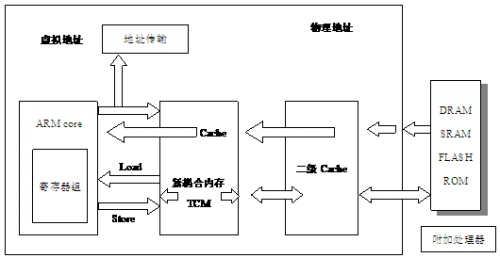

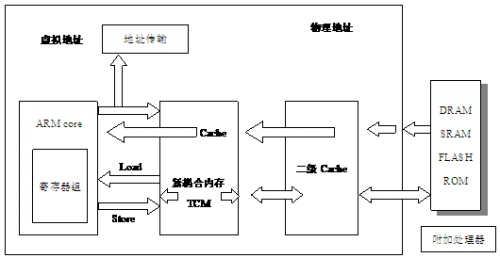

图16.2 ARMv6存储系统示意图

图16.2 ARMv6存储系统示意图

图16.3 ARMv6页表格式

协处理器CP15中的XP-bit可以指定是否使用这种新的页表格式。如果不设置该位,则系统继续使用ARMv5架构的页表格式。

从图16.3可以看出,新的页表格式增加了以下特性:

· XN:从不执行位(execute never bit)。

· nG:非全局地址映射位(not Global bit for address matching)。

应用程序空间指示ASID(Application Space Identifier)是ARMv6体系中增加的又一关键特性。当nG位置位时,地址转换使用虚拟地址和ASID相结合的方法以减少上下文切换的时间。同时,应用程序空间指示提供了一种任务可知调试方法(task-aware debugging)。

有关ARMv6存储系统的详细内容请参阅ARM相关文档。

图16.3 ARMv6页表格式

协处理器CP15中的XP-bit可以指定是否使用这种新的页表格式。如果不设置该位,则系统继续使用ARMv5架构的页表格式。

从图16.3可以看出,新的页表格式增加了以下特性:

· XN:从不执行位(execute never bit)。

· nG:非全局地址映射位(not Global bit for address matching)。

应用程序空间指示ASID(Application Space Identifier)是ARMv6体系中增加的又一关键特性。当nG位置位时,地址转换使用虚拟地址和ASID相结合的方法以减少上下文切换的时间。同时,应用程序空间指示提供了一种任务可知调试方法(task-aware debugging)。

有关ARMv6存储系统的详细内容请参阅ARM相关文档。

该指令根据参数的值来改变默认的数据端格式。

SETEND指令的设置直接和程序状态寄存器CPSR中新增加的E位相对应。E位对数据大小端的控制如图16.4所示。

图16.4 E位对数据大小端的控制

ARMv6对SIMD的实现简单而又不失其灵活性。它将现存的32位ARM数据通道划分成4个8位或2个16位的片段,为SIMD操作增加了独立的数据总线。这种实现方法硬件代价小,遵循了ARM低功耗、高计算效率的设计原则。

为了支持SIMD算法,ARMv6中引入一些新的指令,有关这些指令的详细信息请参阅ARM的相关文档

图16.4 E位对数据大小端的控制

ARMv6对SIMD的实现简单而又不失其灵活性。它将现存的32位ARM数据通道划分成4个8位或2个16位的片段,为SIMD操作增加了独立的数据总线。这种实现方法硬件代价小,遵循了ARM低功耗、高计算效率的设计原则。

为了支持SIMD算法,ARMv6中引入一些新的指令,有关这些指令的详细信息请参阅ARM的相关文档

16.2 ARMv6增加的系统支持

为了满足目前无线网络、汽车电子和消费类电子产品不断增长的市场需要,ARM公司在ARMv6中引入新的技术和结构组成,包括增强的DSP支持和对多处理器环境的支持。16.2.1 存储管理

由于在ARMv6体系结构中引入新的存储管理机制,处理器的整体性能得到提高。在新的体系结构中,平均指令预取和数据等待时间大幅度减少,存取过程中Cache命中率显著提高。由于存储机制的改善,系统整体性能的提高达到30%。 另外,存储系统的改善使系统总线(BUS)使用更加合理,从而减少了系统总线使用频度,降低了系统功耗。 图16.2显示了ARMv6体系结构存储系统示意图。 图16.2 ARMv6存储系统示意图

图16.2 ARMv6存储系统示意图

1.ARMv6 L1 Cache

ARMv6采用“分层”的存储管理,存储层次的最顶层在处理器内核中。该存储器被称为寄存器文件(register file)。这些寄存器被集成在处理器内核中,在系统中提供最快的存储访问。 ARMv6体系结构处理器使用物理索引Cache(Physically tagged caches),即地址转换在CPU和Cache之间,这样就减少了CPU在运行大的操作系统时由于上下文切换而带来的系统开销。使用这种物理Cache,可以使CPU的整体性能提高近20%。 为了减少在内容转换时,刷新Cache的CPU开销,ARMv6将L1 Cache构建为使用物理寻址的存储系统。系统中设有TCM作为物理可寻址的快速访问内存,存在于存储系统中,作为Cache的补充。无论Cache还是TCM,都可以配置为指令和数据分离的Harvard架构或指令和数据统一的冯·诺依曼架构。另外,L1 DMA子系统可以使数据在没有CPU参与的情况下,直接和TCM进行数据传输。2.页表格式

在ARMv6体系结构中,页表格式也发生了变化。图16.3显示了新的一级页表格式。 图16.3 ARMv6页表格式

协处理器CP15中的XP-bit可以指定是否使用这种新的页表格式。如果不设置该位,则系统继续使用ARMv5架构的页表格式。

从图16.3可以看出,新的页表格式增加了以下特性:

· XN:从不执行位(execute never bit)。

· nG:非全局地址映射位(not Global bit for address matching)。

应用程序空间指示ASID(Application Space Identifier)是ARMv6体系中增加的又一关键特性。当nG位置位时,地址转换使用虚拟地址和ASID相结合的方法以减少上下文切换的时间。同时,应用程序空间指示提供了一种任务可知调试方法(task-aware debugging)。

有关ARMv6存储系统的详细内容请参阅ARM相关文档。

图16.3 ARMv6页表格式

协处理器CP15中的XP-bit可以指定是否使用这种新的页表格式。如果不设置该位,则系统继续使用ARMv5架构的页表格式。

从图16.3可以看出,新的页表格式增加了以下特性:

· XN:从不执行位(execute never bit)。

· nG:非全局地址映射位(not Global bit for address matching)。

应用程序空间指示ASID(Application Space Identifier)是ARMv6体系中增加的又一关键特性。当nG位置位时,地址转换使用虚拟地址和ASID相结合的方法以减少上下文切换的时间。同时,应用程序空间指示提供了一种任务可知调试方法(task-aware debugging)。

有关ARMv6存储系统的详细内容请参阅ARM相关文档。

3.增加的页表基地址寄存器

为了提高地址转换的处理速度,ARMv6体系结构中增加了一个新的页表基地址寄存器,以存储二级页表的基地址。CP15同时支持TTBR0和TTBR1。专门的控制寄存器用来保存用户设定的整数N,N的取值范围为0~7。当N的值不等于0时,0~232-N的地址空间使用TTBR0,而其他空间使用TTBR1进行传输控制。一级页表根据N取值的不同,占有128bytes~16KB存储空间。16.2.2 多处理单元支持

由于片上系统Soc结构的复杂化,ARM内核现在经常被用于有多个处理单元的设备,这些处理单元竞争使用系统的共享资源。为了满足多处理单元任务间同步的需要,Load/Store互斥指令引入到新的ARMv6体系结构中来。新指令包括: · LDREX:加载互斥指令。 · STREX:存储互斥指令。 LDREX指令从存储器中装载一个值到寄存器,在处理这个数据时,不会有任何其他因素改变该值。STREX指令存储一个值到寄存器,并返回一个指示值。16.2.3 异常处理和中断

ARMv6体系结构提供了对向量中断(vectored Interrupt)的支持。向量中断控制器(VIC,Vectored Interrupt Controller)由CP15的寄存器1中的VE – bit来控制。当向量中断控制器使能时,该控制器可以向CPU提供发生中断的向量。 另外,在ARMv6的体系结构中,程序状态寄存器CPSR扩展了A位来控制Abort异常。这种机制类似于程序状态寄存器CPSR中I和F bit对IRQ和FIQ的控制。 操作系统通常在堆栈中保存一次中断或异常处理的返回状态。ARMv6增加了新的指令来提高这类操作的效率。这种操作在中断/调度程序驱动系统中,出现的频率是很高的。这些新增加的指令包括: · SRS:保存返回状态在特定模式的堆栈中。 · RFE:异常返回。 · CPSID/CPSIE:改变处理器状态,开中断或关中断。16.2.4 混和大小端支持

AMRv6体系结构中增加了同时处理大端和小端数据的能力。新增加了指令SETEND来设置一段代码处理数据的字节排列方式,另外还增加了一些单独的处理指令来提高在混和大小端环境下的处理效率。 指令SETEND的标准格式如下: SETEND16.2.5 对媒体处理的支持

为了进一步提高体系结构的DSP和媒体处理能力,单指令流多数据流(SIMD)技术被引入到ARMv6体系结构中。这种技术对于处理大量复杂运算和并行地存储大流量数据十分有效。 图16.4 E位对数据大小端的控制

ARMv6对SIMD的实现简单而又不失其灵活性。它将现存的32位ARM数据通道划分成4个8位或2个16位的片段,为SIMD操作增加了独立的数据总线。这种实现方法硬件代价小,遵循了ARM低功耗、高计算效率的设计原则。

为了支持SIMD算法,ARMv6中引入一些新的指令,有关这些指令的详细信息请参阅ARM的相关文档

图16.4 E位对数据大小端的控制

ARMv6对SIMD的实现简单而又不失其灵活性。它将现存的32位ARM数据通道划分成4个8位或2个16位的片段,为SIMD操作增加了独立的数据总线。这种实现方法硬件代价小,遵循了ARM低功耗、高计算效率的设计原则。

为了支持SIMD算法,ARMv6中引入一些新的指令,有关这些指令的详细信息请参阅ARM的相关文档