该篇是FPGA数字信号处理的第四篇,选题为DSP系统中极其常用的FIR滤波器。本文将在前两篇的基础上,继续介绍在Quartus开发环境下使用Altera(或者叫Intel)提供的FIR IP核进行FIR滤波器的设计。

1.“FPGA数字信号处理(二)并行FIR滤波器Verilog设计” https://blog.csdn.net/fpgadesigner/article/details/80594627

2.“FPGA数字信号处理(三)串行FIR滤波器Verilog设计” https://blog.csdn.net/fpgadesigner/article/details/80598992

一种是集成在“IP Catalog”和qsys中:

两种Quartus版本下的IP核,从使用者的角度来看仅仅是配置界面不同,在参数设置和使用方法上基本一致。本文以“MegaWizard Plug-In Manager”中的FIR Compiler IP核使用为例。

两种Quartus版本下的IP核,从使用者的角度来看仅仅是配置界面不同,在参数设置和使用方法上基本一致。本文以“MegaWizard Plug-In Manager”中的FIR Compiler IP核使用为例。

Quartus的FIR IP核属于收费IP,如果是个人学习使用需要对IP核单独破解。在Quartus的破解licence文件中找到下段代码,在licence最后复制粘贴一份,将“FEATURE 6AF7_XXXX”中的XXXX改成FIR IP核对应的编号“0012”。保存后重新打开Quartus,在License Setup页面看到FIR Compiler的破解信息,则可以正常使用。

不过这个滤波器设计功能没有MATLAB的FDATOOL那么强大,也可以用MATLAB生成滤波器系数,存入txt文件中,在上面界面的“Imported Coefficient Set”中导入txt文件。

FIR Compiler IP核可以在主界面的structure中选择滤波器的四种结构,包括三种分布式算法结构:全并行、全串行和多比特串行,另外一种固定/可变系数的多时钟周期结构。如果设计时不需要改变滤波器系数,则选择四种结构的一种;如果需要在设计中重载滤波器系数,则必须选择最后一种结构。 “coefficients scaling”中可以选择滤波器系数的量化方式,“Bit width”中选择量化位宽,上面的图中可以看到滤波器的频率响应。 “Output Sepecification”中可以设置滤波器的输出方式和位宽,IP核会根据输入的数据位宽和其它参数设置自动计算输出数据的位宽。 IP核支持多通道数据输入,可以在“Number of Inpu Channels”中设置输入数据的通道数。另外设置FPGA型号、数据存储方式、系数存储方式、流水线级数、输入数据位宽等常规参数。

设置完成后可以生成IP核。老版本的IP核会自动加入到工程中;新版本的IP核集成在qsys中,需要手动在file中将IP核对应的qip文件加入工程。 在设置为多通道、可变系数模式时,还会用到其它的接口。上表中的接口已经足够完成一次单通道、固定系数的FIR滤波器设计。其它接口在后文的设计中使用到FIR滤波器的其它模式时,再做介绍。

在设置为多通道、可变系数模式时,还会用到其它的接口。上表中的接口已经足够完成一次单通道、固定系数的FIR滤波器设计。其它接口在后文的设计中使用到FIR滤波器的其它模式时,再做介绍。

FIR IP核的相关文档如上图所示。注意,在altera卖身给intel后,官网进行了大改,目前老版本的quartus中的IP核点击“documentation”时已经成了error,即官网已经没有了相关文档。

FIR IP核的相关文档如上图所示。注意,在altera卖身给intel后,官网进行了大改,目前老版本的quartus中的IP核点击“documentation”时已经成了error,即官网已经没有了相关文档。

单通道、固定系数的FIR Compiler接口时序非常简单,Verilog HDL示例代码如下所示:

明显看到经过500Hz低通滤波器滤波后,输入的200+800Hz信号只剩下200Hz的单频信号。

完整的Quartus工程(含testbench仿真)可以在这里下载:https://download.csdn.net/download/fpgadesigner/10464189。

2.“FPGA数字信号处理(三)串行FIR滤波器Verilog设计” https://blog.csdn.net/fpgadesigner/article/details/80598992

IP核概述

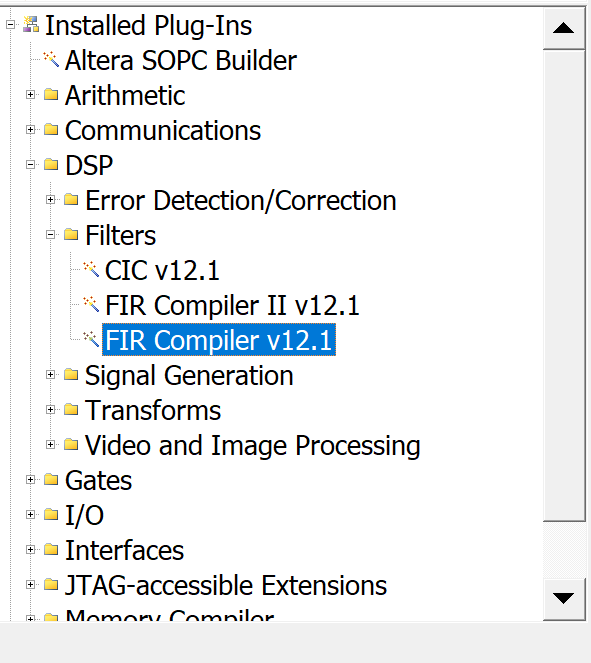

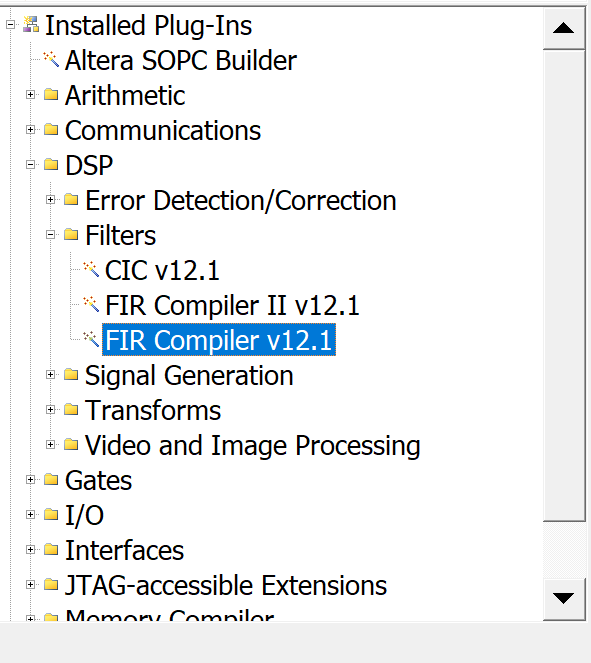

由于版本的关系,Quartus提供的IP核有两种,一种是集成在“MegaWizard Plug-In Manager”中:

一种是集成在“IP Catalog”和qsys中:

两种Quartus版本下的IP核,从使用者的角度来看仅仅是配置界面不同,在参数设置和使用方法上基本一致。本文以“MegaWizard Plug-In Manager”中的FIR Compiler IP核使用为例。

两种Quartus版本下的IP核,从使用者的角度来看仅仅是配置界面不同,在参数设置和使用方法上基本一致。本文以“MegaWizard Plug-In Manager”中的FIR Compiler IP核使用为例。 Quartus的FIR IP核属于收费IP,如果是个人学习使用需要对IP核单独破解。在Quartus的破解licence文件中找到下段代码,在licence最后复制粘贴一份,将“FEATURE 6AF7_XXXX”中的XXXX改成FIR IP核对应的编号“0012”。保存后重新打开Quartus,在License Setup页面看到FIR Compiler的破解信息,则可以正常使用。

FEATURE 6AF7_XXXX alterad 2035.12 permanent uncounted E75BE809707E

VENDOR_STRING="iiiiiiiihdLkhIIIIIIIIUPDuiaaaaaaaa11X38DDDDDDDDpjz5cddddddddtmGzGJJJJJJJJbqIh0uuuuuuuugYYWiVVVVVVVVbp0FVHHHHHHHHBUEakffffffffD2FFRkkkkkkkkWL$84"

HOSTID=b025aa21c82f TS_OK SIGN="1E27 C980 33CD 38BC 5532 368B

116D C1F8 34E0 5436 99A0 5A2E 1C8C 8DD0 C9C6 011B A5A9 932B

08DE C5ED 9E62 2868 5A32 6397 D9B8 5C3A B8E8 4E4F CEC7 C836"

IP核参数设置

像MATLAB一样,FIR Compiler也提供了设计FIR滤波器和生成滤波器系数的功能,点击“New Coffcient Set”,界面如下:

不过这个滤波器设计功能没有MATLAB的FDATOOL那么强大,也可以用MATLAB生成滤波器系数,存入txt文件中,在上面界面的“Imported Coefficient Set”中导入txt文件。

FIR Compiler IP核可以在主界面的structure中选择滤波器的四种结构,包括三种分布式算法结构:全并行、全串行和多比特串行,另外一种固定/可变系数的多时钟周期结构。如果设计时不需要改变滤波器系数,则选择四种结构的一种;如果需要在设计中重载滤波器系数,则必须选择最后一种结构。 “coefficients scaling”中可以选择滤波器系数的量化方式,“Bit width”中选择量化位宽,上面的图中可以看到滤波器的频率响应。 “Output Sepecification”中可以设置滤波器的输出方式和位宽,IP核会根据输入的数据位宽和其它参数设置自动计算输出数据的位宽。 IP核支持多通道数据输入,可以在“Number of Inpu Channels”中设置输入数据的通道数。另外设置FPGA型号、数据存储方式、系数存储方式、流水线级数、输入数据位宽等常规参数。

设置完成后可以生成IP核。老版本的IP核会自动加入到工程中;新版本的IP核集成在qsys中,需要手动在file中将IP核对应的qip文件加入工程。

IP核接口说明

Quartus的很多IP核采用的是Avalon-ST接口,主要有数据(data)、准备好(ready)、有效(valid)和错误(error)几种信号。Avalon-ST接口本身也支持时分复用来完成多通道同步(channel),因此FIR Compiler支持多通道数据处理。 FIR Compiler支持重载滤波器系数,但系数重载的相关端口(coed_set、coed_in_clk、coed_set_in、coed_in、coed_we、coed_ld)不被Avalon-ST接口支持,不属于该类型接口。 接下来介绍几个主要的接口: 在设置为多通道、可变系数模式时,还会用到其它的接口。上表中的接口已经足够完成一次单通道、固定系数的FIR滤波器设计。其它接口在后文的设计中使用到FIR滤波器的其它模式时,再做介绍。

在设置为多通道、可变系数模式时,还会用到其它的接口。上表中的接口已经足够完成一次单通道、固定系数的FIR滤波器设计。其它接口在后文的设计中使用到FIR滤波器的其它模式时,再做介绍。

FPGA设计

IP核的接口在Verilog HDL中进行设计时,一定要参考官方文档中给出的时序图。在IP核的配置界面点击“documentation”,可以找到IP核的data sheet、user guide和release notes。 FIR IP核的相关文档如上图所示。注意,在altera卖身给intel后,官网进行了大改,目前老版本的quartus中的IP核点击“documentation”时已经成了error,即官网已经没有了相关文档。

FIR IP核的相关文档如上图所示。注意,在altera卖身给intel后,官网进行了大改,目前老版本的quartus中的IP核点击“documentation”时已经成了error,即官网已经没有了相关文档。 单通道、固定系数的FIR Compiler接口时序非常简单,Verilog HDL示例代码如下所示:

module FirIPDa

(

input reset_n, //复位信号,低电平有效

input clk, //FPGA系统时钟/数据速率:2kHz

input signed [11:0] Xin, //数据输入频率为2kHZ

output signed [24:0] Yout //滤波后的输出数据

);

wire source_valid, sink_ready;

wire [1:0] source_error;

wire sink_valid = 1'b1;

fir_par fir_inst

(

.clk (clk), //输入,时钟信号

.reset_n (reset_n), //输入,低电平有效复位

.ast_sink_data (Xin), //输入,采样输入数据

.ast_sink_valid (sink_valid), //输入,置1时向FIR滤波器输入数据

.ast_source_ready (1'b1), //输入,源准备好

.ast_sink_error (2'd0), //输入,标识信宿端出现的错误

.ast_source_data (Yout), //输出,滤波器输出,位宽与设计的滤波器参数有关

.ast_sink_ready (sink_ready), //输出,

.ast_source_valid (source_valid), //输出,FIR输出数据有效时该信号置位

.ast_source_error (source_error) //输出,标识信源端出现的错误

);

endmodule

程序中认为输入的采样数据始终有效,因此将sink_valid永远置1。另外将source_ready永远置1,且忽视sink_ready信号,可以获得最高的FIR计算时钟速率。

仿真与工程下载

使用MATLAB生成一个200khz+800kHz的混合频率信号,写入txt文件,。编写Testbench读取txt文件对信号滤波,文件操作方法参考“Testbench编写指南(一)文件的读写操作”https://blog.csdn.net/fpgadesigner/article/details/80470972。 使用Quartus调用ModelSim进行仿真,对正弦信号的滤波如下图所示:

明显看到经过500Hz低通滤波器滤波后,输入的200+800Hz信号只剩下200Hz的单频信号。

完整的Quartus工程(含testbench仿真)可以在这里下载:https://download.csdn.net/download/fpgadesigner/10464189。