上篇博文:半带 FIR 滤波器(Half-band FIR Filter)

希尔伯特变换在数字通信系统中有很多种使用方式。理想的希尔伯特变换为正频率提供90度的相移,为负频率提供-90度的相移。

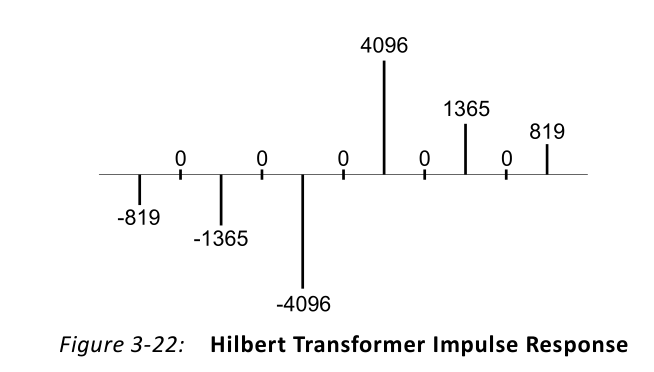

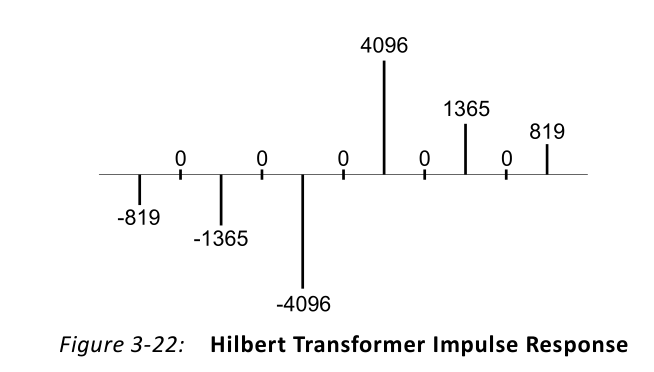

希尔伯特变换接收一个实值信号,并且产生一个复的 (I, Q)输出信号。输出信号的正交部分(Q)由如图 3-22所示冲激响应的 FIR 滤波器产生。同相分量(I)是输入信号经过延时后的结果,延时时间长度由FIR处理过程得到Q输出所需要的相位延时决定,即延时补偿。 通过访问Q通道FIR滤波器的采样历史延迟的中心抽头可以有效地实现这一点,如图3-23所示。 在该图中,x(n)是实值输入信号,y I(n)和y Q(n)分别是同相和正交输出。

通过访问Q通道FIR滤波器的采样历史延迟的中心抽头可以有效地实现这一点,如图3-23所示。 在该图中,x(n)是实值输入信号,y I(n)和y Q(n)分别是同相和正交输出。

Hilbert变换的频域冲激响应应是奇对称的,而且系数也是零值和非零值相间的,利用这个特点可以得到有效的硬件实现结构。下图给出了利用Hilbert变换冲激响应的对称性和零值与非零值相间特点实现Hirbert变换的电路结构。

Hilbert变换的频域冲激响应应是奇对称的,而且系数也是零值和非零值相间的,利用这个特点可以得到有效的硬件实现结构。下图给出了利用Hilbert变换冲激响应的对称性和零值与非零值相间特点实现Hirbert变换的电路结构。

本博文内容来源于Xilinx官方数据手册:LogiCORE IP FIR Compiler v7.1版本

下篇博文:【 FPGA 】FIR 滤波器之内插 FIR 滤波器(Interpolated FIR Filter)

本博文内容来源于Xilinx官方数据手册:LogiCORE IP FIR Compiler v7.1版本

下篇博文:【 FPGA 】FIR 滤波器之内插 FIR 滤波器(Interpolated FIR Filter)

希尔伯特变换接收一个实值信号,并且产生一个复的 (I, Q)输出信号。输出信号的正交部分(Q)由如图 3-22所示冲激响应的 FIR 滤波器产生。同相分量(I)是输入信号经过延时后的结果,延时时间长度由FIR处理过程得到Q输出所需要的相位延时决定,即延时补偿。

通过访问Q通道FIR滤波器的采样历史延迟的中心抽头可以有效地实现这一点,如图3-23所示。 在该图中,x(n)是实值输入信号,y I(n)和y Q(n)分别是同相和正交输出。

通过访问Q通道FIR滤波器的采样历史延迟的中心抽头可以有效地实现这一点,如图3-23所示。 在该图中,x(n)是实值输入信号,y I(n)和y Q(n)分别是同相和正交输出。

Hilbert变换的频域冲激响应应是奇对称的,而且系数也是零值和非零值相间的,利用这个特点可以得到有效的硬件实现结构。下图给出了利用Hilbert变换冲激响应的对称性和零值与非零值相间特点实现Hirbert变换的电路结构。

Hilbert变换的频域冲激响应应是奇对称的,而且系数也是零值和非零值相间的,利用这个特点可以得到有效的硬件实现结构。下图给出了利用Hilbert变换冲激响应的对称性和零值与非零值相间特点实现Hirbert变换的电路结构。

本博文内容来源于Xilinx官方数据手册:LogiCORE IP FIR Compiler v7.1版本

下篇博文:【 FPGA 】FIR 滤波器之内插 FIR 滤波器(Interpolated FIR Filter)

本博文内容来源于Xilinx官方数据手册:LogiCORE IP FIR Compiler v7.1版本

下篇博文:【 FPGA 】FIR 滤波器之内插 FIR 滤波器(Interpolated FIR Filter)