6678学习笔记开篇

从事6678开发一段时间,一直有写点东西的冲动。专门讲6678底层开发的书籍比较少,或者比较粗略,网上搜的一些东西也零零散散,看的意犹未尽。不像2812,6713那样有详尽的手册翻译、其他中文资料和代码解读,印象比较深的就是《手把手教你学DSP》,前辈的积累和分享精神值得学习。在此,计划以手册解读+代码解读+程序实战的形式和大家分享6678的开发经验,也作为自己学习和思考和总结的笔记,欢迎大家批评指正,交流学习,一起进步。 首先分享给大家一些资料和链接,方便大家查找,这些资料大多是从官网下载的,也有从TI技术论坛、61论坛、某宝、某鱼、文库、PUND、CSDN、 {MOD}等地方下载的。哈哈,想起刚接触时从某鱼花了200大洋买的资料,结果和之前自己下载的一模一样(店家愣说不一样不退货,都不容易,忍了)。在这里,你不用为积分头疼,希望大家有资料也分享给我呀,众里寻他千百度的认知过程也蛮心酸的。TI技术论坛C6000多核开发的链接:https://e2echina.ti.com/question_answer/dsp_arm/c6000_multicore/ 源码K1_STK_v1下载链接:https://e2echina.ti.com/question_answer/dsp_arm/c6000_multicore/f/53/t/47664 应用手册和用户指南:哈哈,省的您从官网一点一点下载了,。 链接:https://pan.baidu.com/s/1TnXBwA0-tpTUeh0PdWfk-A 提取码:6mib 其他资料链接: https://pan.baidu.com/s/1t2x5ko-5giJjdBBcpmU6iA 提取码:al9h 创龙的资料,其他资料随文章内容变化持续上传更新。 开发环境: CCS5.4,仿真器SEED560,CCS5.4软件下载链接: http://processors.wiki.ti.com/index.php/Download_CCS,其他版本也在这里。 bios_mcsdk_02_01_02_06_setup的链接: http://software-dl.ti.com/sdoemb/sdoemb_public_sw/bios_mcsdk/02_01_02_06/index_FDS.html 注意patch是补丁记得下载。破解license请见下期开发环境的安装。

好了,开始上干货吧。本期主要对6678的多核处理器内核中央处理单元和DSP工作机制进行详细介绍,作为了解6678的基础,下一期介绍开发环境的安装。

TMS320C6678 DSP多核处理器内核(一)

——中央处理单元及其工作机制1.内核结构:

内核的功能框图如图所示。今天我们主要圈红部分A&B结构的中央处理单元进行学习,了解DSP核心的处理和运行机制,其他部分后续单独作为重点了解学习。

1.1 A&B结构的中央处理单元

66系列内核和64、67系列具有一个相同的特点是采用基本的A&B架构。内核由A和B两部分组成,每部分由四个功能单元组成,即.D、.L、.S、.M。结构如图所示 A、B通道的Register File都包含32个通用32位寄存器A0-A31、B0-B31,支持8位到128位的定点数据,比如大于32位的数据由两个通用寄存器表示,大于64位的用四个通用寄存器组成的一组表示。组对形式如下图所示。

A、B通道的Register File都包含32个通用32位寄存器A0-A31、B0-B31,支持8位到128位的定点数据,比如大于32位的数据由两个通用寄存器表示,大于64位的用四个通用寄存器组成的一组表示。组对形式如下图所示。

接下来我们学习一下L、S、D、M各个单元的主要功能。数据从内存到处理单元再到内存的处理运算过程就是由这些单元协作完成。

L单元和S单元主要进行算数、逻辑运算和指令分支等功能。

D单元:主要将内存中的数据搬移到Register File中,或者将结果从Register File搬移到内存中。

M单元主要为乘法器单元。6678由16个16位乘法器组组成,每四个组成一组协同工作,从而实现内核原始计算能力提升四倍。

如下图所示。各个单元涉及的汇编指令不同,也有部分重叠,从中我们可以看到四个不同单元的分工,更为详尽的信息请见CPU Instruction手册附表。当然如果我们在开发环境下完全使用C语言编程处理,大部分时候是用不到这些知识的。

接下来我们学习一下L、S、D、M各个单元的主要功能。数据从内存到处理单元再到内存的处理运算过程就是由这些单元协作完成。

L单元和S单元主要进行算数、逻辑运算和指令分支等功能。

D单元:主要将内存中的数据搬移到Register File中,或者将结果从Register File搬移到内存中。

M单元主要为乘法器单元。6678由16个16位乘法器组组成,每四个组成一组协同工作,从而实现内核原始计算能力提升四倍。

如下图所示。各个单元涉及的汇编指令不同,也有部分重叠,从中我们可以看到四个不同单元的分工,更为详尽的信息请见CPU Instruction手册附表。当然如果我们在开发环境下完全使用C语言编程处理,大部分时候是用不到这些知识的。

1.2 中央处理单元数据和控制寄存器访问路径

如上图所示,DA1和DA2表示数据地址路径,分别连接D1和D2。

LD1和LD2表示Register File从存储中将数据读取,LD1a、LD2a为低32位,LD1b、LD2b为高32位。

ST1和ST2表示Register File将数据写入到存储中,ST1a、ST2a为低32位,ST1b、ST2b为高32位。

内部数据A、B功能单元都可以访问自己同侧的Register File,比如A的L1、S1、M1、D1可以直接访问同侧的Register File A。同时,也可以通过交叉通道1X和2X访问对侧的Register File,提高了CPU的处理效率。

内核的中断、异常等控制寄存器,如图所示。

如上图所示,DA1和DA2表示数据地址路径,分别连接D1和D2。

LD1和LD2表示Register File从存储中将数据读取,LD1a、LD2a为低32位,LD1b、LD2b为高32位。

ST1和ST2表示Register File将数据写入到存储中,ST1a、ST2a为低32位,ST1b、ST2b为高32位。

内部数据A、B功能单元都可以访问自己同侧的Register File,比如A的L1、S1、M1、D1可以直接访问同侧的Register File A。同时,也可以通过交叉通道1X和2X访问对侧的Register File,提高了CPU的处理效率。

内核的中断、异常等控制寄存器,如图所示。

内核的S2单元通过MVC指令可以访问控制寄存器,在指令的E1阶段完成。

AMR控制寄存器主要对地址的模式等进行配置,如线性和环形模式。CSR寄存器主要表征了CPU的版本信息,上电等信息。CPPGFR主要控制伽罗瓦场多项式发生器。ICR、IER、IFR、IRP、ISTP、NRP为中断相关寄存器,其中ISTP和CMD文件中中断向量表段的起始地址一致。DNUM为核号寄存。其他寄存器意义详见手册。

内核的S2单元通过MVC指令可以访问控制寄存器,在指令的E1阶段完成。

AMR控制寄存器主要对地址的模式等进行配置,如线性和环形模式。CSR寄存器主要表征了CPU的版本信息,上电等信息。CPPGFR主要控制伽罗瓦场多项式发生器。ICR、IER、IFR、IRP、ISTP、NRP为中断相关寄存器,其中ISTP和CMD文件中中断向量表段的起始地址一致。DNUM为核号寄存。其他寄存器意义详见手册。

1.3 流水线(pipeline)指令执行

本节首先学习了单条DSP指令执行的过程,然后引出流水线的含义。1.3.1 DSP指令的执行过程

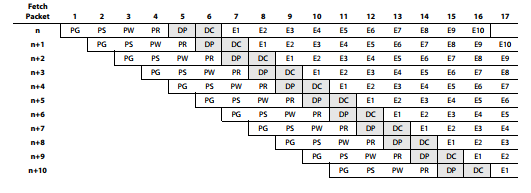

DSP指令的执行分为三个阶段,取指(Fetch)、译码(Decode)、执行(Execute)。 (1)取指阶段 取指分为四个阶段,如图所示: PG: Program address generate

PS: Program address send

PW: Program access ready wait

PR: Program fetch packet receive

CPU发送第一个取指包(FP)后进入PG阶段,CPU生成程序地址;在PS阶段,CPU发送地址到内存;PW阶段发生内存读取,在PR阶段程序指令进入CPU。

(2)译码阶段

译码分为两个阶段,如图所示。

PG: Program address generate

PS: Program address send

PW: Program access ready wait

PR: Program fetch packet receive

CPU发送第一个取指包(FP)后进入PG阶段,CPU生成程序地址;在PS阶段,CPU发送地址到内存;PW阶段发生内存读取,在PR阶段程序指令进入CPU。

(2)译码阶段

译码分为两个阶段,如图所示。

DP:Instruction dispatch

DC:Instruction decode

在DP阶段,指令被分发到合适的功能单元;在DC阶段,指令的源地址、目标地址和相关的执行路径被译码,为功能单元的执行指令做准备。

(3)执行阶段

执行阶段被分为5个阶段,E1-E5。不同的指令,使用E1-E5阶段的数量不同,耗时不同。

DP:Instruction dispatch

DC:Instruction decode

在DP阶段,指令被分发到合适的功能单元;在DC阶段,指令的源地址、目标地址和相关的执行路径被译码,为功能单元的执行指令做准备。

(3)执行阶段

执行阶段被分为5个阶段,E1-E5。不同的指令,使用E1-E5阶段的数量不同,耗时不同。

(4)完整过程

(4)完整过程

1.3.2 DSP流水线执行特点

在上一节中,主要讲述的单条DSP指令的执行过程。那么什么是流水线式的执行方式呢。先给大家讲个故事。 1913年,福特应用创新理念和反向思维逻辑提出在汽车组装中,汽车底盘在传送带上以一定速度从一端向另一端前行.前行中,逐步装上发动机,操空系统,车厢,方向盘,仪表,车灯,车窗玻璃、车轮,一辆完整的车组装成了.第一条流水线使每辆T型汽车的组装时间由原来的12小时28分钟缩短至10秒钟,生产效率提高了4488倍! 流水线是把一个重复的过程分为若干个子过程,每个子过程可以和其他子过程并行运作.福特的流水线不仅把汽车放在流水线上组装,也花费大量精力研究提高劳动生产率.福特把装配汽车的零件装在敞口箱里,放在输送带上,送到技工面前,工人只需站在输送带两边,节省了来往取零件的时间.而且装配底盘时,让工人拖着底盘通过预先排列好的一堆零件,负责装配的工人只需安装,这样装配速度自然加快了。 同理,将DSP的指令执行分为三个子过程,这三个子过程通过若干个通道交叉并行运转,大大提高了DSP指令执行的速率,不用等上一条指令完全执行完毕就可以运行其他指令。如下图所示。