origin: http://www.eepw.com.cn/article/201603/287859.htm

全球主要的电信晶片供应商高通(Qualcomm)、DSP核心供应商CEVA以及处理器核心业者ARM,均竞相迎接这一挑战。三家公司均已开发出新的处理 器架构,并抢先在今年的世界行动通讯大会(MWC)之前发布。高通宣布Snapdragon X16、CEVA发表CEVA-X4,ARM则畅谈其新款Cortex-R8。

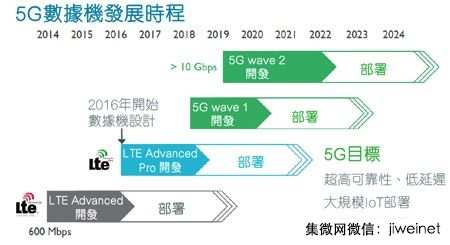

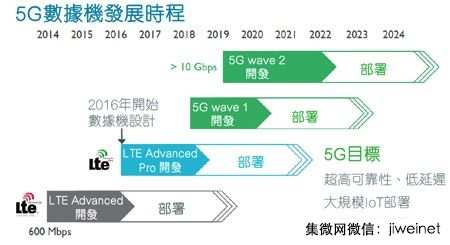

本文引用地址:http://www.eepw.com.cn/article/201604/289387.htm 高通新款数据机晶片在其Hexagon DSP核心中执行密集的LTE协定和语音编解码器(codec),同时还采用ARM Cortex执行Linux作业系统(OS)、IMS和IP堆叠。 挑战何在? 那么,这些新的基频数据机有何不同之处? 与 该技术有关的议题包括:增加载波聚合(CA)、将多重无线存取技术(Multi-RAT)整并于单一数据机、切换不同数据机时的低延迟作业、同步处理双基 地台以及伴随VoLTE高品质语音通话服务而来的复杂度等。根据CEVA,新的基频据机必须能够处理上述所有或更多的问题。 The Linley Group资深分析师Mike Demler呼吁为现有的数据机晶片架构进行“全面体检”,“才能满足LTE Advanced(LTE-A)与LTE-A Pro标准日益严格的性能和功耗限制。” 因此,存在于高通、CEVA和ARM三方之间的竞赛,开始转变成为针对处理器、硬体加速与DSP的全新战场。 供应商们正积极讨论在Layer 1实体(PHY)控制器、Layer 2和layer 3处理之间增加的LTE基频工作负载应该如何进行最佳化处理;以及应该采用先进的DSP核心、强化的处理器核心或是二者兼用的组合? 各据不同势力范围的每一家供应商显然有着不同的想法。 高通发表先进的LTE数据机Snapdragon X16,用于支援LTE-A Pro Category 16高达1 Gbps传输速率的下行链路以及实现Category 13高达150Mbps的上传速度。

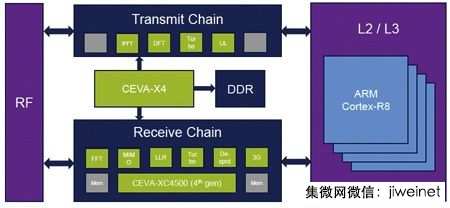

高通最新Snapdragon X16支援高达1 Gbps的下载速度,号称是行动产业首款Gigabit级的LTE数据机 为了不让高通专美于前,CEVA和ARM也发布自家最新设计的核心——分别是CEVA-X4与ARM Cortex-R8,他们表示最新的架构已经准备好迎接LTE-A Pro数据机的挑战了。不过,目前还没有任何一款商用基频晶片采用任一家IP供应商的处理器核心。 因 应LTE-A Pro数据机晶片日益增加的处理需求,两家IP核心供应商显然采取了全然不同的发展重点。例如,CEVA以CEVA-X4更新其L1 PHY控制器。相反地,ARM则透过其最新设计的四核心Cortex-R8,专注于满足针对Layer 2与L3软体处理持续增加的需求。 Demler明确指出,Cortex-R8和CEVA-X4是两种完全不同的核心。CEVA-X4用于PHY层控制,而ARM Cortex-R则否。他强调,“X4和R8可能在一款数据机应用中共存,让X4处理实体层,而Cortex-R则处理更高层级的控制功能。”

CEVA-X4与ARM Cortex-R8可能共存于下一代数据机晶片中? 遭遇瓶颈 CEVA行销与企业发展副总裁Eran Briman指出,在详细研究最新先进基频数据机的需求后,“我们发现PHY控制器在下一代基频中的瓶颈。” 藉由为基频应用重新定义处理控制和资料平面的性能和能效,CEVA开发出全新的CEVA-X DSP架构。 CEVA-X4是来自CEVA-X架构的首款授权核心。虽然DSP一直是CEVA的强项,但Demler 认为,CEVA-X4更像是“一款具有DSP功能的控制器。” CEVA无线业务部业务开发总监Emmanuel Gresset解释,在CEVA-X4中增加的CEVA先进DSP功能结合了控制层处理,以及“协同处理器和硬体加速的支援。” 他认为CEVA-X4是一种“全新的处理器类型,它能在DSP与控制之间实现真正的平衡。” Gresset 还指出,CEVA-X4的CoreMark/MHz基准达到了4.0。CoreMark是专为嵌入式系统衡量CPU性能的基准。Gresset说,这对于 CEVA来说是非常重要的,因为CEVA-X4目前可说是“与ARM Cortex-R7/R8不相上下。”

新的CEVA-X4架构充份结合控制器与DSP处理器,瞄准手机、IoT装置以及下一代5G基频数据机等应用 捍卫L2/L3处理领域 ARM一直是智慧型手机市场中首屈一指的CPU核心供应商。 ARM先进技术行销总监Chris Turner解释,“ARM Cortex-R7目前部署于大量3G/4G智慧型手机数据机中,Cortex-R4和Cortex-R5也用于ARM合作夥伴的数据机产品中。” 藉着Cortex-R8的推出,ARM计划满足对于协议软体处理以及LTE-A Pro与第一代5G日益增加的需求。他并补充说,“我们期望看到新的基频设计提升到采用Cortex-R8。” 值得注意的是,Cortex-R是为硬即时应用而最佳化的,Turner因此称Cortex-R8是“专为5G性能打造的唯一即时处理器。” 不过,奇怪的是,高通显然并未在其新款Snapdragon X16数据机中采用ARM核心,反而改为部署自家的DSP来处理LTE-A Pro的工作负载。 ARM Cortex-R8和R7的最主要区别在于R8支援多达4颗超纯量乱序执行的核心。此外,ARM表示,R8还配备“高达每核心2MB紧密耦合记忆体”的更大容量。

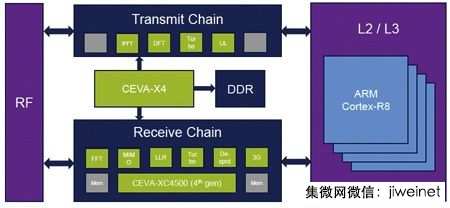

随着5G的资料传输速率大幅提升,Cortex-R8兼具低延迟、高效能与低功耗的优势,有助于打造支援LTE-A Pro和5G的数据机 针对数据机晶片的其他部份,Turner坦承“实体层是十分复杂的工程,包括类比转换、DSP进行调变与解调、Turbo编码、错误检查与加速加密,以及标头压缩等。” 那么ARM Cortex-R系列核心如何与其连接?Turner说,“的确,有些技术可以从专业的IP供应商授权取得,但他们通常还得进行修改或配置,才能用于一家公司专有的数据机架构。” 他补充说,“我们在这些设计中看到ARM Cortex-R系列处理器出现在软体接触实体层(Layer-1)硬体之处,并根据不同的标准,为管理与排程连接的所有软体提供Layer-2与Layer-3处理。” 此外,他表示,ARM的处理器还可执行Layer-1控制软体,配置与管理连接至Layer-1硬体(包括DSP与本地化控制逻辑)的介面。 是否重叠? 然而,CEVA看这一竞争格局的观点略有不同。Gresset指出,ARM的Cortex-R7或R8在这方面的应用,“缺少了DSP和系统控制。”他解释说,这使得ARM难以扩展Cortex-R在处理PHY控制器的角 {MOD}。 Gresset还补充说,“相较于CEVA-X4采用VLIW/SIMD核心,ARM的R7/R8由于采用超纯量乱序架构,使得晶片尺寸较大,每核心也消耗更多功耗。”。 因 此,Gresset 强调,CEVA虽然藉由增加更多硬体加速来捍卫其于Layer 1 PHY控制器的地盘,同时也希望创造一个可提升至Layer-2与Layer-3处理的开始,尽管这一向是ARM占主导的领域。他将强大的DSP处理(高 达16GOP)、高效的控制器性能以及先进的系统控制称为“CEVA-X新架构的三大支柱”。 另一方面,ARM则认为,Cortex-R8的关键优势在于其“在4个一致的核心与介面扩展数据机软体”的能力。其目标在于为密集的即时软体工作负载“实现平行化,以及满足LTE-A与LTE-A pro所需的性能与时机”。

全球主要的电信晶片供应商高通(Qualcomm)、DSP核心供应商CEVA以及处理器核心业者ARM,均竞相迎接这一挑战。三家公司均已开发出新的处理 器架构,并抢先在今年的世界行动通讯大会(MWC)之前发布。高通宣布Snapdragon X16、CEVA发表CEVA-X4,ARM则畅谈其新款Cortex-R8。

本文引用地址:http://www.eepw.com.cn/article/201604/289387.htm 高通新款数据机晶片在其Hexagon DSP核心中执行密集的LTE协定和语音编解码器(codec),同时还采用ARM Cortex执行Linux作业系统(OS)、IMS和IP堆叠。 挑战何在? 那么,这些新的基频数据机有何不同之处? 与 该技术有关的议题包括:增加载波聚合(CA)、将多重无线存取技术(Multi-RAT)整并于单一数据机、切换不同数据机时的低延迟作业、同步处理双基 地台以及伴随VoLTE高品质语音通话服务而来的复杂度等。根据CEVA,新的基频据机必须能够处理上述所有或更多的问题。 The Linley Group资深分析师Mike Demler呼吁为现有的数据机晶片架构进行“全面体检”,“才能满足LTE Advanced(LTE-A)与LTE-A Pro标准日益严格的性能和功耗限制。” 因此,存在于高通、CEVA和ARM三方之间的竞赛,开始转变成为针对处理器、硬体加速与DSP的全新战场。 供应商们正积极讨论在Layer 1实体(PHY)控制器、Layer 2和layer 3处理之间增加的LTE基频工作负载应该如何进行最佳化处理;以及应该采用先进的DSP核心、强化的处理器核心或是二者兼用的组合? 各据不同势力范围的每一家供应商显然有着不同的想法。 高通发表先进的LTE数据机Snapdragon X16,用于支援LTE-A Pro Category 16高达1 Gbps传输速率的下行链路以及实现Category 13高达150Mbps的上传速度。

高通最新Snapdragon X16支援高达1 Gbps的下载速度,号称是行动产业首款Gigabit级的LTE数据机 为了不让高通专美于前,CEVA和ARM也发布自家最新设计的核心——分别是CEVA-X4与ARM Cortex-R8,他们表示最新的架构已经准备好迎接LTE-A Pro数据机的挑战了。不过,目前还没有任何一款商用基频晶片采用任一家IP供应商的处理器核心。 因 应LTE-A Pro数据机晶片日益增加的处理需求,两家IP核心供应商显然采取了全然不同的发展重点。例如,CEVA以CEVA-X4更新其L1 PHY控制器。相反地,ARM则透过其最新设计的四核心Cortex-R8,专注于满足针对Layer 2与L3软体处理持续增加的需求。 Demler明确指出,Cortex-R8和CEVA-X4是两种完全不同的核心。CEVA-X4用于PHY层控制,而ARM Cortex-R则否。他强调,“X4和R8可能在一款数据机应用中共存,让X4处理实体层,而Cortex-R则处理更高层级的控制功能。”

CEVA-X4与ARM Cortex-R8可能共存于下一代数据机晶片中? 遭遇瓶颈 CEVA行销与企业发展副总裁Eran Briman指出,在详细研究最新先进基频数据机的需求后,“我们发现PHY控制器在下一代基频中的瓶颈。” 藉由为基频应用重新定义处理控制和资料平面的性能和能效,CEVA开发出全新的CEVA-X DSP架构。 CEVA-X4是来自CEVA-X架构的首款授权核心。虽然DSP一直是CEVA的强项,但Demler 认为,CEVA-X4更像是“一款具有DSP功能的控制器。” CEVA无线业务部业务开发总监Emmanuel Gresset解释,在CEVA-X4中增加的CEVA先进DSP功能结合了控制层处理,以及“协同处理器和硬体加速的支援。” 他认为CEVA-X4是一种“全新的处理器类型,它能在DSP与控制之间实现真正的平衡。” Gresset 还指出,CEVA-X4的CoreMark/MHz基准达到了4.0。CoreMark是专为嵌入式系统衡量CPU性能的基准。Gresset说,这对于 CEVA来说是非常重要的,因为CEVA-X4目前可说是“与ARM Cortex-R7/R8不相上下。”

新的CEVA-X4架构充份结合控制器与DSP处理器,瞄准手机、IoT装置以及下一代5G基频数据机等应用 捍卫L2/L3处理领域 ARM一直是智慧型手机市场中首屈一指的CPU核心供应商。 ARM先进技术行销总监Chris Turner解释,“ARM Cortex-R7目前部署于大量3G/4G智慧型手机数据机中,Cortex-R4和Cortex-R5也用于ARM合作夥伴的数据机产品中。” 藉着Cortex-R8的推出,ARM计划满足对于协议软体处理以及LTE-A Pro与第一代5G日益增加的需求。他并补充说,“我们期望看到新的基频设计提升到采用Cortex-R8。” 值得注意的是,Cortex-R是为硬即时应用而最佳化的,Turner因此称Cortex-R8是“专为5G性能打造的唯一即时处理器。” 不过,奇怪的是,高通显然并未在其新款Snapdragon X16数据机中采用ARM核心,反而改为部署自家的DSP来处理LTE-A Pro的工作负载。 ARM Cortex-R8和R7的最主要区别在于R8支援多达4颗超纯量乱序执行的核心。此外,ARM表示,R8还配备“高达每核心2MB紧密耦合记忆体”的更大容量。

随着5G的资料传输速率大幅提升,Cortex-R8兼具低延迟、高效能与低功耗的优势,有助于打造支援LTE-A Pro和5G的数据机 针对数据机晶片的其他部份,Turner坦承“实体层是十分复杂的工程,包括类比转换、DSP进行调变与解调、Turbo编码、错误检查与加速加密,以及标头压缩等。” 那么ARM Cortex-R系列核心如何与其连接?Turner说,“的确,有些技术可以从专业的IP供应商授权取得,但他们通常还得进行修改或配置,才能用于一家公司专有的数据机架构。” 他补充说,“我们在这些设计中看到ARM Cortex-R系列处理器出现在软体接触实体层(Layer-1)硬体之处,并根据不同的标准,为管理与排程连接的所有软体提供Layer-2与Layer-3处理。” 此外,他表示,ARM的处理器还可执行Layer-1控制软体,配置与管理连接至Layer-1硬体(包括DSP与本地化控制逻辑)的介面。 是否重叠? 然而,CEVA看这一竞争格局的观点略有不同。Gresset指出,ARM的Cortex-R7或R8在这方面的应用,“缺少了DSP和系统控制。”他解释说,这使得ARM难以扩展Cortex-R在处理PHY控制器的角 {MOD}。 Gresset还补充说,“相较于CEVA-X4采用VLIW/SIMD核心,ARM的R7/R8由于采用超纯量乱序架构,使得晶片尺寸较大,每核心也消耗更多功耗。”。 因 此,Gresset 强调,CEVA虽然藉由增加更多硬体加速来捍卫其于Layer 1 PHY控制器的地盘,同时也希望创造一个可提升至Layer-2与Layer-3处理的开始,尽管这一向是ARM占主导的领域。他将强大的DSP处理(高 达16GOP)、高效的控制器性能以及先进的系统控制称为“CEVA-X新架构的三大支柱”。 另一方面,ARM则认为,Cortex-R8的关键优势在于其“在4个一致的核心与介面扩展数据机软体”的能力。其目标在于为密集的即时软体工作负载“实现平行化,以及满足LTE-A与LTE-A pro所需的性能与时机”。