data/attach/1907/wgnshgh8valzzjyvghux0tremlz7wtcq.jpg

1.2 应用

略

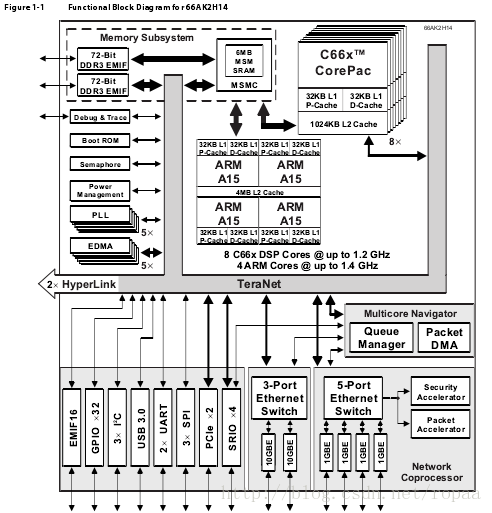

1.3 KeyStone 架构 TI 的 KeyStone 多核架构是一种运用专用协处理器及 I/O 整合了 RISC 和 DSP 核心的高性能结构。 KeyStone 给其所有处理器核心、外围设备、协处理器及I/O提供内部带宽合适的无阻塞通路,此为KeyStone首创。 这一点通过4个主要的硬件部件实现:多核导航器、一致性网络(TeraNet)、多核共享内存控制器以及超链接(HyperLink)。

多核导航器是一种革新的基于包交换的 16k 序列管理器。当任务被分配给队列时,多核导航器可提供硬件加速的调度,指引任务分配到正确的可用硬件。

基于包交换的片上系统,使用了2Tbps容量的TeraNet交换中心资源( switched central resource )来移动数据包。

多和共享内存控制器允许处理器核心直接访问内存,而不需要从TeraNet中占用容量。由于此,数据包的移动不会被内存访问所阻断。‘

超链接(HyperLink)提供了50G波特率的芯片级互连,使得各片上系统的串联工作成为可能。超链接的低协议开销和高吞吐量使它成为了理想的芯片-芯片互联接口。 当与多和导航器一同工作时,超链接将任务透明地分配给串联的设备,并且像在本地资源上运行一样地执行任务。

1.4 设备描述 66AK2Hx 平台使用 KeyStone II 架构整合了四核 ARM® Cortex™-A15 处理器与高达8核的 TMS320C66x 高性能DSP处理器。

66AK2H14 provides up to 5.6 GHz of ARM and 9.6 GHz of DSP ……(略,详见1.1)……

C66x 100% 向下兼容至 C64x+ 设备。它嵌入了90项新的指令,主要目标在浮点(FPi)和面向向量数学(VPi)处理上。

…………

1.5 KeyStone II 中的增强

1.6 功能块示意图![]()

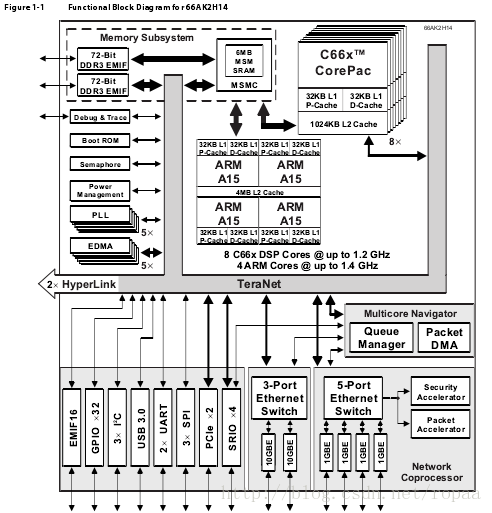

1.3 KeyStone 架构 TI 的 KeyStone 多核架构是一种运用专用协处理器及 I/O 整合了 RISC 和 DSP 核心的高性能结构。 KeyStone 给其所有处理器核心、外围设备、协处理器及I/O提供内部带宽合适的无阻塞通路,此为KeyStone首创。 这一点通过4个主要的硬件部件实现:多核导航器、一致性网络(TeraNet)、多核共享内存控制器以及超链接(HyperLink)。

多核导航器是一种革新的基于包交换的 16k 序列管理器。当任务被分配给队列时,多核导航器可提供硬件加速的调度,指引任务分配到正确的可用硬件。

基于包交换的片上系统,使用了2Tbps容量的TeraNet交换中心资源( switched central resource )来移动数据包。

多和共享内存控制器允许处理器核心直接访问内存,而不需要从TeraNet中占用容量。由于此,数据包的移动不会被内存访问所阻断。‘

超链接(HyperLink)提供了50G波特率的芯片级互连,使得各片上系统的串联工作成为可能。超链接的低协议开销和高吞吐量使它成为了理想的芯片-芯片互联接口。 当与多和导航器一同工作时,超链接将任务透明地分配给串联的设备,并且像在本地资源上运行一样地执行任务。

1.4 设备描述 66AK2Hx 平台使用 KeyStone II 架构整合了四核 ARM® Cortex™-A15 处理器与高达8核的 TMS320C66x 高性能DSP处理器。

66AK2H14 provides up to 5.6 GHz of ARM and 9.6 GHz of DSP ……(略,详见1.1)……

C66x 100% 向下兼容至 C64x+ 设备。它嵌入了90项新的指令,主要目标在浮点(FPi)和面向向量数学(VPi)处理上。

…………

1.5 KeyStone II 中的增强

1.6 功能块示意图