I2S接口概述

I2S全称Inter-IC Sound, Integrated Interchip Sound,或简写IIS,是飞利浦在1986年定义(1996年修订)的数字音频传输标准,用于数字音频数据在系统内部器件之间传输,例如编解码器CODEC、DSP、数字输入/输出接口、ADC、DAC和数字滤波器等。除了都是由飞利浦定义外,I2S和I2C没有任何关系。I2S硬件接口定义

- 串行时钟SCLK,也叫位时钟(BCLK),即对应数字音频的每一位数据,SCLK都有1个脉冲,SCLK的频率=2*采样频率*采样位数。

- 帧时钟LRCK,用于切换左右声道的数据,1为左声道,0为右声道,LRCK频率等于采样频率。

- 串行数据SD,就是用二进制补码表示的音频数据。

- 有时为了使系统能够更好地同步,还需要另外一个信号MCLK,称为主时钟,也叫系统时钟(sys clock),一般是采样频率的256倍或是384倍。切记,MCLK并不是必须的。可有可无,看设计要求。

电气连接

IIS是比较简单的数字接口协议,没有地址或设备选择机制。在IIS总线上,只能同时存在一个主设备和发送设备。

主设备可以是发送设备,也可以是接收设备,或是协调发送设备和接受设备的其它控制设备。

在IIS系统中,提供时钟的设备为主设备。

案例分析

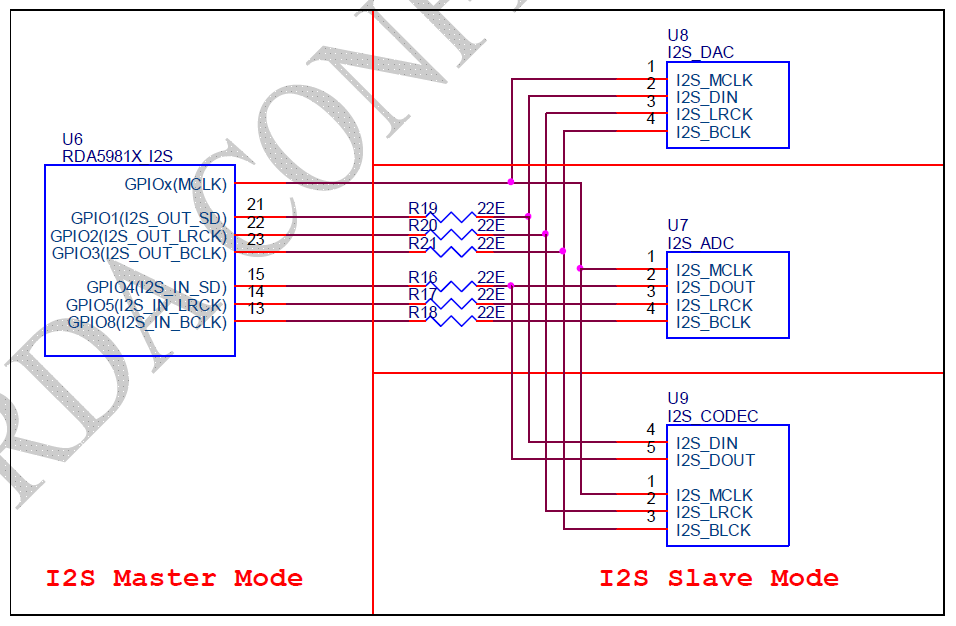

这是 RDA5981 的 IIS 接口,这个接口比较特殊:

SD 线分为 IN 和 OUT 两根,当它是输出音频数据时就使用 OUT_SD,当它是接受音频数据时就是用 IN_SD

LRCK 和 BCLK 也分为 IN 和 OUT 两组,当 RDA5981 当做主器件时就是用 OUT 组的时钟,当它用作从器件时就使用 IN 组的时钟。