玩了一段时间32了,遇到一些仿真问题,

关于JTAG与SWD

JTAG(Joint Test Action Group;联合测试工作组)是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。现在多数的高级器件都支持JTAG协议,如DSP、FPGA器件等。标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。 SWD协议 串行总线调试接口。需要3根线与目标MCU相连。SWDIO 为双向Data口,主机到目标的数据传送。SWDCLK 为时钟口,主机驱动。GND GND脚。 一般我们新手上路都用20角的j-link,方便又好使

一般我们都使用JTAG模式,但有时IO口不够用或者我们使用微小板子,只有SW下载口,这就要改模式了具体改如下图

这里可以改变模式,后面可以改传输频率,一般情况下不改,当下载情况不好时,降低频率

一一对应即可

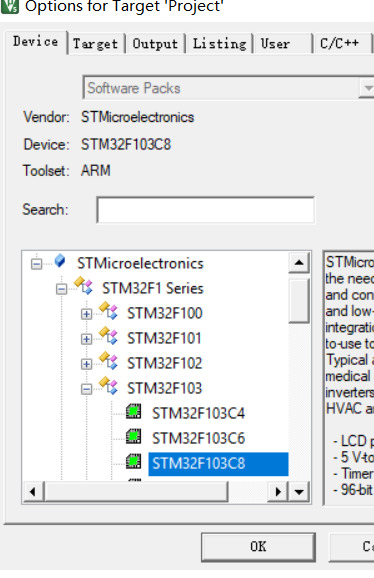

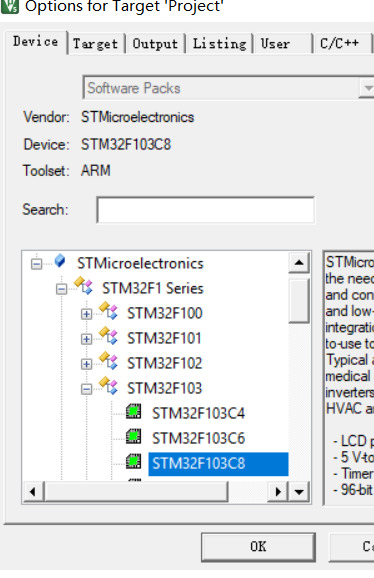

若程序不小心将下载的IO口占用,并且下载到芯片中,此时我们再下载就不好使了,解决方法就是按住复位键,当看到程序将要下载的时候松开复位,时机一定要抓好,下载一份其他代码就好,这个问题就解决了。 有时我们还会遇到下载FLASH的问题,一般都是芯片选型的问题和FLASH没加,如图改下就好

关于JTAG与SWD

JTAG(Joint Test Action Group;联合测试工作组)是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。现在多数的高级器件都支持JTAG协议,如DSP、FPGA器件等。标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。 SWD协议 串行总线调试接口。需要3根线与目标MCU相连。SWDIO 为双向Data口,主机到目标的数据传送。SWDCLK 为时钟口,主机驱动。GND GND脚。 一般我们新手上路都用20角的j-link,方便又好使

一般我们都使用JTAG模式,但有时IO口不够用或者我们使用微小板子,只有SW下载口,这就要改模式了具体改如下图

这里可以改变模式,后面可以改传输频率,一般情况下不改,当下载情况不好时,降低频率

一一对应即可

若程序不小心将下载的IO口占用,并且下载到芯片中,此时我们再下载就不好使了,解决方法就是按住复位键,当看到程序将要下载的时候松开复位,时机一定要抓好,下载一份其他代码就好,这个问题就解决了。 有时我们还会遇到下载FLASH的问题,一般都是芯片选型的问题和FLASH没加,如图改下就好