我的开发环境:quartus13.1

altlvds_tx/ altlvds_rx核实际上是个并串/串并转换器,在使用altlvds_tx/ altlvds_rx核时,一定要先在quartus ii中新建工程,编译并分配管脚,看编译能否通过,如果通过了再投板,否则可能要更改电路设计了。

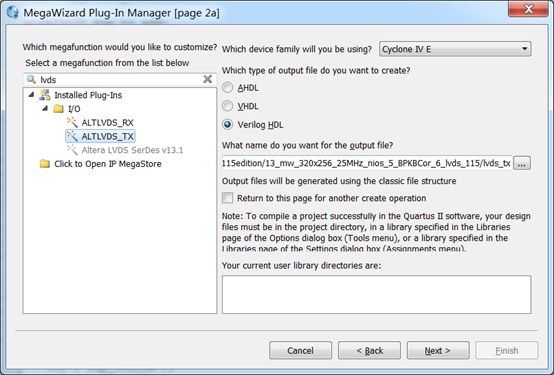

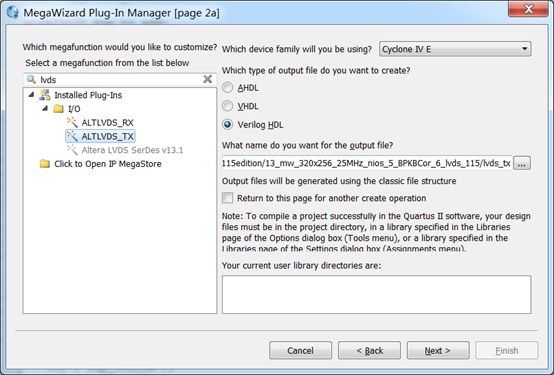

我在电路中使用lvds接口发送数据,以前的设计中使用的是DS90CR287完成数据串化,对于base模式,有4对数据和1对时钟,共5对lvds信号。使用FPGA的true lvds transmitters发送数据,需使用altera IP,在quartus中添加altlvds_tx核。

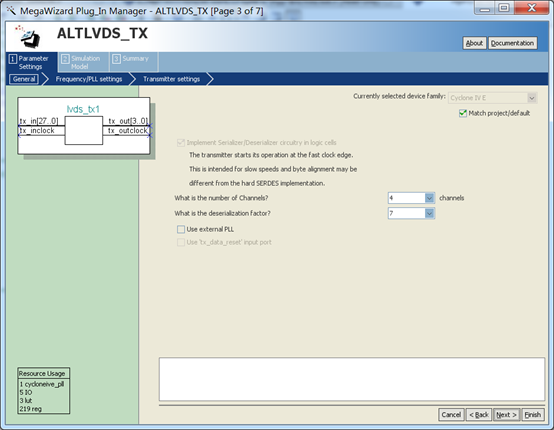

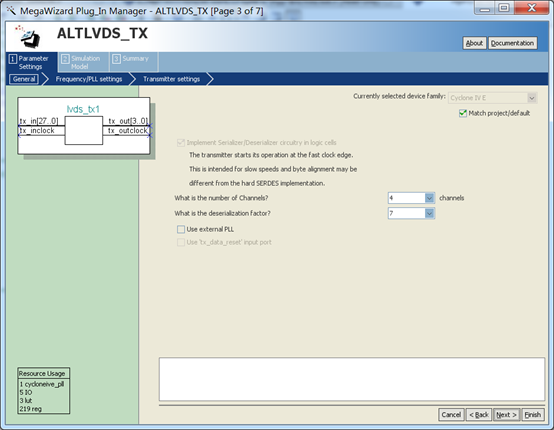

这里选择LVDS transmitter,然后设置4个LVDS通道(channels);每个通道对应7个解串因子,即7并1串处理。最下面的Use External PLL如果勾选上,则这个IP核内的其他两个配置页面不可设置,用户的时序频率方面的配置主要在外部的PLL时钟上下文章了;若不勾选上,则会使用一个PLL,如果资源够用的话,可以不用勾选,我们接着来看后面两个配置页面。

这里选择LVDS transmitter,然后设置4个LVDS通道(channels);每个通道对应7个解串因子,即7并1串处理。最下面的Use External PLL如果勾选上,则这个IP核内的其他两个配置页面不可设置,用户的时序频率方面的配置主要在外部的PLL时钟上下文章了;若不勾选上,则会使用一个PLL,如果资源够用的话,可以不用勾选,我们接着来看后面两个配置页面。

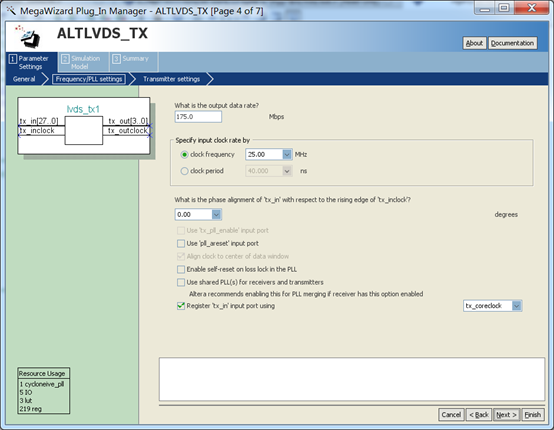

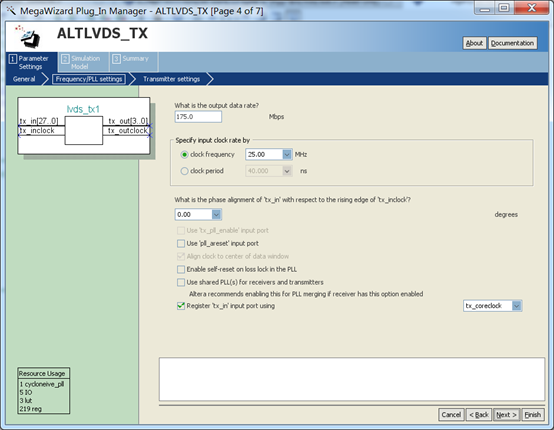

在Frequency/PLL settings中,需要配置好LVDS串行数据传输速率,在我的设计中,并行数据时钟频率为25MHz,对应串行数据频率为25*7=245Mbps,。其他几个选项一般使用默认设置,大家可以参考altlvds_tx Megafunction User Guide中有详细说明。

在Frequency/PLL settings中,需要配置好LVDS串行数据传输速率,在我的设计中,并行数据时钟频率为25MHz,对应串行数据频率为25*7=245Mbps,。其他几个选项一般使用默认设置,大家可以参考altlvds_tx Megafunction User Guide中有详细说明。

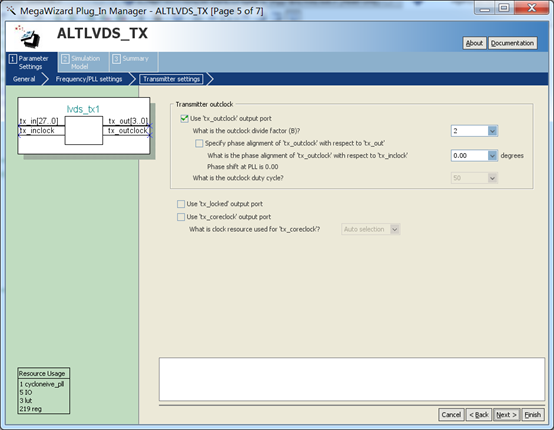

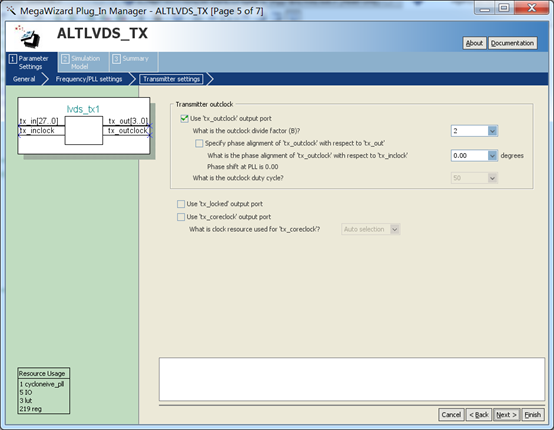

Transmitter settings中有多个Transmitter outclock配置选项,主要是LVDS输出时钟与输出差分信号的时钟以及相位设置,具体如何配置还是需要根据用户本身这个LVDS信号的传输需求而定。

Transmitter settings中有多个Transmitter outclock配置选项,主要是LVDS输出时钟与输出差分信号的时钟以及相位设置,具体如何配置还是需要根据用户本身这个LVDS信号的传输需求而定。

reg [6:0] datain3;

reg [6:0] datain2;

reg [6:0] datain1;

reg [6:0] datain0;

lvds_tx1 lvds_tx1_inst (

.tx_in ( {datain3 , datain2 , datain1 , datain0} ),

.tx_inclock ( clk ),

.tx_out ( cameralinkData ),

.tx_outclock ( cameralinkClk )

);

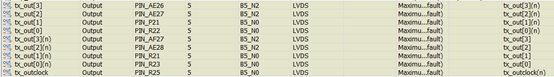

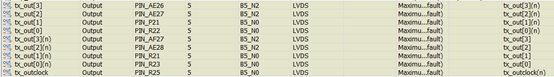

最后,在管脚分配时,需要选择I/O Standard为LVDS,然后会自动参数另一个*(n)的配对差分管脚

reg [6:0] datain3;

reg [6:0] datain2;

reg [6:0] datain1;

reg [6:0] datain0;

lvds_tx1 lvds_tx1_inst (

.tx_in ( {datain3 , datain2 , datain1 , datain0} ),

.tx_inclock ( clk ),

.tx_out ( cameralinkData ),

.tx_outclock ( cameralinkClk )

);

最后,在管脚分配时,需要选择I/O Standard为LVDS,然后会自动参数另一个*(n)的配对差分管脚

编译,如果编译通过,则说明设计ok。

另外,板子画完了,等待投完板回来调试,调试后再补充实验结果。

参考文章

编译,如果编译通过,则说明设计ok。

另外,板子画完了,等待投完板回来调试,调试后再补充实验结果。

参考文章

这里选择LVDS transmitter,然后设置4个LVDS通道(channels);每个通道对应7个解串因子,即7并1串处理。最下面的Use External PLL如果勾选上,则这个IP核内的其他两个配置页面不可设置,用户的时序频率方面的配置主要在外部的PLL时钟上下文章了;若不勾选上,则会使用一个PLL,如果资源够用的话,可以不用勾选,我们接着来看后面两个配置页面。

这里选择LVDS transmitter,然后设置4个LVDS通道(channels);每个通道对应7个解串因子,即7并1串处理。最下面的Use External PLL如果勾选上,则这个IP核内的其他两个配置页面不可设置,用户的时序频率方面的配置主要在外部的PLL时钟上下文章了;若不勾选上,则会使用一个PLL,如果资源够用的话,可以不用勾选,我们接着来看后面两个配置页面。

在Frequency/PLL settings中,需要配置好LVDS串行数据传输速率,在我的设计中,并行数据时钟频率为25MHz,对应串行数据频率为25*7=245Mbps,。其他几个选项一般使用默认设置,大家可以参考altlvds_tx Megafunction User Guide中有详细说明。

在Frequency/PLL settings中,需要配置好LVDS串行数据传输速率,在我的设计中,并行数据时钟频率为25MHz,对应串行数据频率为25*7=245Mbps,。其他几个选项一般使用默认设置,大家可以参考altlvds_tx Megafunction User Guide中有详细说明。

Transmitter settings中有多个Transmitter outclock配置选项,主要是LVDS输出时钟与输出差分信号的时钟以及相位设置,具体如何配置还是需要根据用户本身这个LVDS信号的传输需求而定。

Transmitter settings中有多个Transmitter outclock配置选项,主要是LVDS输出时钟与输出差分信号的时钟以及相位设置,具体如何配置还是需要根据用户本身这个LVDS信号的传输需求而定。

reg [6:0] datain3;

reg [6:0] datain2;

reg [6:0] datain1;

reg [6:0] datain0;

lvds_tx1 lvds_tx1_inst (

.tx_in ( {datain3 , datain2 , datain1 , datain0} ),

.tx_inclock ( clk ),

.tx_out ( cameralinkData ),

.tx_outclock ( cameralinkClk )

);

最后,在管脚分配时,需要选择I/O Standard为LVDS,然后会自动参数另一个*(n)的配对差分管脚

reg [6:0] datain3;

reg [6:0] datain2;

reg [6:0] datain1;

reg [6:0] datain0;

lvds_tx1 lvds_tx1_inst (

.tx_in ( {datain3 , datain2 , datain1 , datain0} ),

.tx_inclock ( clk ),

.tx_out ( cameralinkData ),

.tx_outclock ( cameralinkClk )

);

最后,在管脚分配时,需要选择I/O Standard为LVDS,然后会自动参数另一个*(n)的配对差分管脚

编译,如果编译通过,则说明设计ok。

另外,板子画完了,等待投完板回来调试,调试后再补充实验结果。

参考文章

编译,如果编译通过,则说明设计ok。

另外,板子画完了,等待投完板回来调试,调试后再补充实验结果。

参考文章

- LVDS SERDES Transmitter/Receiver IP Cores User Guide