在看这篇文章之前, 建议先好好读下这篇文章。http://download.csdn.net/detail/angelbosj/8013827。

由于我不太会用 VISio,要是哪位网友能告诉我,怎么能画出上面文档那么好的时序图来,请留言告诉我。拜谢~

对于视频接口好多都是这样的, 比如 bt1120, 16根数据线和 1根clock. 并行.

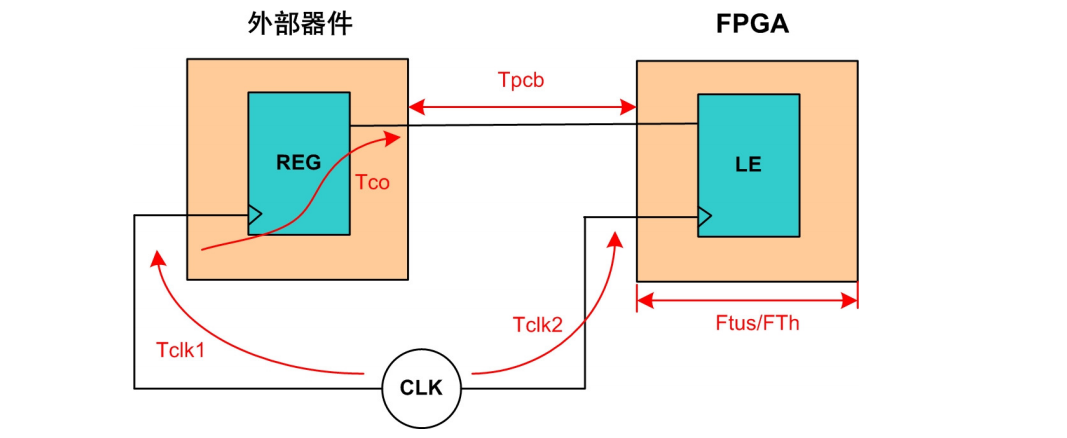

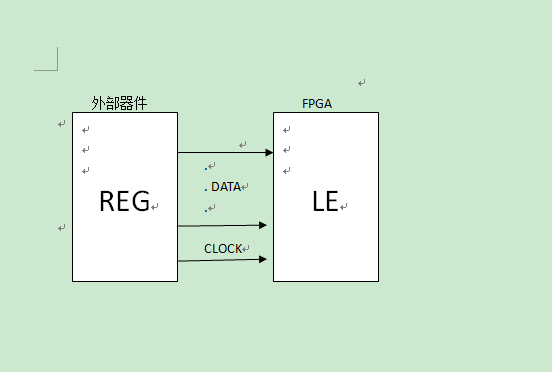

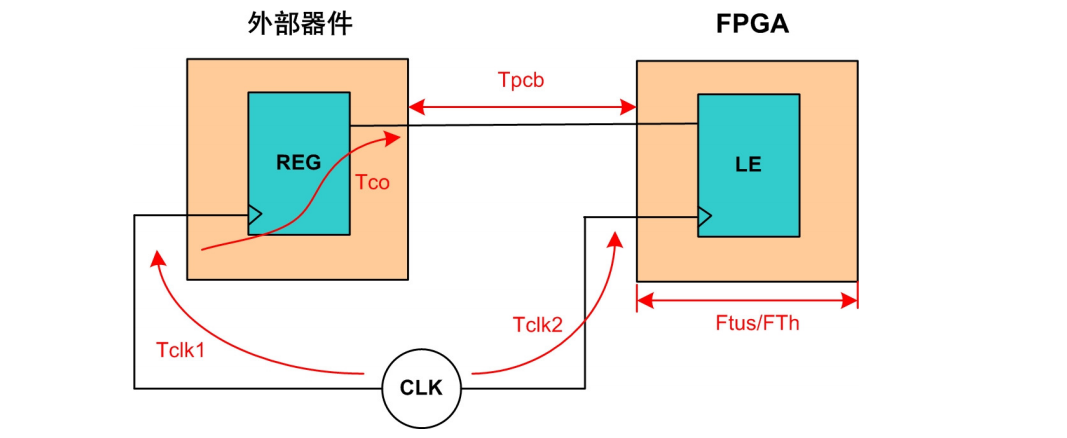

a、FPGA 输入时钟模型.

a、FPGA 输入时钟模型.

我们可以要求layout的时候, clk 和 数据线之间等长, 这样分析起来会容易。

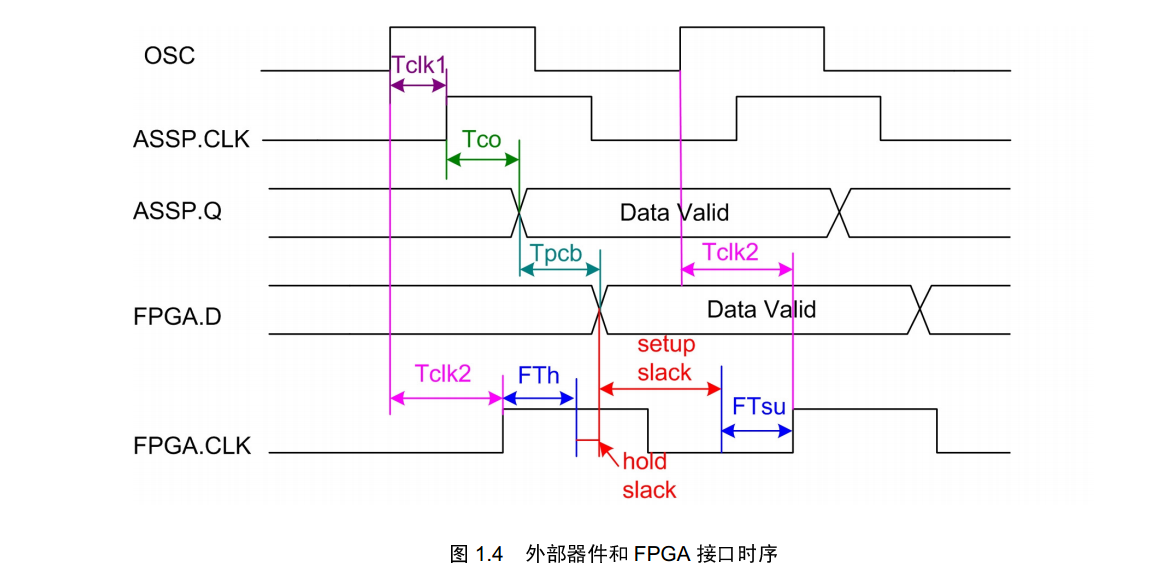

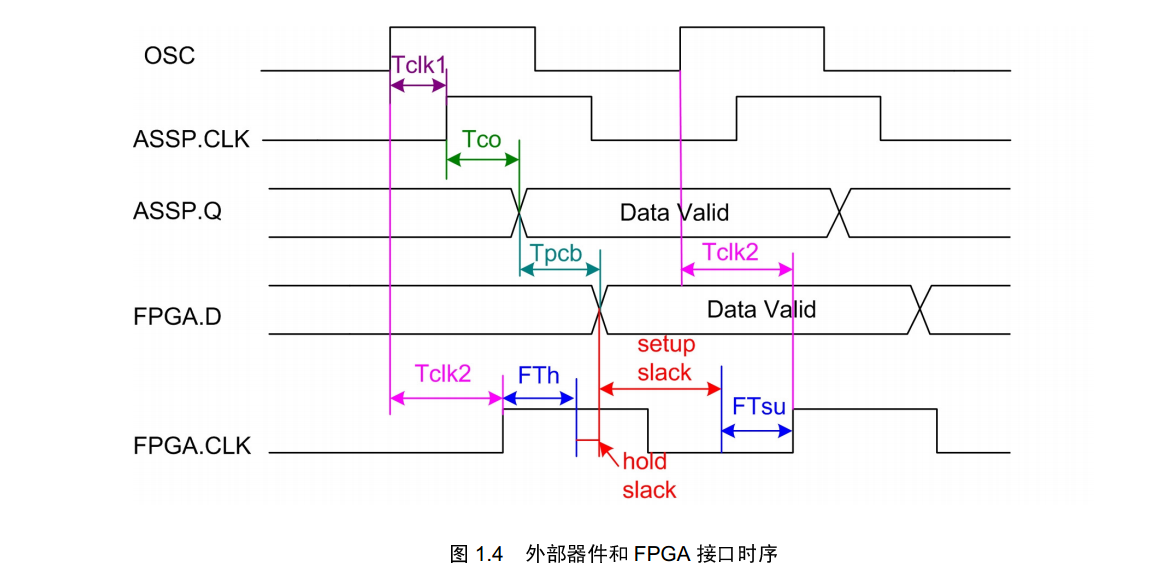

如果外部芯片是上升沿发送数据, FPGA上升沿接受数据.

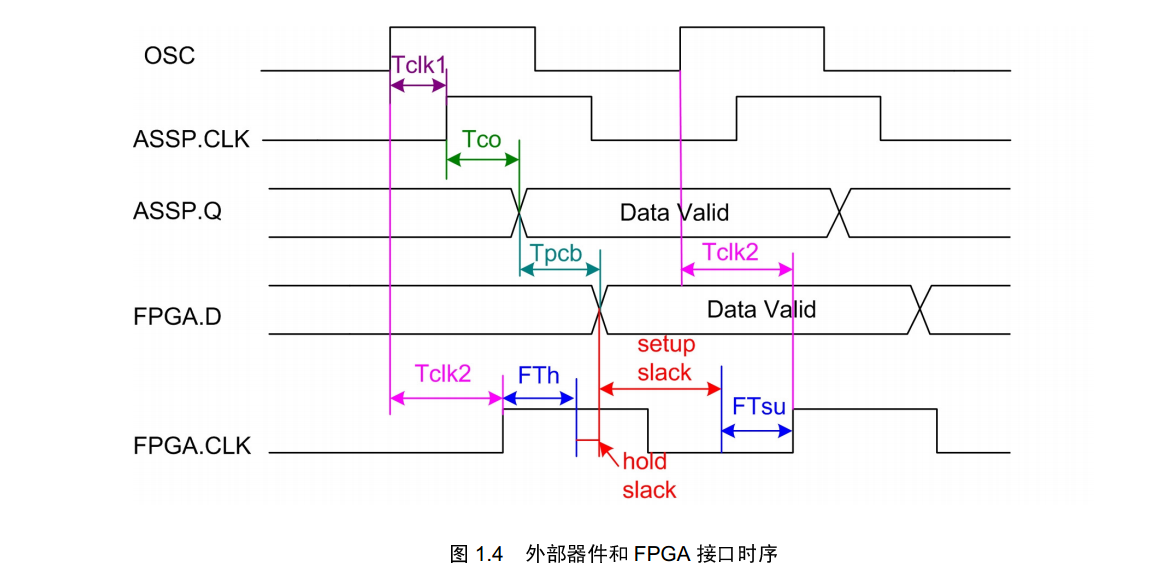

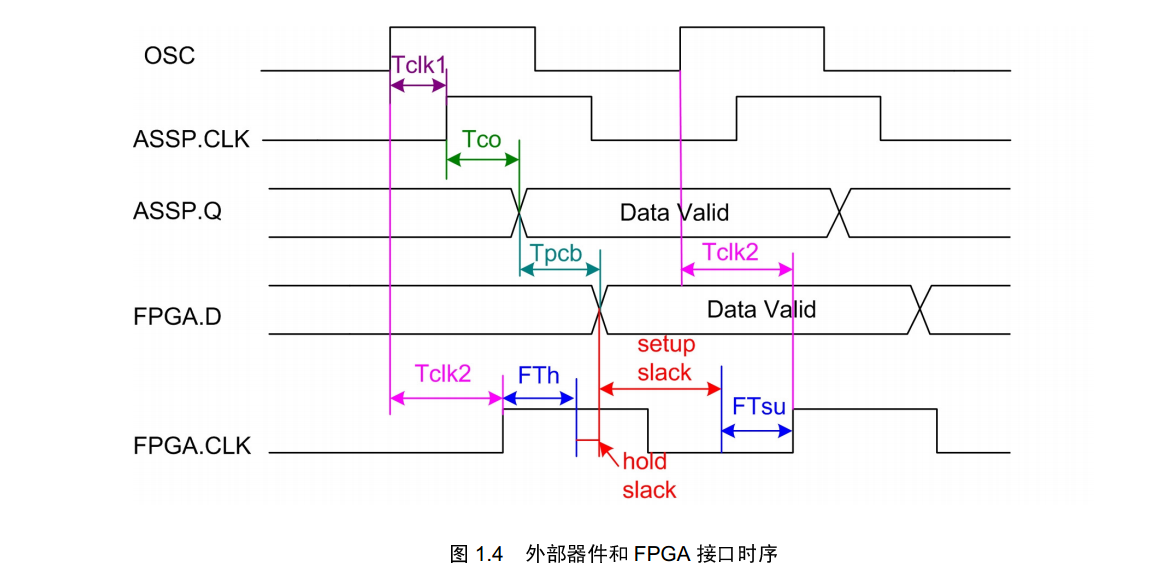

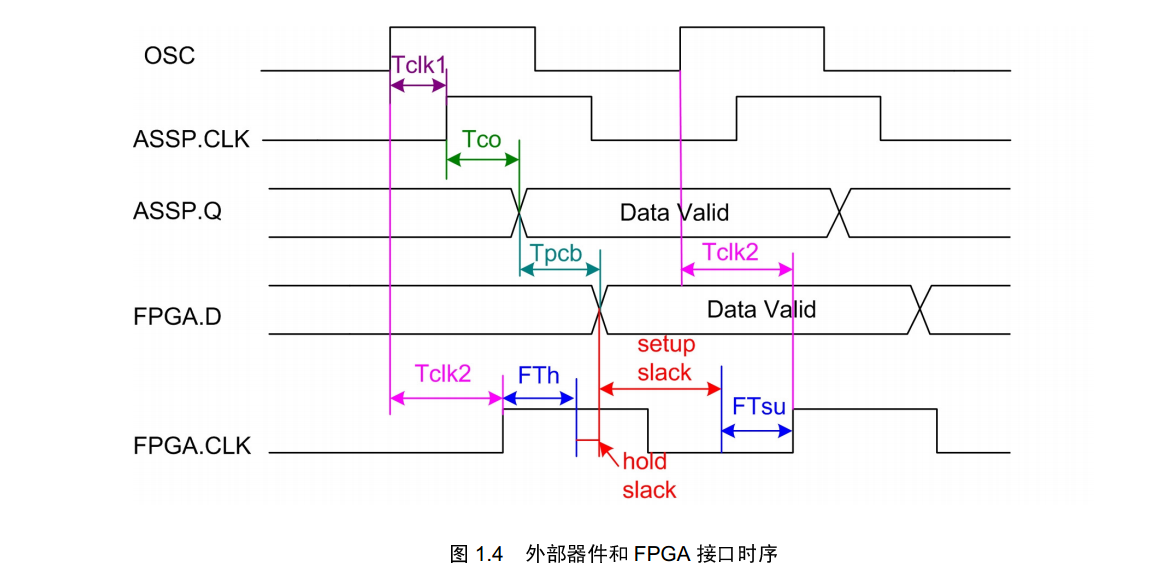

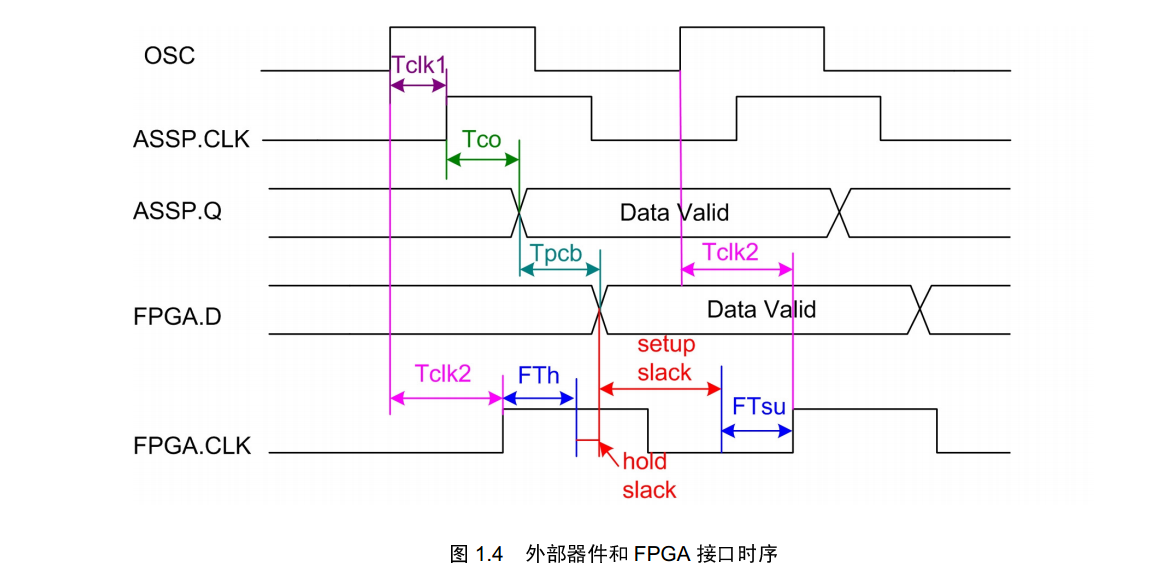

请看下面这图:

我们可以要求layout的时候, clk 和 数据线之间等长, 这样分析起来会容易。

如果外部芯片是上升沿发送数据, FPGA上升沿接受数据.

请看下面这图:

建立时间满足的情况:

Setup Slack = (Tclk + Tclk2 ) - (Tclk1 + Tpcb + Tco + FTsu) >0.

因为 Tclk2 = Tpcb, Tclk1 = 0. 所以, Tclk - (Tco + FTsu) > 0 . 由此可知,建立时间肯定能满足.

保持时间满足的情况:

Hold Slack = (Tclk1 + Tco + Tpcb) - (Tclk2 + FTh) >0 .

因为 Tclk2 = Tpcb, Tclk1 = 0. 所以 Tco - FTh > 0. 这样显然可能不合适.

建立时间满足的情况:

Setup Slack = (Tclk + Tclk2 ) - (Tclk1 + Tpcb + Tco + FTsu) >0.

因为 Tclk2 = Tpcb, Tclk1 = 0. 所以, Tclk - (Tco + FTsu) > 0 . 由此可知,建立时间肯定能满足.

保持时间满足的情况:

Hold Slack = (Tclk1 + Tco + Tpcb) - (Tclk2 + FTh) >0 .

因为 Tclk2 = Tpcb, Tclk1 = 0. 所以 Tco - FTh > 0. 这样显然可能不合适.

外部芯片是下降沿发送数据, FPGA上升沿接受数据, 请看下面这图:

建立时间满足的情况:![]() Setup Slack = (Tclk + Tclk2 ) - (Tclk1 + Tpcb + Tco + FTsu) >0.

Setup Slack = (Tclk + Tclk2 ) - (Tclk1 + Tpcb + Tco + FTsu) >0.![]()

![]() 因为是下降沿发送数据, 则Tclk1 = Tclk/2. Tclk2 = Tpcb,所以, Tclk - (Tclk/2 + Tco + FTsu) > 0 . 可以满足情况.

保持时间满足的情况:

Hold Slack = (Tclk1 + Tco + Tpcb) - (Tclk2 + FTh) >0 .

因为 Tclk2 = Tpcb, Tclk1 = Tclk/2.. 所以 Tco + Tclk/2 - FTh > 0. 可以满足情况.

因为是下降沿发送数据, 则Tclk1 = Tclk/2. Tclk2 = Tpcb,所以, Tclk - (Tclk/2 + Tco + FTsu) > 0 . 可以满足情况.

保持时间满足的情况:

Hold Slack = (Tclk1 + Tco + Tpcb) - (Tclk2 + FTh) >0 .

因为 Tclk2 = Tpcb, Tclk1 = Tclk/2.. 所以 Tco + Tclk/2 - FTh > 0. 可以满足情况.

外部芯片是上升沿发送数据, FPGA下降沿接受数据, 请看下图;

建立时间满足的情况: Setup Slack = (Tclk + Tclk2 ) - (Tclk1 + Tpcb + Tco + FTsu) >0. 因为是下降沿接受数据, 则Tclk1 = 0. Tclk2 = Tpcb - Tclk/2. 此时. Setup Slack = Tclk/2 - (Tco + FTsu ) > 0 可以满足条件.

保持时间满足的情况:

Hold Slack = (Tclk1 + Tco + Tpcb) - (Tclk2 + FTh) >0 . 因为是下降沿接受数据, 则Tclk1 = 0. Tclk2 = Tpcb - Tclk/2. 此时,Tco + Tclk/2 - FTh > 0 可以满足条件.

b、FPGA 输出时钟模型. FPGA 输出时钟模型.和 FPGA输入模型情况类似.

总结: 对于FPGA 输入时钟模型, 有两个建议: 一、 数据 和 时钟线 等长. 二、 外部芯片下降沿发送数据,FPGA上升沿接受数据. 对于FPGA 输出时钟模型, 有两个建议: 一、 数据 和 时钟线 等长. 二、 FPGA上升沿发送数据,外部芯片 下降沿接受数据.

只有这样再去进行FPGA端口的约束才有意义. 补充: PCB延时经验值为 600mil/ns, 1mm = 39.37mil. 内部时序不满足的时候, 尽量减少 组合逻辑.

a、FPGA 输入时钟模型.

a、FPGA 输入时钟模型.

我们可以要求layout的时候, clk 和 数据线之间等长, 这样分析起来会容易。

如果外部芯片是上升沿发送数据, FPGA上升沿接受数据.

请看下面这图:

我们可以要求layout的时候, clk 和 数据线之间等长, 这样分析起来会容易。

如果外部芯片是上升沿发送数据, FPGA上升沿接受数据.

请看下面这图:

建立时间满足的情况:

Setup Slack = (Tclk + Tclk2 ) - (Tclk1 + Tpcb + Tco + FTsu) >0.

因为 Tclk2 = Tpcb, Tclk1 = 0. 所以, Tclk - (Tco + FTsu) > 0 . 由此可知,建立时间肯定能满足.

保持时间满足的情况:

Hold Slack = (Tclk1 + Tco + Tpcb) - (Tclk2 + FTh) >0 .

因为 Tclk2 = Tpcb, Tclk1 = 0. 所以 Tco - FTh > 0. 这样显然可能不合适.

建立时间满足的情况:

Setup Slack = (Tclk + Tclk2 ) - (Tclk1 + Tpcb + Tco + FTsu) >0.

因为 Tclk2 = Tpcb, Tclk1 = 0. 所以, Tclk - (Tco + FTsu) > 0 . 由此可知,建立时间肯定能满足.

保持时间满足的情况:

Hold Slack = (Tclk1 + Tco + Tpcb) - (Tclk2 + FTh) >0 .

因为 Tclk2 = Tpcb, Tclk1 = 0. 所以 Tco - FTh > 0. 这样显然可能不合适.

外部芯片是下降沿发送数据, FPGA上升沿接受数据, 请看下面这图:

建立时间满足的情况:

外部芯片是上升沿发送数据, FPGA下降沿接受数据, 请看下图;

建立时间满足的情况: Setup Slack = (Tclk + Tclk2 ) - (Tclk1 + Tpcb + Tco + FTsu) >0. 因为是下降沿接受数据, 则Tclk1 = 0. Tclk2 = Tpcb - Tclk/2. 此时. Setup Slack = Tclk/2 - (Tco + FTsu ) > 0 可以满足条件.

保持时间满足的情况:

Hold Slack = (Tclk1 + Tco + Tpcb) - (Tclk2 + FTh) >0 . 因为是下降沿接受数据, 则Tclk1 = 0. Tclk2 = Tpcb - Tclk/2. 此时,Tco + Tclk/2 - FTh > 0 可以满足条件.

b、FPGA 输出时钟模型. FPGA 输出时钟模型.和 FPGA输入模型情况类似.

总结: 对于FPGA 输入时钟模型, 有两个建议: 一、 数据 和 时钟线 等长. 二、 外部芯片下降沿发送数据,FPGA上升沿接受数据. 对于FPGA 输出时钟模型, 有两个建议: 一、 数据 和 时钟线 等长. 二、 FPGA上升沿发送数据,外部芯片 下降沿接受数据.

只有这样再去进行FPGA端口的约束才有意义. 补充: PCB延时经验值为 600mil/ns, 1mm = 39.37mil. 内部时序不满足的时候, 尽量减少 组合逻辑.