class="markdown_views prism-atom-one-light">

优缺点分析二进制数据串行传送的优点是所需要的数据线最少,即只需要一条线路。而在并行传送中,线路的数量等于一次传送的位的数量。串行传送的缺点是相对于并行传送,它需要更长的时间来完成一个给定位数的传送。例如,如果1 微秒可以传送一位,那么需8 微秒来完成串行传送8个位,但并行传送8个位只需1 微秒,并行传送的缺点是和串行相比,需要更多的线路。

集成电路封装以他们安装在印刷电路板(PCB)(Printed circuit board)上的方法分类:

adc——dsp——cdaf

paratic golical正逻辑

当然同时也有负逻辑这个东西

在数字信号传输过程中是有电压波动的,但是因为high/low的划定是有其一贯额范围的,所以有相当的容错性。如果实在low到high之间,就会成为invalid,即不存在

digital waveforms:数字波形,

0——1——0:正脉冲;

1——0——1:负脉冲

rising edge和falling edge都是一个时间点

正脉冲占总周期的比率叫做duty cycle

cpu的clock

时序图:timing diagrams

0100

0011这种如何区分两个1呢?

所以要有一个clock,一个clock周期一个数据

有些孩纸啊上升沿河下降沿的地方传输数据

在上面时候读数据最稳定?所以一般在clock的下降沿读数据比较准确

data can be transmitted by either serial transfer(ex.usb)or parallel transfer

数据串行传输或者并行传输

串行不一定有时钟

慢切斯特编码

也可以双方约定好一个bit的长度

串口的数据传输方式就是约定好传输的bit常数和bit开始的时间点

但是并行一定有clock

Chapter1 Introductory Concepts

数字量(DIgital Quantities)和模拟量(Analog Quantities)

模拟量具有连续的数值,数字量具有离散的数值- 数字量的优点:

- 数字数据和模拟数据相比,前者在处理和传输方面更加有效,更加可靠

- 数字数据在需要保存时更加优越。如,转换成数字形式的英语额,要比相对应的模拟形式音乐更加简洁,复制是更加精确、更清晰。噪声对模拟信号的影响是远大于数字信号的。

• digital data can be processed and transmitted more efficiently and reliably than analog data.

• digital form can be stored more compactly and reproduced with greater accuracy and clarity than is possible when it is in analog form.

• Noise (unwanted voltage fluctuations) does not affect digital data nearly as much as it does analog signals

- 模拟电子系统(An Analog System)

- 使用数字方法和模拟方法的系统。(A System Using Digital and Analog Methods)

其中,ADC:数模转换器;DSP:数字信号处理;CDA:模数转换

二进制数、逻辑电平和数字波形(Binary Digits、Logic Levels、and Digital Waveforms)

- 正逻辑(positive logic)高电压用1来表示,低电压用0来表示,这就是正逻辑。一般情况下都是这样子的。

- 负逻辑(negative logic)就是上面反过来

- 逻辑电平(Logic Level)

- 在数字信号的传输过程中是存在一定电压波动的,但是因为HIGH与LOW的划定是有一定范围的,所以有相当的容错性。如果是在low到high之间,就会成为invalid,即不存在。如在CMOS数字电路中,高电平旨在2~3.3V,低电平值在0

~0.8V,而0.8 ~0.2V理论上是不可以出现的

- 数字波形(Digital Waveforms)

先介绍一下数字波形中的一些概念:

The Pulse:leading edge (also called rising edge ):occurs first at time t0

falling edge (also called tralling edge):occurs last at time t1

The picture above shows us a ideal pulses because the rising and falling edges are assumed to change in zero time (instantaneously)

The picture below shows us a nonideal pulse .(always resulted by RC circuit )

rise time(tr)

fall time(tf)

amplitude

**pulse width **:is a measure of the duration of the pulse and is often defined as the tiem intercal between the 50%points on the rising and falling edges ,as indicated in Figure below

- Waveform Characteristics(波形特性)

- period:周期

- frequency:频率

- duty cycle:占空比

- 数字波形携带二进制信息(A Digital Waveform Carries Binary Information)

- 时钟(clock):在数字系统中,所有的波形都与一个基本时序波形同步,称之为时钟。每个脉冲之间的间隔(周期)等于一个位时间(the period or called the Bit time)。

- 时序图(Timing Diagram)

时序图就是数字波形的图形,他表示两个或两个以上波形的实际时间关系,还表示波形和波形之间的相互变化关系。

数据传送

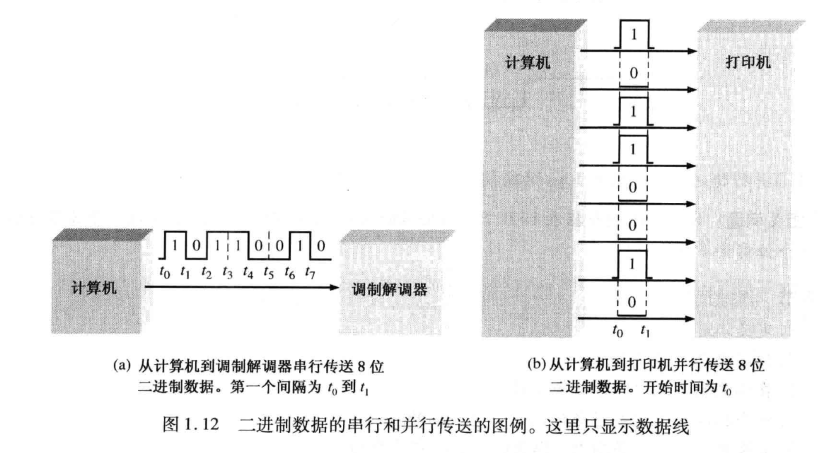

数据(data)是指一组可以用来传递某种信息的位(bits)使用数字波形表示的二进制数据,必须在数字系统中从一个电路传送到另一个电路,或者从一个系统传送到另一个系统,以实现某个设定的目的。例如,计算机存储器中的数字是以二进制的形式存储的,它必须传送到计算机的中央处理器才能实现加法运算 。然后加法运算的结果必须传送到显示器显示并且/或者回送到存储器中。如图所示,二进制数据的传送方式有两种——串行(Serial transfer)和并行(Parallel transfer)。

优缺点分析二进制数据串行传送的优点是所需要的数据线最少,即只需要一条线路。而在并行传送中,线路的数量等于一次传送的位的数量。串行传送的缺点是相对于并行传送,它需要更长的时间来完成一个给定位数的传送。例如,如果1 微秒可以传送一位,那么需8 微秒来完成串行传送8个位,但并行传送8个位只需1 微秒,并行传送的缺点是和串行相比,需要更多的线路。

例题:

(a) Determine the total time required to serially transfer the eight bits contained in waveform A of Figure 1–14, and indicate the sequence of bits. The left-most bit is the first to be transferred. The 1 MHz clock is used as reference. (b) What is the total time to transfer the same eight bits in parallel?

解:时钟频率是1MHz,所以周期就可以得到:

即传送以为需要一微秒,则传输8个位需要8微秒

而并行传送8各位需要1微秒的时间

基本逻辑功能(Basic Logic Functions)

组合和顺序逻辑功能(Combinational and Sequential Logic Functions)

- 比较函数(The comparison function)

2.计算函数(The Arithmetic Function)

- 加(Addition)

加法是由加法器(adder)实现的。比如:

其中,carry input是进位输入,carry output是进位输出 - 减(Subtraction)

减法由减法器实现(subtracter) - 乘法(Multiplication)

由乘法器实现(multiplier)因为乘法仅仅是部分乘积位置的移位的一系列加法,它可以通过与其他电路结合使用加法器来实现。 - 除法(Division)

除法可以通过一系列的减法、比较和移位来完成,因此它也可以与其他电路一起使用加法器来完成。除法器需要两个输入,生成的输出是商和余数。

- 编码(The Encoding Function)

encode:编码

编码功能是由一个称为编码器的逻辑电路执行的,在第6章中已经介绍过。编码器将信息(如十进制数或字母字符)转换成某种编码形式。例如,一种特定类型的编码器将每个十进制数字(0到9)转换为二进制代码。与特定十进制数对应的输入上的高电平产生逻辑电平,这些逻辑电平表示输出行上正确的二进制代码。图1-22是一个简单的编码器,用于将(编码)计算器按键转换成二进制代码,该二进制代码可由计算器电路处理。

- 解码(The Decoding Function)

- 数据选择(The Data Selection Function)

- 计数(Counting Function)

- 储存

固定功能的集成电路(integrated circuit)

单片继承电路(IC)是一个完全由单个小型的硅芯片组成的电子电路。组成电路的所有原件——晶体管、二极管、电阻和电容是单个芯片的一部分。集成电路封装以他们安装在印刷电路板(PCB)(Printed circuit board)上的方法分类:

- 对穿孔封装()

adc——dsp——cdaf

paratic golical正逻辑

当然同时也有负逻辑这个东西

在数字信号传输过程中是有电压波动的,但是因为high/low的划定是有其一贯额范围的,所以有相当的容错性。如果实在low到high之间,就会成为invalid,即不存在

digital waveforms:数字波形,

0——1——0:正脉冲;

1——0——1:负脉冲

rising edge和falling edge都是一个时间点

正脉冲占总周期的比率叫做duty cycle

cpu的clock

时序图:timing diagrams

0100

0011这种如何区分两个1呢?

所以要有一个clock,一个clock周期一个数据

有些孩纸啊上升沿河下降沿的地方传输数据

在上面时候读数据最稳定?所以一般在clock的下降沿读数据比较准确

data can be transmitted by either serial transfer(ex.usb)or parallel transfer

数据串行传输或者并行传输

串行不一定有时钟

慢切斯特编码

也可以双方约定好一个bit的长度

串口的数据传输方式就是约定好传输的bit常数和bit开始的时间点

但是并行一定有clock