TMS320F28335项目开发记录9_28335之中断系统

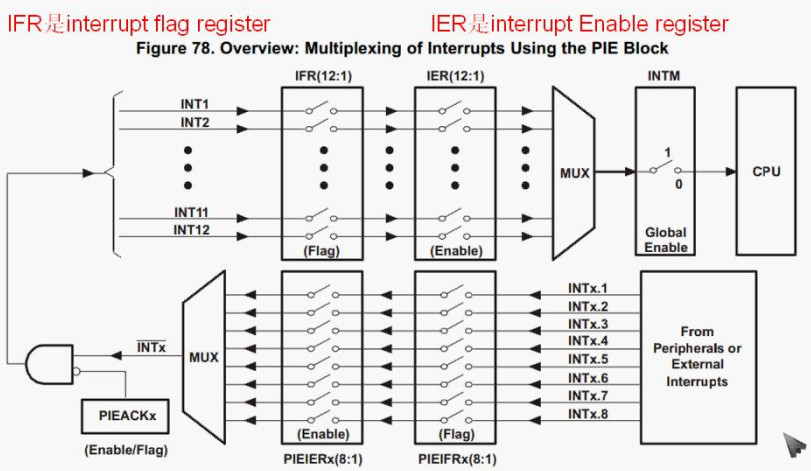

2014年11月08日 12:00:12 阅读数:3104 28335中断系统 1.中断系统 在这里我们要十分清楚DSP的中断系统。C28XX一共有16个中断源,其中有2个不可屏蔽的中断RESET和NMI、定时器1和定时器2分别使用中断13和14。这样还有12个中断都直接连接到外设中断扩展模块PIE上。说的简单一点就是PIE通过12根线与28335核的12个中断线相连。而PIE的另外一侧有12*8根线分别连接到外设,如AD、SPI、EXINT等等。 PIE共管理12*8=96个外部中断。这12组大中断由28335核的中断寄存器IER来控制,即IER确定每个中断到底属于哪一组大中断(如IER |= M_INT12; 说明我们要用第12组的中断,但是第12组里面的什么中断CPU并不知道需要再由PIEIER确定 )。 接下来再由PIE模块中的寄存器PIEIER中的低8确定该中断是这一组的第几个中断,这些配置都要告诉CPU(我们不难想象到PIEIER共有12总即从PIEIER1-PIEIER12)。另外,PIE模块还有中断标志寄存器PIEIFR,同样它的低8位是来自外部中断的8个标志位,同样CPU的IFR寄存器是中断组的标志寄存器。由此看来,CPU的所有中断寄存器控制12组的中断,PIE的所有中断寄存器控制每组内8个的中断。除此之外,我们用到哪一个外部中断,相应的还有外部中断的寄存器,需要注意的就是外部中断的标志要自己通过软件来清零。而PIE和CPU的中断标志寄存器由硬件来清零。

-

EALLOW; // This is needed to write to EALLOW protected registers -

PieVectTable.XINT2 = &ISRExint; //告诉中断入口地址 -

EDIS; // This is needed to disable write to EALLOW protected registers -

PieCtrlRegs.PIECTRL.bit.ENPIE = 1; // Enable the PIE block使能PIE -

PieCtrlRegs.PIEIER1.bit.INTx5= 1; //使能第一组中的中断5 -

IER |= M_INT1; // Enable CPU 第一组中断 -

EINT; // Enable Global interrupt INTM -

ERTM; // Enable Global realtime interrupt DBGM

也就是说,12组中的每个中断都要完成上面的相同配置,剩下的才是去配置自己的中断。如我们提到的EXINT,即外面来个低电平我们就进入中断,完成我们的程序。在这里要介绍一下,DSP的GPIO口都可以配置为外部中断口,其配置方法如下:

-

GpioCtrlRegs.GPBMUX2.bit.GPIO54 = 0; //选择他们是GPIO口 -

GpioCtrlRegs.GPBMUX2.bit.GPIO55 = 0; -

GpioCtrlRegs.GPBMUX2.bit.GPIO56 = 0; -

GpioCtrlRegs.GPBMUX2.bit.GPIO57 = 0; -

GpioCtrlRegs.GPBDIR.bit.GPIO54 = 0;//选择他们都是输入口 -

GpioCtrlRegs.GPBDIR.bit.GPIO55 = 0; -

GpioCtrlRegs.GPBDIR.bit.GPIO56 = 0; -

GpioCtrlRegs.GPBDIR.bit.GPIO57 = 0; -

GpioCtrlRegs.GPBQSEL2.bit.GPIO54= 0;//GPIO时钟和系统时钟一样且支持GPIO -

GpioCtrlRegs.GPBQSEL2.bit.GPIO55= 0; -

GpioCtrlRegs.GPBQSEL2.bit.GPIO56= 0; -

GpioCtrlRegs.GPBQSEL2.bit.GPIO57= 0; -

GpioIntRegs.GPIOXINT3SEL.bit.GPIOSEL = 54;//中断3选择GPIO -

GpioIntRegs.GPIOXINT4SEL.bit.GPIOSEL = 55; -

GpioIntRegs.GPIOXINT5SEL.bit.GPIOSEL = 56; -

GpioIntRegs.GPIOXINT6SEL.bit.GPIOSEL = 57; -

XIntruptRegs.XINT3CR.bit.POLARITY= 0;//触发模式为下降沿触发 -

XIntruptRegs.XINT4CR.bit.POLARITY= 0; -

XIntruptRegs.XINT5CR.bit.POLARITY= 0; -

XIntruptRegs.XINT6CR.bit.POLARITY= 0; -

XIntruptRegs.XINT3CR.bit.ENABLE = 1;//使能中断 -

XIntruptRegs.XINT4CR.bit.ENABLE = 1; -

XIntruptRegs.XINT5CR.bit.ENABLE = 1; -

XIntruptRegs.XINT6CR.bit.ENABLE = 1;

- 设置中断向量。例如:PieVectTable.ADCINT = &adc_isr;等

- 打开PIE控制器。PieCtrlRegs.PIECTRL.bit.ENPIE = 1;

- 使能PIE中对应外设的中断(相应group的相应pin)。例如:PieCtrlRegs.PIEIER1.bit.INTx8 = 1; PieCtrlRegs.PIEIER1.bit.INTx6 = 1;等

- 使能CPU的相应中断(INT1~INT12)IER |= M_INT1;

- 使能CPU响应中断EINT、ERTM;;