目录

一、vivado中cell port net 和pin之间的关系

- cell 一般指我们在代码中实例化的模块,也可以是我们综合后可以看到的LUT、block RAM 、DSP、MMCM以及PLL等。

- pin 每个cell都有相应的pin,也即模块的输入输出信号,并非芯片的引脚。

- net 即pin与pin之间的连线

- port 我们在顶层文件中声明的输入输出信号,与FPGA外部的芯片进行通信的管脚

- package pin 即FPGA的实际的物理引脚,也即大家在实现时为每个端口分配的引脚号。

二、基本的命令 get_*

- -hier 即遍历每一层去寻找目标

e.g. 上图为我们设计的top层包含两个模块A和B ,其中A包含A1和A2 ,B 包含B1和B2.

对于命令 get_cells {A* B*} 返回的结果为 A B

命令get_cells -hier {A* B*} 返回的结果为 A A/A1 A/A2 B B/B1 B/B2 - -of 即在-of 后面的结果中搜寻

e.g. 命令get_nets -of [get_cells demuxstate] 此命令返回所有与cell demuxstate相连的nets - -filter 即得到满足相条件的目标

- Tips

1.[ ]: 在TCL命令中括号的代码会被当做表达式(变量,或函数)执行

- { }: Tcl 中的大括号除了用作分割代码片段外(如 if while 这样的语句需要用大括号),还被用来做字符串表达。与双引号不同的是其中的方括号中的表达式不会被执行。

3. . 和 * : 为通配符 点表示一位而星号表示多位

三、时序分析中常用的约束命令

-

创建基本的时钟约束语句

- Primary clock 为我们板子的主时钟,一般通过CC引脚输入FPGA 在进行时序约束之前必须首先定义一个primary clock。

创建上图的时钟tcl命令如下:1. creat_clock -period 10 [get_ports sysclk]-

Genrated Clock 有两类时钟一是用户自定义,而是自动推断的时钟

- 用户自动的时钟 一般是用户通过代码产生的时钟,需要通过相应的tcl命令来告诉综合器哪些为时钟信号。

e.g.

1. creat_clock -name clkin -period 10 [get_ports clkin] #创建primary clock 2. creat_generated_clock -name clkdiv2 -source [get_ports clkin] -divide_by 2 [get_pins REGA/Q]- 自动推断时钟 通过MMCM PLL或BUFR源语产生的时钟

- 用户自动的时钟 一般是用户通过代码产生的时钟,需要通过相应的tcl命令来告诉综合器哪些为时钟信号。

-

Clock Group 即对时钟进行分类与分组

- 异步时钟组 对于异步的时钟,我们需要告诉时序约束工具不同时钟间的异步关系

set_clock_groups -name async_clk0_clk1 -asynchronous -group [get_clocks -include_generated_clocks clk0] -group [get_clocks -include_generated_clocks clk1]

- Exclusive Clock Groups

尽管有两个同步时钟clk0和clk1但是这两个时钟在同一是时刻只有一个起作用,所以需要告诉时序分析工具,此两个时钟为 exclusive clocks ,不需要同时进行时序分析set_clock_groups -name exclusive_clk0_clk1 -physically_exclusive -group clk0 -group clk1- Unexpandable Clock Groups即时钟周期没有做大公倍数,此时时序工具也无法分析,我们可以通过改变周期,如果设计要求无法改变,我们可以通过set_false_path来告诉时序分析工具。

- 异步时钟组 对于异步的时钟,我们需要告诉时序约束工具不同时钟间的异步关系

-

Genrated Clock 有两类时钟一是用户自定义,而是自动推断的时钟

- Primary clock 为我们板子的主时钟,一般通过CC引脚输入FPGA 在进行时序约束之前必须首先定义一个primary clock。

-

创建输入时钟约束语句

-

Input delay

图中蓝 {MOD}虚线部分即为输入延时,包含全部的源时钟延时和信号进入FPGA芯片内部之前的数据延时

设置输入延时的大小命令如下:creat_clock -name sysclk -period 10 [get_ports clkin] set_input_delay -clock sysclk 4 [get_ports din] -

完整的静态时序约束

一个完整的时序路径即源时钟延迟、数据路径延迟和目的时钟延迟构成一个源.

creat_clock -name sysclk -period 10 [get_ports clkin] set_input_delay -clock sysclk -max 4 [get_ports ain] set_input_delay -clock sysclk -min 2 [get_ports ain] -

Input delay

-

创建输出时钟约束语句

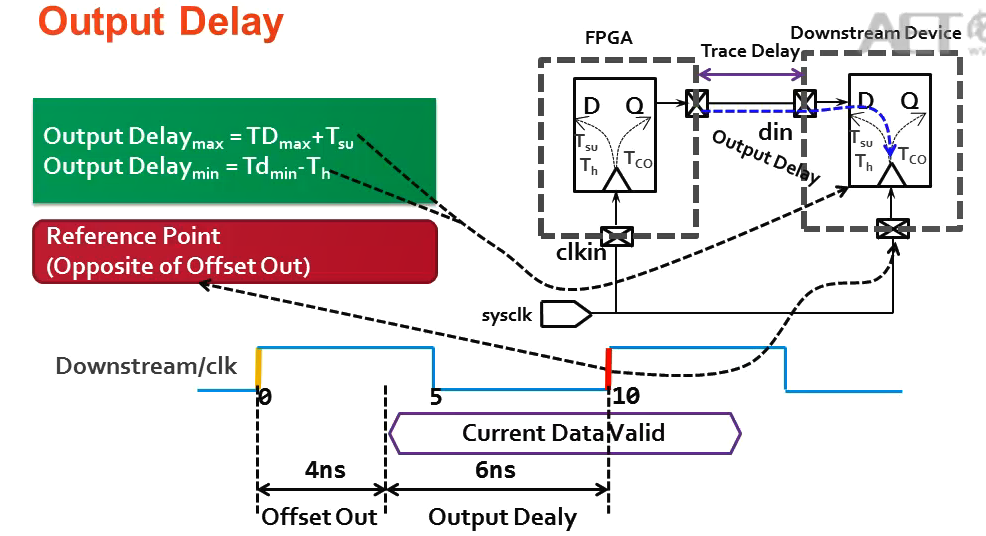

- Output Delay

图中蓝 {MOD}虚线即为输出延时 设置输出延时命令为:

creat_clock -name sysclk -period 10 [get_ports clkin] set_output_delay -clock sysclk [get_ports din]- 完整静态时钟约束

注意输入时钟延迟和输出时钟延迟的不同 由于输入数据路径不包括Tsu 和Thold 所以其最小值大于都等于0 ,而输出延时中数据路径延时包含Tsu 和Thold时间,所以其最小值一般为负。

- Output Delay

creat_clock -name sysclk -period 10 [get_ports clkin]

set_output_delay -clock sysclk -max 2 [get_ports dout]

srt_output_delay -clock sysclk -min -1 [get_ports dout]

-

创建虚拟时钟约束语句

-

虚拟时钟的两种应用场景

- 外部器件的频率和FPGA内部的频率不同

creat_clock -name sysclk -period 10 [get_ports clkin] creat_clock -name vclk -period 5 set_input_delay 6 -clock sysclk [get_ports dina] set_input_delay 6 -clock vclk [get_ports dinb]注意 vclk的时钟频率和internal clock的时钟频率相同- 虽为同一个时钟,但是外部有一个时钟延时

creat_clock -name sysclk -period 10 [get_ports clkin] creat_clock -name vclk -period 5 set_clock_latency -source 1 [get_clocks vclk] set_input_delay -clock vclk -max 4 [get_ports dina] set_input_delay -clock vclk -max 2 [get_ports dina]虚拟时钟只能用于IO时序分析,其与实体时钟的一个本质区别是虚拟时钟,不与任何管脚绑定。 - 外部器件的频率和FPGA内部的频率不同

-

虚拟时钟的两种应用场景

-

创建多周期时钟约束语句

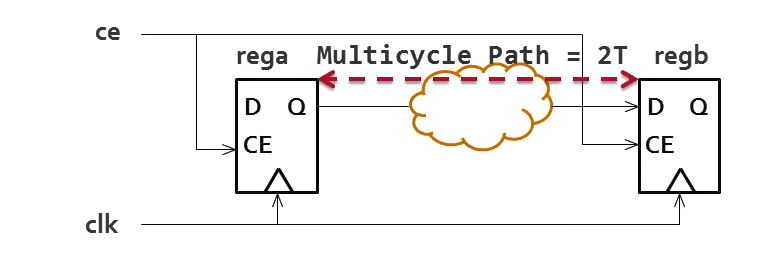

多周期时钟路径是为了放松相应时序电路的要求

由于ce(假设ce一周期为高一周期)的控制,此电路实际的周期为clk的2倍,因此我们不必以clk的周期来对此电路进行时序分析,为此我们需要设置一个周期为clk两倍的时序分析。

图中红 {MOD}虚线是为时序分析时默认的捕获沿,而我们其实无需这么苛刻的时序要求,因此我们需要告诉工具实际的分析点是图中2的位置。

由于我们重新指定setup的分析点为2 所以默认的hold点变为1,我们需要重新制定0为实际的分析点。

set_multicycle_path -from [get_cells rega] -to [get_cells regb] -setup -end 2

set_multicycle_path -from [get_cells rega] -to [get_cells regb] -hold -end 1

-setup表示该周期路径所需要的时钟周期的个数;-hold表示相对于缺省的捕获沿,实际捕获沿迎回调的周期-end和-start是指上面所说时钟周期个数的参考时钟,-end表示参考时钟为捕获端所用时钟,也就是驱动regb的时钟,并非指捕获沿 -start表示参考时钟为发送端所用时钟,也就是去驱动rega的时钟,并非指发送沿。

- 创建伪路径时钟约束语句

伪路径是指存在我们的设计当中,但是没有发挥真正的功能,因此我们无需对其进行分析。这样就可以给我们带来一些好处,比如去除无效的时序路径,节约时间和资源(综合器跳过对伪路径的优化)。

上图中是典型的跨时钟域设计中拍二拍电路,其中蓝 {MOD}圈中的电路我们无需对其进行时序分析,因此我们可以做如下约束:

set_false_path -from [get_clocks clka] -to [get_clocks clkb]

set_false_path -from [get_clocks clkb] -to [get_clocks clka]

上面的语句和时钟分组约束的效果是一样的。