看了手册关于电源控制的这一张,我觉得先了解下相关寄存器比较好,而且相关寄存器只有两个,看完就还不容易忘记,如果按照手册上的读,看完前面的,再去看寄存器,前面的已经忘了。看完寄存器,脑子里面还能有点印象,刚好看前面的,就很有节奏感。借此做如下总结:

供电: VDD:2.0V--3.6V; 内嵌的电压管理器为内部数字区域分配1.8V电压; VBAT:当VDD不供电时,为RTC和Backup供电。通俗就是电池供电。

独立的A/D和D/A供电和参考电压: 为了提高转换精度,ADC和DAC需要独立的可以被滤波和从噪声中屏蔽的供电电源:VDDA作为供电输入,VSSA作为孤立的地,VREF-必须和VSSA连接;(这里我有个地方不太懂,前面说VDDA和VSSA必须相应连接VDD和VSS,这里又说需要使用VDDA和VSSA为ADC和DAC独立供电,这里很明显前后矛盾了,我在相关的群里问过,有人回答一般应用里面是直接连起来的。今天本打算去问老师,下课时,被拥挤的人流阻挡。。。如果大家有更好的建议,谢谢留言!) 在100-Pin和144-Pin中,VREF+是需要连接参考电压的,范围:2.4V--VDDA; 在少于等于64-Pin中,VREF-和VREF+都是不可用的,内部自动连接了ADC的VDDA和VSSA; 电池备份区域: 通过图,很好理解VBAT为那些东西(RTC单元、LSE振荡器、PC13、PC14、PC15)供电,实现从VDD转向VBAT供电,是通过复位模块的掉电复位PDR实现的。 在上升时间或者检测到一个PDR时,VBAT和VDD之间的切换还是保持在VBAT;在启动的时候,如果VDD稳定的时间小于上升时间TRSTTEMPO,并且VDD>VBAT+0.6V,一个电流就会从内部的连接VDD和Switch的二极管进去VBAT;如果VBAT不能承受这个电压,可以在VDD和VBAT之间放一个二极管。 不使用外部电池的时候,可以直接通过一个陶瓷二极管把VBAT和VDD连接. Backup由VDD供电: PC14和PC15可以被用作GPIO口和LSE; PC13可以用作GPIO、TAMPER、RTC校验时钟、RTC Alarm或者秒输出(register:BKR) PC13 to PC15不能用作电流源,最大输出3mA,最高速度2MHz和最大负载30pF Backup由VBAT供电: PC14和PC15可用作LSE; PC13可用作TAMPER,RTC Alarm或者秒输出(register:BKP_RTCCR); 电压管理器: 复位后自动使能,三种模式: Run mode:为1.8V区域(core、memories和数字外设)正常供电; Stop mode:为1.8V提供低电源,保存SRAM中的内容; Standby mode:regulator被断电,除了Standby电路和Backup区域,寄存器、SRAM内容丢失; 供电管理器: POR和PDR:上升/下降到2V,复位启动;

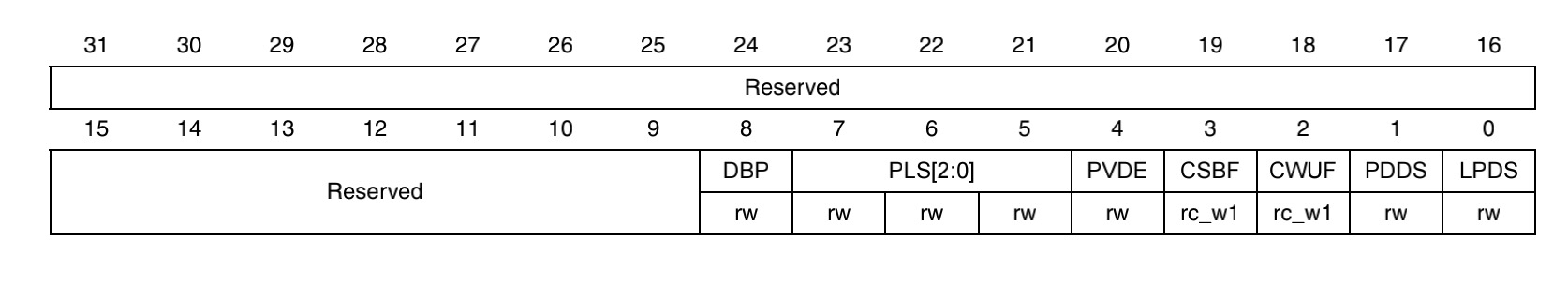

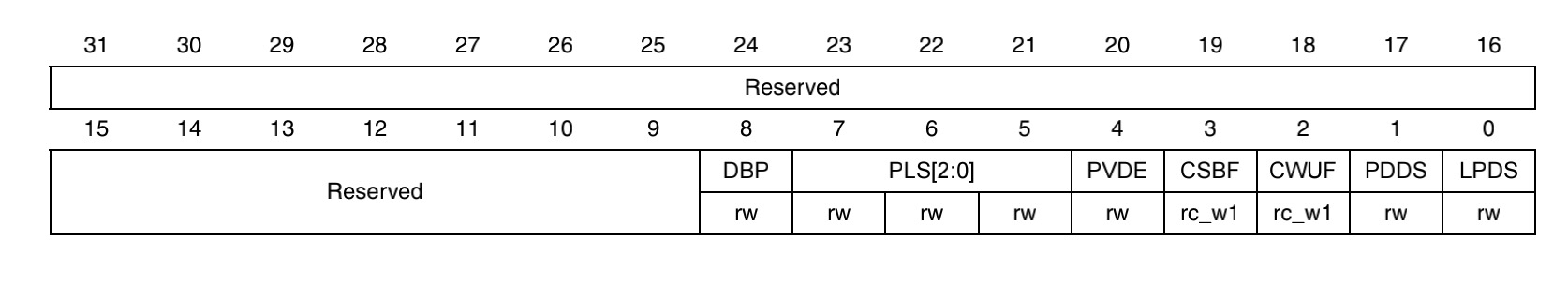

相关寄存器: 电源控制寄存器(PWR_CR): DBP:消除备份区域的写保护,在复位状态,RTC和Backup寄存器被保护不被寄生的写入,为了对这些寄存器进行写操作,必须对DBP置位;

PLS[2:0]:PVD的等级选择

000--2.2V 001--2.3V 010--2.4V 011--2.5V .... 111--2.9V

PVDE:PVD使能位

CSBF:清楚待机标志位

CWUF:清楚唤醒标志位

PDDS:掉电深入睡眠位,同LPDS一起工作

0--当CPU进入深度睡眠,进入Stop模式,regulator状态由LPDS决定

1--当CPU进入深度睡眠,进入Standby模式

LPDS:低电源深度睡眠

0--电压管理器正常工作在Stop模式

1--电压管理器在Stop模式下出去低电源

电源控制/状态寄存器(PWR_CSR):

DBP:消除备份区域的写保护,在复位状态,RTC和Backup寄存器被保护不被寄生的写入,为了对这些寄存器进行写操作,必须对DBP置位;

PLS[2:0]:PVD的等级选择

000--2.2V 001--2.3V 010--2.4V 011--2.5V .... 111--2.9V

PVDE:PVD使能位

CSBF:清楚待机标志位

CWUF:清楚唤醒标志位

PDDS:掉电深入睡眠位,同LPDS一起工作

0--当CPU进入深度睡眠,进入Stop模式,regulator状态由LPDS决定

1--当CPU进入深度睡眠,进入Standby模式

LPDS:低电源深度睡眠

0--电压管理器正常工作在Stop模式

1--电压管理器在Stop模式下出去低电源

电源控制/状态寄存器(PWR_CSR): EWUP:使能WKUP引脚,该位需要通过系统复位来复位

0--WKUP引脚被用作通用IO口,一个Event不会使CPU从Standby模式恢复;

1--WKUP引脚被用来唤醒CPU从Standby模式,并且强迫使输入电平拉低,当检测当上升沿的时候,CPU苏醒;

PVDO:PVD的输出,只有当PVDE被置位时,该位才有效.PVD会被Standby模式停止掉,PVD为0,当从Standby模式和 Reset启动后

0--VDD/VSSA比PLS中选中的电压高;

1--VDD/VSSA比PLS中选中的电压低;

SBF:Standby标志位(硬件置位,通过POR/PDR或者CSBF--PWR_CR位清0)

WUF:Wakeup标志位(硬件置位,通过硬件、系统复位、CWUF--PWR_CR位清0)

EWUP:使能WKUP引脚,该位需要通过系统复位来复位

0--WKUP引脚被用作通用IO口,一个Event不会使CPU从Standby模式恢复;

1--WKUP引脚被用来唤醒CPU从Standby模式,并且强迫使输入电平拉低,当检测当上升沿的时候,CPU苏醒;

PVDO:PVD的输出,只有当PVDE被置位时,该位才有效.PVD会被Standby模式停止掉,PVD为0,当从Standby模式和 Reset启动后

0--VDD/VSSA比PLS中选中的电压高;

1--VDD/VSSA比PLS中选中的电压低;

SBF:Standby标志位(硬件置位,通过POR/PDR或者CSBF--PWR_CR位清0)

WUF:Wakeup标志位(硬件置位,通过硬件、系统复位、CWUF--PWR_CR位清0)

PVD可编程电压检测器: PVDE位使能;

监视VDD和VDDA的供电,通过和PLS[2:0](PWR_CR)中选择的电压比较,PVDO标志位指示状态; 内部连接EXTI 16,使能EXTI寄存器,可以产生中断。当VDD/VDDA上升超过或者下降低于PVD设定值,就可以通过EXTI16产生中断输出。 低电源模式:

默认情况下,系统和电源复位,微控制器是在Run模式。

stm32f10XXX有三种低电源模式:

Sleep mode:CPU时钟关闭,其它保持;

Stop mode:所有时钟关闭;

Standby mode:1.8V区域断电;

通过降低系统时钟(RCC_CFGR)、APB时钟(RCC_APB1ENR、RCC_APB2ENR)和AHB外设可以降低能耗在Run mode下。

低电源模式:

默认情况下,系统和电源复位,微控制器是在Run模式。

stm32f10XXX有三种低电源模式:

Sleep mode:CPU时钟关闭,其它保持;

Stop mode:所有时钟关闭;

Standby mode:1.8V区域断电;

通过降低系统时钟(RCC_CFGR)、APB时钟(RCC_APB1ENR、RCC_APB2ENR)和AHB外设可以降低能耗在Run mode下。

解释几个简写: WFI:Wait For Interrupt WFE:Wait For Event

Sleep mode: Sleep-now:SLEEPONEXIT清除,只要WFI和WFE指令执行,MCU就进入Sleep模式; Sleep-on-exit:SLEEPONEXIT被置位,只要退出最低权限ISR,MCU就进入Sleep模式; 在Sleep模式下,所有的I/O口保持相同的状态在Run模式下; 这种模式的唤醒实践最长,因为浪费在了中断进入和中断离开;

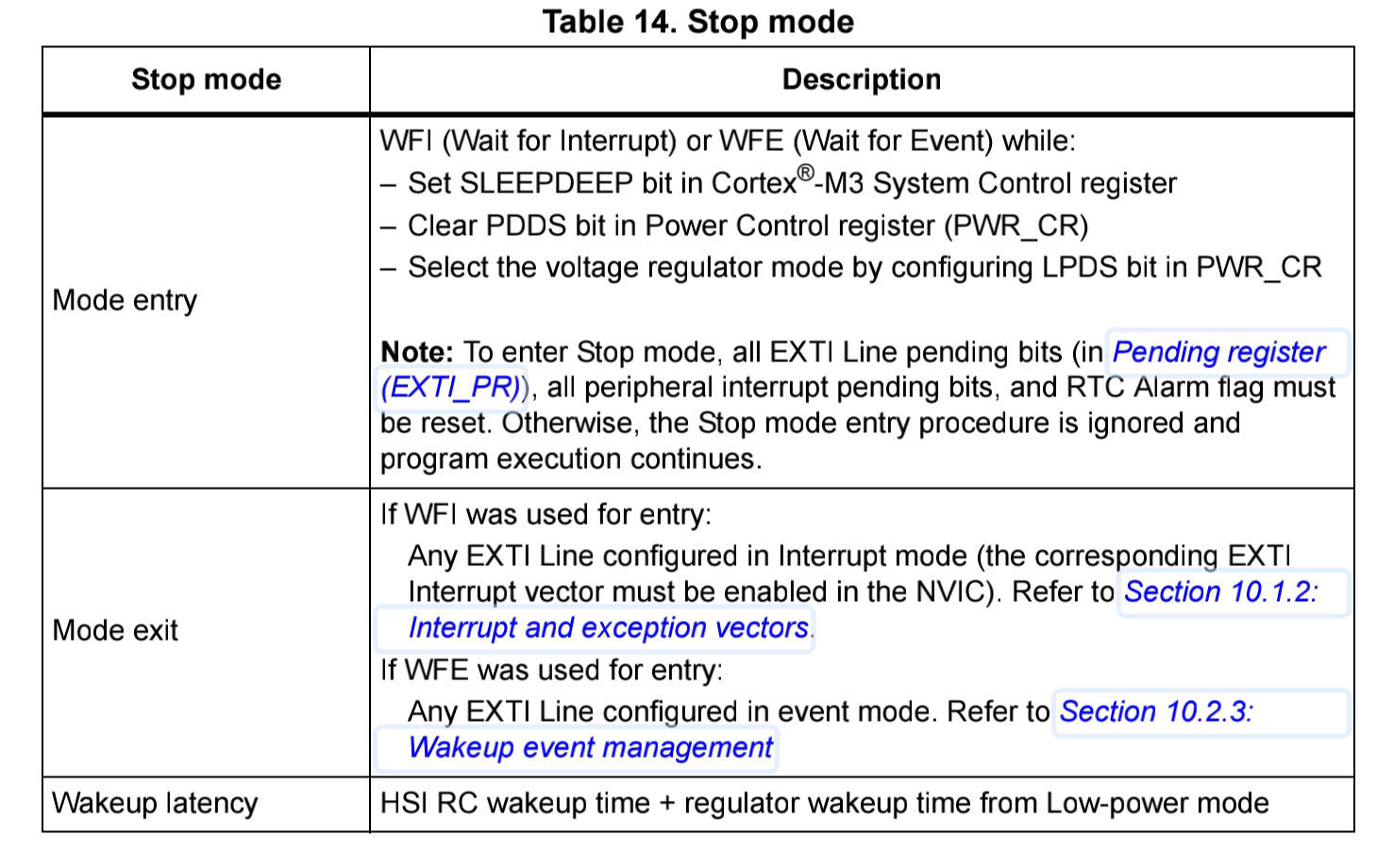

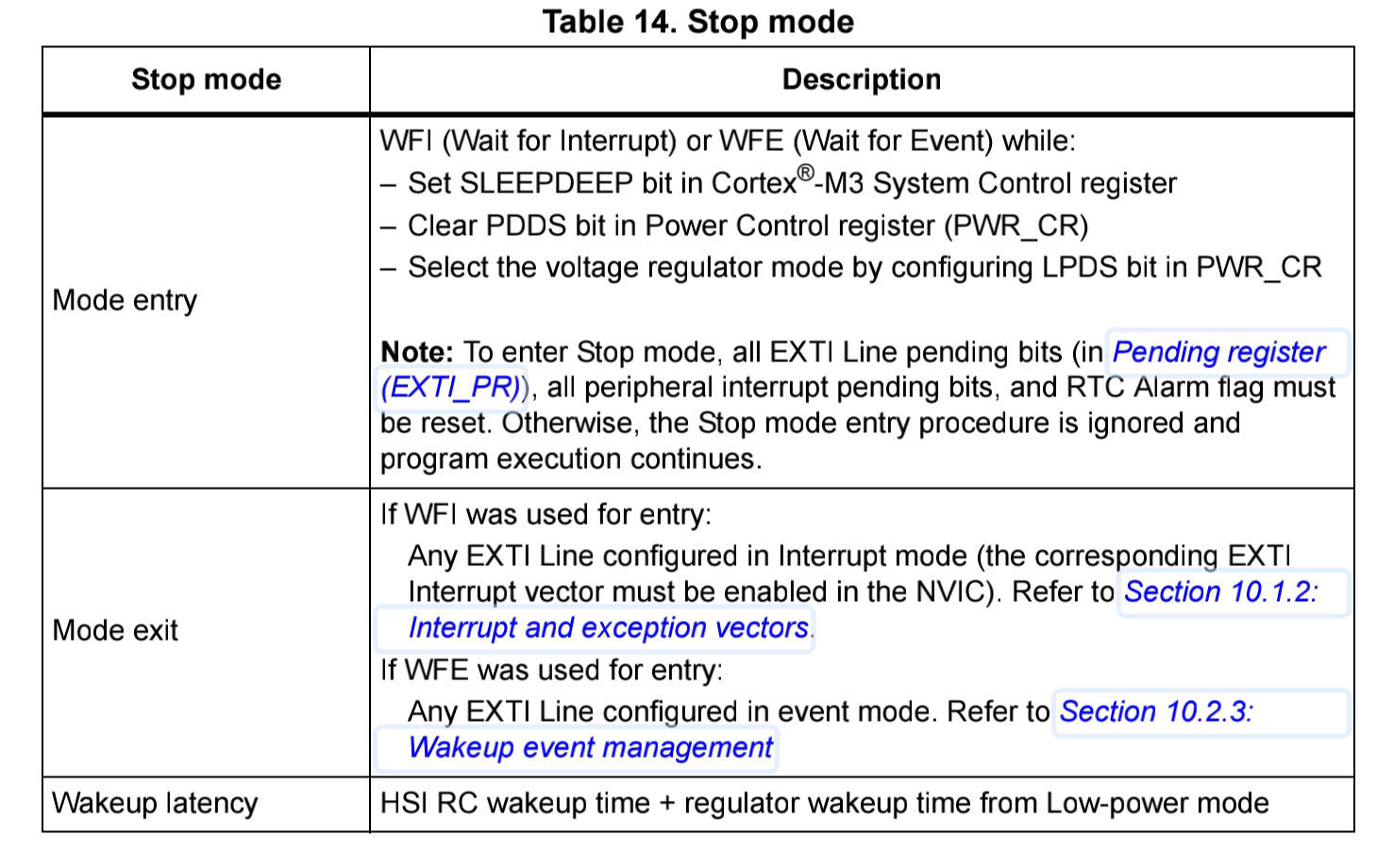

Stop mde: SRAM和寄存器中的内容被保持; 所有的I/O口保持在相同状态,在Run mode下; 内部电源管理器可以被设置为低电源模式(PWR_CR的LPDS位),再降低能耗; 如果编程或者APB通道正在进行,Stop模式的进入会延迟; 在此模式下,通过编程可以选择如下功能: IWDG:一旦开始,就只能通过复位关闭; RTC:RCC_BDCR的RTCE位使能; LSI RC:RCC_CSR的LSION位配置; LSE OSC:RCC_BDCR的LSEON位配置; ADC和DAC在Stop模式下会消耗电能,除非在进入Stop之前关闭。ADON(ADC_CR2)和ENx(DAC_CR)必须为0;

Standby mode: 该模式的能耗最低,基于Cortex-m3的深度睡眠,1.8V区域断电,PLL、HSI、HSE关闭,SRAM和寄存器内容丢失,只有Backup区域的寄存器和Standby电路保持;

在此模式下,通过编程可以选择如下功能: IWDG:一旦开始,就只能通过复位关闭; RTC:RCC_BDCR的RTCE位使能; LSI RC:RCC_CSR的LSION位配置; LSE OSC:RCC_BDCR的LSEON位配置;

I/O状态: 所有I/O为高阻态,除了: Reset 管脚; TAMPER引脚(温度传感器或者校验输出) WKUP引脚,如果使能; 通过配置DBGMCU_CR寄存器,软件可以调试,即使处于低电源模式; RTC可以用来唤醒MCU从低电源模式;

供电: VDD:2.0V--3.6V; 内嵌的电压管理器为内部数字区域分配1.8V电压; VBAT:当VDD不供电时,为RTC和Backup供电。通俗就是电池供电。

独立的A/D和D/A供电和参考电压: 为了提高转换精度,ADC和DAC需要独立的可以被滤波和从噪声中屏蔽的供电电源:VDDA作为供电输入,VSSA作为孤立的地,VREF-必须和VSSA连接;(这里我有个地方不太懂,前面说VDDA和VSSA必须相应连接VDD和VSS,这里又说需要使用VDDA和VSSA为ADC和DAC独立供电,这里很明显前后矛盾了,我在相关的群里问过,有人回答一般应用里面是直接连起来的。今天本打算去问老师,下课时,被拥挤的人流阻挡。。。如果大家有更好的建议,谢谢留言!) 在100-Pin和144-Pin中,VREF+是需要连接参考电压的,范围:2.4V--VDDA; 在少于等于64-Pin中,VREF-和VREF+都是不可用的,内部自动连接了ADC的VDDA和VSSA; 电池备份区域: 通过图,很好理解VBAT为那些东西(RTC单元、LSE振荡器、PC13、PC14、PC15)供电,实现从VDD转向VBAT供电,是通过复位模块的掉电复位PDR实现的。 在上升时间或者检测到一个PDR时,VBAT和VDD之间的切换还是保持在VBAT;在启动的时候,如果VDD稳定的时间小于上升时间TRSTTEMPO,并且VDD>VBAT+0.6V,一个电流就会从内部的连接VDD和Switch的二极管进去VBAT;如果VBAT不能承受这个电压,可以在VDD和VBAT之间放一个二极管。 不使用外部电池的时候,可以直接通过一个陶瓷二极管把VBAT和VDD连接. Backup由VDD供电: PC14和PC15可以被用作GPIO口和LSE; PC13可以用作GPIO、TAMPER、RTC校验时钟、RTC Alarm或者秒输出(register:BKR) PC13 to PC15不能用作电流源,最大输出3mA,最高速度2MHz和最大负载30pF Backup由VBAT供电: PC14和PC15可用作LSE; PC13可用作TAMPER,RTC Alarm或者秒输出(register:BKP_RTCCR); 电压管理器: 复位后自动使能,三种模式: Run mode:为1.8V区域(core、memories和数字外设)正常供电; Stop mode:为1.8V提供低电源,保存SRAM中的内容; Standby mode:regulator被断电,除了Standby电路和Backup区域,寄存器、SRAM内容丢失; 供电管理器: POR和PDR:上升/下降到2V,复位启动;

相关寄存器: 电源控制寄存器(PWR_CR):

DBP:消除备份区域的写保护,在复位状态,RTC和Backup寄存器被保护不被寄生的写入,为了对这些寄存器进行写操作,必须对DBP置位;

PLS[2:0]:PVD的等级选择

000--2.2V 001--2.3V 010--2.4V 011--2.5V .... 111--2.9V

PVDE:PVD使能位

CSBF:清楚待机标志位

CWUF:清楚唤醒标志位

PDDS:掉电深入睡眠位,同LPDS一起工作

0--当CPU进入深度睡眠,进入Stop模式,regulator状态由LPDS决定

1--当CPU进入深度睡眠,进入Standby模式

LPDS:低电源深度睡眠

0--电压管理器正常工作在Stop模式

1--电压管理器在Stop模式下出去低电源

电源控制/状态寄存器(PWR_CSR):

DBP:消除备份区域的写保护,在复位状态,RTC和Backup寄存器被保护不被寄生的写入,为了对这些寄存器进行写操作,必须对DBP置位;

PLS[2:0]:PVD的等级选择

000--2.2V 001--2.3V 010--2.4V 011--2.5V .... 111--2.9V

PVDE:PVD使能位

CSBF:清楚待机标志位

CWUF:清楚唤醒标志位

PDDS:掉电深入睡眠位,同LPDS一起工作

0--当CPU进入深度睡眠,进入Stop模式,regulator状态由LPDS决定

1--当CPU进入深度睡眠,进入Standby模式

LPDS:低电源深度睡眠

0--电压管理器正常工作在Stop模式

1--电压管理器在Stop模式下出去低电源

电源控制/状态寄存器(PWR_CSR): EWUP:使能WKUP引脚,该位需要通过系统复位来复位

0--WKUP引脚被用作通用IO口,一个Event不会使CPU从Standby模式恢复;

1--WKUP引脚被用来唤醒CPU从Standby模式,并且强迫使输入电平拉低,当检测当上升沿的时候,CPU苏醒;

PVDO:PVD的输出,只有当PVDE被置位时,该位才有效.PVD会被Standby模式停止掉,PVD为0,当从Standby模式和 Reset启动后

0--VDD/VSSA比PLS中选中的电压高;

1--VDD/VSSA比PLS中选中的电压低;

SBF:Standby标志位(硬件置位,通过POR/PDR或者CSBF--PWR_CR位清0)

WUF:Wakeup标志位(硬件置位,通过硬件、系统复位、CWUF--PWR_CR位清0)

EWUP:使能WKUP引脚,该位需要通过系统复位来复位

0--WKUP引脚被用作通用IO口,一个Event不会使CPU从Standby模式恢复;

1--WKUP引脚被用来唤醒CPU从Standby模式,并且强迫使输入电平拉低,当检测当上升沿的时候,CPU苏醒;

PVDO:PVD的输出,只有当PVDE被置位时,该位才有效.PVD会被Standby模式停止掉,PVD为0,当从Standby模式和 Reset启动后

0--VDD/VSSA比PLS中选中的电压高;

1--VDD/VSSA比PLS中选中的电压低;

SBF:Standby标志位(硬件置位,通过POR/PDR或者CSBF--PWR_CR位清0)

WUF:Wakeup标志位(硬件置位,通过硬件、系统复位、CWUF--PWR_CR位清0)

PVD可编程电压检测器: PVDE位使能;

监视VDD和VDDA的供电,通过和PLS[2:0](PWR_CR)中选择的电压比较,PVDO标志位指示状态; 内部连接EXTI 16,使能EXTI寄存器,可以产生中断。当VDD/VDDA上升超过或者下降低于PVD设定值,就可以通过EXTI16产生中断输出。

低电源模式:

默认情况下,系统和电源复位,微控制器是在Run模式。

stm32f10XXX有三种低电源模式:

Sleep mode:CPU时钟关闭,其它保持;

Stop mode:所有时钟关闭;

Standby mode:1.8V区域断电;

通过降低系统时钟(RCC_CFGR)、APB时钟(RCC_APB1ENR、RCC_APB2ENR)和AHB外设可以降低能耗在Run mode下。

低电源模式:

默认情况下,系统和电源复位,微控制器是在Run模式。

stm32f10XXX有三种低电源模式:

Sleep mode:CPU时钟关闭,其它保持;

Stop mode:所有时钟关闭;

Standby mode:1.8V区域断电;

通过降低系统时钟(RCC_CFGR)、APB时钟(RCC_APB1ENR、RCC_APB2ENR)和AHB外设可以降低能耗在Run mode下。

解释几个简写: WFI:Wait For Interrupt WFE:Wait For Event

Sleep mode: Sleep-now:SLEEPONEXIT清除,只要WFI和WFE指令执行,MCU就进入Sleep模式; Sleep-on-exit:SLEEPONEXIT被置位,只要退出最低权限ISR,MCU就进入Sleep模式; 在Sleep模式下,所有的I/O口保持相同的状态在Run模式下; 这种模式的唤醒实践最长,因为浪费在了中断进入和中断离开;

Stop mde: SRAM和寄存器中的内容被保持; 所有的I/O口保持在相同状态,在Run mode下; 内部电源管理器可以被设置为低电源模式(PWR_CR的LPDS位),再降低能耗; 如果编程或者APB通道正在进行,Stop模式的进入会延迟; 在此模式下,通过编程可以选择如下功能: IWDG:一旦开始,就只能通过复位关闭; RTC:RCC_BDCR的RTCE位使能; LSI RC:RCC_CSR的LSION位配置; LSE OSC:RCC_BDCR的LSEON位配置; ADC和DAC在Stop模式下会消耗电能,除非在进入Stop之前关闭。ADON(ADC_CR2)和ENx(DAC_CR)必须为0;

Standby mode: 该模式的能耗最低,基于Cortex-m3的深度睡眠,1.8V区域断电,PLL、HSI、HSE关闭,SRAM和寄存器内容丢失,只有Backup区域的寄存器和Standby电路保持;

在此模式下,通过编程可以选择如下功能: IWDG:一旦开始,就只能通过复位关闭; RTC:RCC_BDCR的RTCE位使能; LSI RC:RCC_CSR的LSION位配置; LSE OSC:RCC_BDCR的LSEON位配置;

I/O状态: 所有I/O为高阻态,除了: Reset 管脚; TAMPER引脚(温度传感器或者校验输出) WKUP引脚,如果使能; 通过配置DBGMCU_CR寄存器,软件可以调试,即使处于低电源模式; RTC可以用来唤醒MCU从低电源模式;