为 FPGA 应用设计优秀电源管理解决方案不是一项简单的任务,相关的技术讨论有很多很多。今天小编要为大家分享的内容『FPGA 的电源管理』主要有两个目的——

☞找到正确解决方案并选择最合适的电源管理产品

☞ 如何优化实际解决方案使其用于 FPGA

找到合适的电源解决方案

寻找为 FPGA 供电的最佳解决方案并不简单。许多供应商以适合为 FPGA 供电的名义推销某些产品。为 FPGA 供电的 DC-DC 转换器选择有何特定要求?其实并不多。一般而言,所有电源转换器都可用来为 FPGA 供电。推荐某些产品通常是基于以下事实:许多FPGA应用需要多个电压轨,例如用于 FPGA 内核和 I/O,还可能需要额外的电压轨来用于 DDR 存储器。

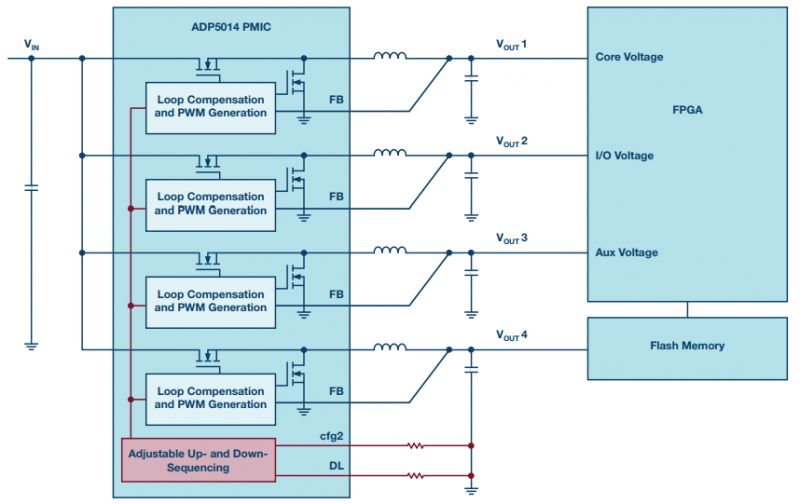

将多个DC-DC 转换器全部集成到单个稳压器芯片中的 PMIC(电源管理集成电路)常常是首选。

一种为特定 FPGA 寻找优秀供电解决方案的流行方法是使用许多FPGA 供应商都提供的已有电源管理参考设计。这对于优化设计来说是一个很好的入门方式。但此类设计往往需要修改,因为

- FPGA系统通常需要额外的电压轨和负载,这些也需要供电;

- 在参考设计上增加一些东西常常也是必要的;

- FPGA 的输入电源不是固定的,输入电压在很大程度上取决于实际的逻辑电平以及 FPGA 所实现的设计。

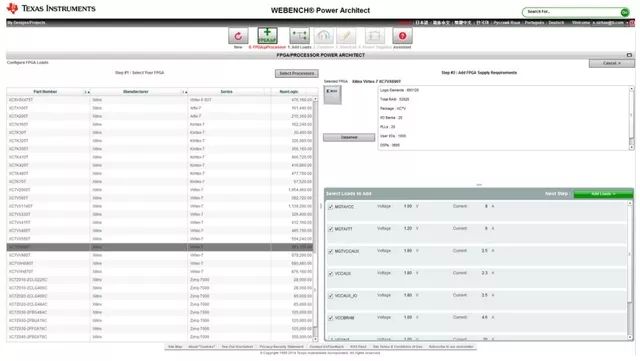

完成对电源管理参考设计的修改之后,它看起来将与最初的参考设计不同。可能有人会辩称,最好的解决方案是根本不用电源管理参考设计,而是直接将所需的电压轨和电流输入到电源管理选型与优化工具中,例如 ADI公司的 LTpowerCAD 等。

图1. 通过 LTpowerCAD 工具选择合适的 DC-DC 转换器来为 FPGA 供电。

LTpowerCAD 可用来为各个电压轨提供电源解决方案。它还提供一系列参考设计,以让设计人员快速入门。LTpowerCAD 可以从 ADI公司网站免费下载。☞下载链接:http://www.analog.com/cn/design-center/ltpowercad.html

如何优化实际解决方案以用于FPGA

一旦选择了电源架构和各个电压转换器,就需要选择合适的无源元件来设计电源。做这件事时,需要牢记

FPGA 的特殊负载要求——

- 各项电流需求

- 电压轨时序控制

- 电压轨单调上升

- 快速电源瞬变

- 电压精度

- FPGA 输入电容

各项电流需求

FPGA 的实际电流消耗在很大程度上取决于使用情况。不同的时钟和不同的FPGA 内容需要不同的功率。因此,

在 FPGA 系统的设计过程中,典型 FPGA 设计的最终电源规格必然会发生变化。FPGA 制造商提供的功率估算工具有助于计算解决方案所需的功率等级。在构建实际硬件之前,获得这些信息会非常有用。但是,为了利用此类功率估算工具获得有意义的结果,FPGA 的设计必须最终确定,或者至少接近最终完成。

通常情况下,工程师设计电源时考虑的是最大 FPGA 电流。如果最终发现实际 FPGA 设计需要的功率更少,设计人员就会缩减电源。

电压轨时序控制

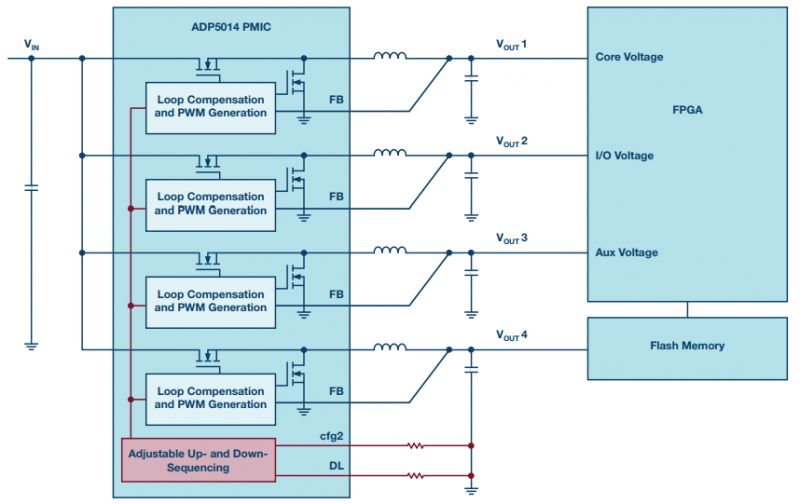

许多 FPGA 要求不同电源电压轨以特定顺序上电。内核电压的供应往往需要早于 I/O 电压的供应,否则一些 FPGA 会被损坏。为了避免这种情况,电源需要按正确的顺序上电。使用标准 DC-DC 转换器上的使能引脚,可以轻松实现简单的上电时序控制。然而,器件关断通常也需要时序控制。仅执行使能引脚时序控制,很难取得良好的结果。更好的解决办法是使用具有高级集成时序控制功能的PMIC,例如 ADP5014。图2中用红 {MOD}表示的特殊电路模块支持调整上电和关断时序。

图2. ADP5014 PMIC 集成了对灵活控制上电/关断时序的支持。

图 3 显示了利用此器件实现的时序控制。通过 ADP5014 上的延迟 (DL) 引脚可以轻松调整上电和关断时序的时间延迟。

图3. 多个FPGA电源电压的启动和关断顺序。

如果使用多个单独的电源,增加时序控制芯片便可实现所需的上电/关断顺序。一个例子是 LTC2924,它既能控制 DC-DC 转换器的使能引脚来打开和关闭电源,也能驱动高端 N 沟道 MOSFET 来将 FPGA 与某个电压轨连接和断开。

电压轨单调上升

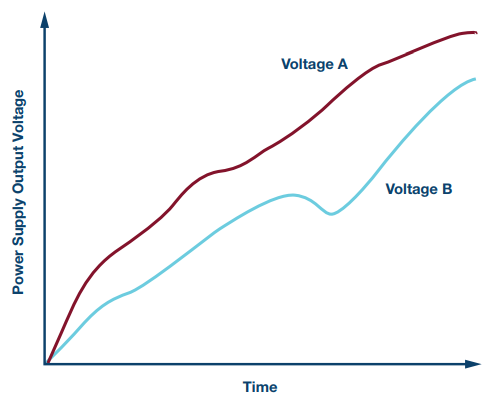

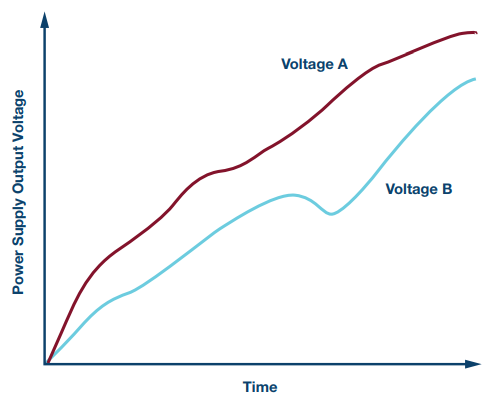

除了电压时序之外,启动过程中还可能要求电压单调上升。这意味着电压仅线性上升,如图 4 中的电压 A 所示。此图中的电压 B是电压非单调上升的例子。

在启动过程中,当电压上升到一定电平时负载开始拉大电流,就会发生这种情况。防止这种情况的一种办法是延长电源的软启动时间,并选择能够快速提供大量电流的电源转换器。

图4. 电压A单调上升,电压B非单调上升。

快速电源瞬变

FPGA 的另一个特点是它会非常迅速地开始抽取大量电流。这会在电源上造成很高的负载瞬变。出于这个原因,

许多 FPGA 需要大量的输入电压去耦。陶瓷电容非常靠近地用在器件的 VCORE 和 GND 引脚之间。高达 1 mF 的值非常常见。如此高电容有助于降低对电源提供非常高峰值电流的需求。但是,许多开关稳压器和 LDO 规定了最大输出电容。FPGA 的输入电容要求可能超过电源允 许的最大输出电容。

电源不喜欢非常大的输出电容,原因有两点——

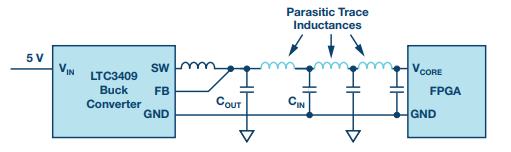

- 在启动期间,开关稳压器的输出电容看来像是短路的。对此问题有一个解决办法。较长的软启动时间可以让大电容组上的电压稳定地升高,电源不会进入短路限流模式。 图5. 很多FPGA的输入电容要求。

- 该电容值会成为调节环路的一部分。集成环路补偿的转换器不允许输出电容过大,以防止稳压器的环路不稳定。在高端反馈电阻上使用前馈电容常常可以影响控制环路,如图6所示。 图6. 当没有环路补偿引脚可用时,利用前馈电容可以调节控制环路。

针对电源的负载瞬变和启动行为,开发工具链(包括 LTpowerCAD,尤其是 LTspice)是非常有帮助的。该工具可以很好的建模和仿真,从而有效实现 FPGA 的大输入电容与电源的输出电容的去耦。 图 6 就展示了这一概念。

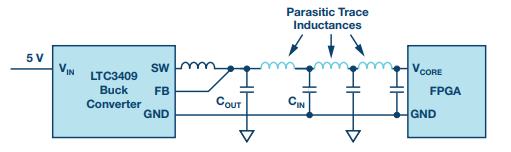

虽然 POL(负载端)电源的位置往往靠近负载,但在电源和 FPGA 输入电容之间常常存在一些 PCB 走线。当电路板上有多个彼此相邻的 FPGA 输入电容时,离电源最远的那些电容对电源传递函数的影响较小,因为它们之间不仅存在一些电阻,还存在寄生走线电感。这些寄生电感允许 FPGA 的输入电容大于电源输出电容的最大限值,即使所有电容都连接到电路板上的同一节点也无妨。在 LTspice 中,可以将寄生走线电感添加到原理图中,并且可以模拟这些影响。当电路建模中包含足够的寄生元件时,仿真结果接近实际结果。

图7. 电源输出电容与FPGA输入电容之间的寄生去耦。

电压精度

FPGA电源的电压精度通常要求非常高。3%的变化容差带是相当常见的。例如,为使0.85 V的Stratix V内核电压轨保持在3%的电压精度窗口内,要求全部容差带仅为25.5 mV。这个小窗口包括负载瞬变后的电压变化以及直流精度。同样,对于此类严格要求,包括LTpowerCAD和LTspice在内的可用电源工具链在电源设计过程中非常重要。

FPGA 输入电容

为了快速提供大电流,FPGA 的输入电容通常选择陶瓷电容。此类电容很适合这种用途,但需要小心选择,使其真实电容值不随直流偏置电压而下降。一些陶瓷电容,尤其是 Y5U 型,当直流偏置电压接近其最大额定直流电压时,其真实电容值会降低到只有标称值的20%

FPGA系统的复杂度越来越高,所以FPGA必须采用适当的

电源管理技术, 来设计针对FPGA系统的电源。

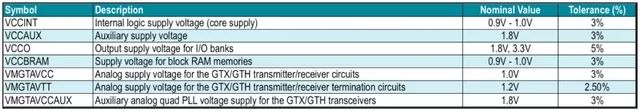

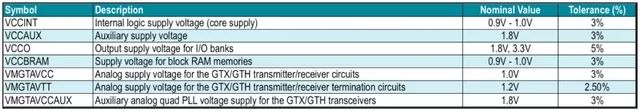

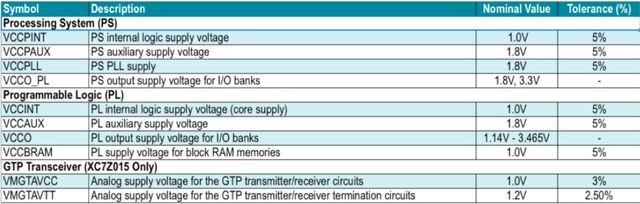

FPGA通常需要几个电压供电。根据应用的不同,主输入电源可以采用背板电源、隔离电源、非隔离电源,甚至是电池供电的方式。这些主输入通常产生一个中间DC电压来为FPGA的主电压供电。这些中间电压通常为5V或12V的DC电压。表1和表2中列出了FPGA的某些典型电压轨。

表1 Virtex 7FPGA的电源要求

表2 Zynq 7000系列片上系统 (SoC) 的电源要求

表2 Zynq 7000系列片上系统 (SoC) 的电源要求

Xilinx功率估算器

为每个电压确定合适的电流是一件比较棘手的工作,原因在于电流的范围可以从几百毫安到60A,甚至更高。如果事先进行规划的话,情况就会完全不同,事先规划可以避免对电源的过度设计和设计的不充份,从而导致必须推倒重来等错误。FPGA厂家提供了精确的FPGA功耗计算工具,可根据客户对FPGA的使用方式来估算出最差情况下的功耗。

图1中显示的Xilinx功率估算器 (XPE),涵盖了数个Xilinx FPGA系列。借助于这款工具,客户可以选择正在使用的部件,并且输入

时钟和配置信息,来确定电源需求,并且根据估算值来选择合适的器件。

图1 Xilinx功率估算器 (XPE)

图1 Xilinx功率估算器 (XPE)

设计注意事项

注意事项1

在选择一款符合FPGA应用需要的电源时,必须将很多因素考虑在内。成本、尺寸,以及效率,始终是电源设计过程中需要注意的因素。不过,在FPGA应用中,某些电源将会有不同的要求。内核电源通常需要在线路、负载和温度范围内保持更加严格的精度。某些电源,比如说

收发器,对于噪声更加敏感,并且需要将它们的输出保持在特定的噪声阀值以下。还需注意的是,某些具有共模电压的电源可组合在一起,并且可以用一个铁氧体磁珠进行隔离,以实现滤波或作为一个负载开关。

注意事项2

当进行符合容限要求方面的设计时,需要将全部的静态和动态运行条件考虑在内。首先,选择一款基准精度小于1%的稳压器,这为客户预留了最大的设计裕量空间来处理负载瞬变等动态运行条件。

注意事项3

在设计高速收发器电源时还需谨慎,因为这些灵敏电源输出的噪声会使性能下降,并且增加抖动。低压降稳压器 (

LDO) 是这些电源轨的理想选择。不过,当需要更高电流时,只要输出纹波的典型值在10kHz至80MHz频率范围内保持在10mVpk-pk以下,就可以使用

开关电源。专用FPGA数据表将包含与收发器需求相关的详细技术规格。

注意事项4

电源排序是FPGA电源设计时的另外一个重要方面。由于FPGA系统中需要多个电源供电,如图推荐的电源顺序在启动时汲取最小电流,这反过来防止了对器件的损坏。图2中显示的是针对Virtex 7系列FPGA上的逻辑电路和收发器电源的建议加电电源序列。针对Zynq 7000系列SoC的处理器排序显示在图3中。

图2 针对Virtex 7 FPGA的推荐加电序列

图2 针对Virtex 7 FPGA的推荐加电序列

其中,VCCINT and VMGTAVCC可同时加电,只要它们在VMGTAVTT之前启动,它们的加电顺序可以互换。

图3 建议用于Zynq 7000系列SoC的加电序列

图3 建议用于Zynq 7000系列SoC的加电序列

对于Xilinx 7/Zynq 7000系列器件来说,这些电源必须具有一个线性上升,并且必须在0.2ms至50ms的周期范围内加电,而对于Xilinx Ultrascale FPGA系列器件来说,这个周期范围在0.2ms到40ms之间。建议断电顺序与加电顺序相反。

电源解决方案

一旦已经估算出合适的电流,并且全部设计注意事项已知的话,电源设计人员可以开始器件选型。有几个选项可供选择,诸如低压降稳压器 (LDO)、开关模式电源 (S

MPS) 和集成模块,它们都具有不同的优缺点。例如,由于其简单性和低输出噪声,LDO是某些较低电流FPGA电源的理想选择。而LDO的缺点在于,它们的效率不高,并且会在较高电流时,通过导通

晶体管大量散热。它们通常适用于那些功率较低的应用,以及那些要求低噪声的应用。

当需要的电流值大于2安培,并且效率更为重要的话,设计人员可以选择开关电源 (SMPS)。这些器件在单相位配置中的效率可以达到90%以上,并且提供高达30A的电流。与LDO相比,它们的设计工作复杂,并且在较轻负载时的效率不太高,不过它们更加灵活,并且在较高电流时的效率较高。

电源模块,比如说LMZ31506电源 (simple switcher),可以将一个

DC/DC转换器、功率金属氧化物场效应晶体管 (

MOSFET)、一个屏蔽

电感器,和无源组件集成在一个薄型四方扁平无引线 (QFN) 封装内。由于全部组件已经集成在一个封装内,并且仅需最少的外部组件,这样可以减少设计时间。

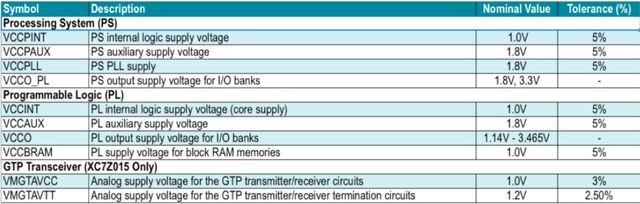

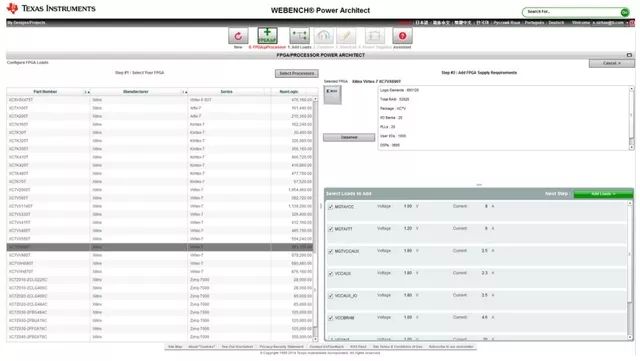

Webench FPGA架构设计工具

Webench FPGA架构设计工具(图4)是一款十分有用的工具,能够帮助电源设计人员在几分钟内构建多个FPGA电源输出。这个工具包含新上市的FPGA的详细电源需求。在这款工具中,你只需选择正在使用的FPGA,并且将电流调整到需要的水平上,而这款工具将自动形成一份综合性的设计报告。

图4 Webench FPGA架构设计工具

全文转自:

https://mp.weixin.qq.com/s/PC2CzdyccQXMqkQlLSj6ow

http://www.sohu.com/a/229649286_288206

图4 Webench FPGA架构设计工具

全文转自:

https://mp.weixin.qq.com/s/PC2CzdyccQXMqkQlLSj6ow

http://www.sohu.com/a/229649286_288206

图1. 通过 LTpowerCAD 工具选择合适的 DC-DC 转换器来为 FPGA 供电。

LTpowerCAD 可用来为各个电压轨提供电源解决方案。它还提供一系列参考设计,以让设计人员快速入门。LTpowerCAD 可以从 ADI公司网站免费下载。☞下载链接:http://www.analog.com/cn/design-center/ltpowercad.html

如何优化实际解决方案以用于FPGA

一旦选择了电源架构和各个电压转换器,就需要选择合适的无源元件来设计电源。做这件事时,需要牢记 FPGA 的特殊负载要求——

图1. 通过 LTpowerCAD 工具选择合适的 DC-DC 转换器来为 FPGA 供电。

LTpowerCAD 可用来为各个电压轨提供电源解决方案。它还提供一系列参考设计,以让设计人员快速入门。LTpowerCAD 可以从 ADI公司网站免费下载。☞下载链接:http://www.analog.com/cn/design-center/ltpowercad.html

如何优化实际解决方案以用于FPGA

一旦选择了电源架构和各个电压转换器,就需要选择合适的无源元件来设计电源。做这件事时,需要牢记 FPGA 的特殊负载要求——

图2. ADP5014 PMIC 集成了对灵活控制上电/关断时序的支持。

图 3 显示了利用此器件实现的时序控制。通过 ADP5014 上的延迟 (DL) 引脚可以轻松调整上电和关断时序的时间延迟。

图2. ADP5014 PMIC 集成了对灵活控制上电/关断时序的支持。

图 3 显示了利用此器件实现的时序控制。通过 ADP5014 上的延迟 (DL) 引脚可以轻松调整上电和关断时序的时间延迟。

图3. 多个FPGA电源电压的启动和关断顺序。

如果使用多个单独的电源,增加时序控制芯片便可实现所需的上电/关断顺序。一个例子是 LTC2924,它既能控制 DC-DC 转换器的使能引脚来打开和关闭电源,也能驱动高端 N 沟道 MOSFET 来将 FPGA 与某个电压轨连接和断开。

电压轨单调上升

除了电压时序之外,启动过程中还可能要求电压单调上升。这意味着电压仅线性上升,如图 4 中的电压 A 所示。此图中的电压 B是电压非单调上升的例子。在启动过程中,当电压上升到一定电平时负载开始拉大电流,就会发生这种情况。防止这种情况的一种办法是延长电源的软启动时间,并选择能够快速提供大量电流的电源转换器。

图3. 多个FPGA电源电压的启动和关断顺序。

如果使用多个单独的电源,增加时序控制芯片便可实现所需的上电/关断顺序。一个例子是 LTC2924,它既能控制 DC-DC 转换器的使能引脚来打开和关闭电源,也能驱动高端 N 沟道 MOSFET 来将 FPGA 与某个电压轨连接和断开。

电压轨单调上升

除了电压时序之外,启动过程中还可能要求电压单调上升。这意味着电压仅线性上升,如图 4 中的电压 A 所示。此图中的电压 B是电压非单调上升的例子。在启动过程中,当电压上升到一定电平时负载开始拉大电流,就会发生这种情况。防止这种情况的一种办法是延长电源的软启动时间,并选择能够快速提供大量电流的电源转换器。

图4. 电压A单调上升,电压B非单调上升。

快速电源瞬变

FPGA 的另一个特点是它会非常迅速地开始抽取大量电流。这会在电源上造成很高的负载瞬变。出于这个原因,许多 FPGA 需要大量的输入电压去耦。陶瓷电容非常靠近地用在器件的 VCORE 和 GND 引脚之间。高达 1 mF 的值非常常见。如此高电容有助于降低对电源提供非常高峰值电流的需求。但是,许多开关稳压器和 LDO 规定了最大输出电容。FPGA 的输入电容要求可能超过电源允 许的最大输出电容。

电源不喜欢非常大的输出电容,原因有两点——

图4. 电压A单调上升,电压B非单调上升。

快速电源瞬变

FPGA 的另一个特点是它会非常迅速地开始抽取大量电流。这会在电源上造成很高的负载瞬变。出于这个原因,许多 FPGA 需要大量的输入电压去耦。陶瓷电容非常靠近地用在器件的 VCORE 和 GND 引脚之间。高达 1 mF 的值非常常见。如此高电容有助于降低对电源提供非常高峰值电流的需求。但是,许多开关稳压器和 LDO 规定了最大输出电容。FPGA 的输入电容要求可能超过电源允 许的最大输出电容。

电源不喜欢非常大的输出电容,原因有两点——

图7. 电源输出电容与FPGA输入电容之间的寄生去耦。

电压精度

FPGA电源的电压精度通常要求非常高。3%的变化容差带是相当常见的。例如,为使0.85 V的Stratix V内核电压轨保持在3%的电压精度窗口内,要求全部容差带仅为25.5 mV。这个小窗口包括负载瞬变后的电压变化以及直流精度。同样,对于此类严格要求,包括LTpowerCAD和LTspice在内的可用电源工具链在电源设计过程中非常重要。

FPGA 输入电容

为了快速提供大电流,FPGA 的输入电容通常选择陶瓷电容。此类电容很适合这种用途,但需要小心选择,使其真实电容值不随直流偏置电压而下降。一些陶瓷电容,尤其是 Y5U 型,当直流偏置电压接近其最大额定直流电压时,其真实电容值会降低到只有标称值的20%

FPGA系统的复杂度越来越高,所以FPGA必须采用适当的电源管理技术, 来设计针对FPGA系统的电源。

FPGA通常需要几个电压供电。根据应用的不同,主输入电源可以采用背板电源、隔离电源、非隔离电源,甚至是电池供电的方式。这些主输入通常产生一个中间DC电压来为FPGA的主电压供电。这些中间电压通常为5V或12V的DC电压。表1和表2中列出了FPGA的某些典型电压轨。

表1 Virtex 7FPGA的电源要求

图7. 电源输出电容与FPGA输入电容之间的寄生去耦。

电压精度

FPGA电源的电压精度通常要求非常高。3%的变化容差带是相当常见的。例如,为使0.85 V的Stratix V内核电压轨保持在3%的电压精度窗口内,要求全部容差带仅为25.5 mV。这个小窗口包括负载瞬变后的电压变化以及直流精度。同样,对于此类严格要求,包括LTpowerCAD和LTspice在内的可用电源工具链在电源设计过程中非常重要。

FPGA 输入电容

为了快速提供大电流,FPGA 的输入电容通常选择陶瓷电容。此类电容很适合这种用途,但需要小心选择,使其真实电容值不随直流偏置电压而下降。一些陶瓷电容,尤其是 Y5U 型,当直流偏置电压接近其最大额定直流电压时,其真实电容值会降低到只有标称值的20%

FPGA系统的复杂度越来越高,所以FPGA必须采用适当的电源管理技术, 来设计针对FPGA系统的电源。

FPGA通常需要几个电压供电。根据应用的不同,主输入电源可以采用背板电源、隔离电源、非隔离电源,甚至是电池供电的方式。这些主输入通常产生一个中间DC电压来为FPGA的主电压供电。这些中间电压通常为5V或12V的DC电压。表1和表2中列出了FPGA的某些典型电压轨。

表1 Virtex 7FPGA的电源要求

表2 Zynq 7000系列片上系统 (SoC) 的电源要求

表2 Zynq 7000系列片上系统 (SoC) 的电源要求

Xilinx功率估算器

为每个电压确定合适的电流是一件比较棘手的工作,原因在于电流的范围可以从几百毫安到60A,甚至更高。如果事先进行规划的话,情况就会完全不同,事先规划可以避免对电源的过度设计和设计的不充份,从而导致必须推倒重来等错误。FPGA厂家提供了精确的FPGA功耗计算工具,可根据客户对FPGA的使用方式来估算出最差情况下的功耗。

图1中显示的Xilinx功率估算器 (XPE),涵盖了数个Xilinx FPGA系列。借助于这款工具,客户可以选择正在使用的部件,并且输入时钟和配置信息,来确定电源需求,并且根据估算值来选择合适的器件。

Xilinx功率估算器

为每个电压确定合适的电流是一件比较棘手的工作,原因在于电流的范围可以从几百毫安到60A,甚至更高。如果事先进行规划的话,情况就会完全不同,事先规划可以避免对电源的过度设计和设计的不充份,从而导致必须推倒重来等错误。FPGA厂家提供了精确的FPGA功耗计算工具,可根据客户对FPGA的使用方式来估算出最差情况下的功耗。

图1中显示的Xilinx功率估算器 (XPE),涵盖了数个Xilinx FPGA系列。借助于这款工具,客户可以选择正在使用的部件,并且输入时钟和配置信息,来确定电源需求,并且根据估算值来选择合适的器件。

图1 Xilinx功率估算器 (XPE)

设计注意事项

注意事项1

在选择一款符合FPGA应用需要的电源时,必须将很多因素考虑在内。成本、尺寸,以及效率,始终是电源设计过程中需要注意的因素。不过,在FPGA应用中,某些电源将会有不同的要求。内核电源通常需要在线路、负载和温度范围内保持更加严格的精度。某些电源,比如说收发器,对于噪声更加敏感,并且需要将它们的输出保持在特定的噪声阀值以下。还需注意的是,某些具有共模电压的电源可组合在一起,并且可以用一个铁氧体磁珠进行隔离,以实现滤波或作为一个负载开关。

注意事项2

当进行符合容限要求方面的设计时,需要将全部的静态和动态运行条件考虑在内。首先,选择一款基准精度小于1%的稳压器,这为客户预留了最大的设计裕量空间来处理负载瞬变等动态运行条件。

注意事项3

在设计高速收发器电源时还需谨慎,因为这些灵敏电源输出的噪声会使性能下降,并且增加抖动。低压降稳压器 (LDO) 是这些电源轨的理想选择。不过,当需要更高电流时,只要输出纹波的典型值在10kHz至80MHz频率范围内保持在10mVpk-pk以下,就可以使用开关电源。专用FPGA数据表将包含与收发器需求相关的详细技术规格。

注意事项4

电源排序是FPGA电源设计时的另外一个重要方面。由于FPGA系统中需要多个电源供电,如图推荐的电源顺序在启动时汲取最小电流,这反过来防止了对器件的损坏。图2中显示的是针对Virtex 7系列FPGA上的逻辑电路和收发器电源的建议加电电源序列。针对Zynq 7000系列SoC的处理器排序显示在图3中。

图1 Xilinx功率估算器 (XPE)

设计注意事项

注意事项1

在选择一款符合FPGA应用需要的电源时,必须将很多因素考虑在内。成本、尺寸,以及效率,始终是电源设计过程中需要注意的因素。不过,在FPGA应用中,某些电源将会有不同的要求。内核电源通常需要在线路、负载和温度范围内保持更加严格的精度。某些电源,比如说收发器,对于噪声更加敏感,并且需要将它们的输出保持在特定的噪声阀值以下。还需注意的是,某些具有共模电压的电源可组合在一起,并且可以用一个铁氧体磁珠进行隔离,以实现滤波或作为一个负载开关。

注意事项2

当进行符合容限要求方面的设计时,需要将全部的静态和动态运行条件考虑在内。首先,选择一款基准精度小于1%的稳压器,这为客户预留了最大的设计裕量空间来处理负载瞬变等动态运行条件。

注意事项3

在设计高速收发器电源时还需谨慎,因为这些灵敏电源输出的噪声会使性能下降,并且增加抖动。低压降稳压器 (LDO) 是这些电源轨的理想选择。不过,当需要更高电流时,只要输出纹波的典型值在10kHz至80MHz频率范围内保持在10mVpk-pk以下,就可以使用开关电源。专用FPGA数据表将包含与收发器需求相关的详细技术规格。

注意事项4

电源排序是FPGA电源设计时的另外一个重要方面。由于FPGA系统中需要多个电源供电,如图推荐的电源顺序在启动时汲取最小电流,这反过来防止了对器件的损坏。图2中显示的是针对Virtex 7系列FPGA上的逻辑电路和收发器电源的建议加电电源序列。针对Zynq 7000系列SoC的处理器排序显示在图3中。

图2 针对Virtex 7 FPGA的推荐加电序列

其中,VCCINT and VMGTAVCC可同时加电,只要它们在VMGTAVTT之前启动,它们的加电顺序可以互换。

图2 针对Virtex 7 FPGA的推荐加电序列

其中,VCCINT and VMGTAVCC可同时加电,只要它们在VMGTAVTT之前启动,它们的加电顺序可以互换。

图3 建议用于Zynq 7000系列SoC的加电序列

对于Xilinx 7/Zynq 7000系列器件来说,这些电源必须具有一个线性上升,并且必须在0.2ms至50ms的周期范围内加电,而对于Xilinx Ultrascale FPGA系列器件来说,这个周期范围在0.2ms到40ms之间。建议断电顺序与加电顺序相反。

电源解决方案

一旦已经估算出合适的电流,并且全部设计注意事项已知的话,电源设计人员可以开始器件选型。有几个选项可供选择,诸如低压降稳压器 (LDO)、开关模式电源 (SMPS) 和集成模块,它们都具有不同的优缺点。例如,由于其简单性和低输出噪声,LDO是某些较低电流FPGA电源的理想选择。而LDO的缺点在于,它们的效率不高,并且会在较高电流时,通过导通晶体管大量散热。它们通常适用于那些功率较低的应用,以及那些要求低噪声的应用。

当需要的电流值大于2安培,并且效率更为重要的话,设计人员可以选择开关电源 (SMPS)。这些器件在单相位配置中的效率可以达到90%以上,并且提供高达30A的电流。与LDO相比,它们的设计工作复杂,并且在较轻负载时的效率不太高,不过它们更加灵活,并且在较高电流时的效率较高。

电源模块,比如说LMZ31506电源 (simple switcher),可以将一个DC/DC转换器、功率金属氧化物场效应晶体管 (MOSFET)、一个屏蔽电感器,和无源组件集成在一个薄型四方扁平无引线 (QFN) 封装内。由于全部组件已经集成在一个封装内,并且仅需最少的外部组件,这样可以减少设计时间。

Webench FPGA架构设计工具

Webench FPGA架构设计工具(图4)是一款十分有用的工具,能够帮助电源设计人员在几分钟内构建多个FPGA电源输出。这个工具包含新上市的FPGA的详细电源需求。在这款工具中,你只需选择正在使用的FPGA,并且将电流调整到需要的水平上,而这款工具将自动形成一份综合性的设计报告。

图3 建议用于Zynq 7000系列SoC的加电序列

对于Xilinx 7/Zynq 7000系列器件来说,这些电源必须具有一个线性上升,并且必须在0.2ms至50ms的周期范围内加电,而对于Xilinx Ultrascale FPGA系列器件来说,这个周期范围在0.2ms到40ms之间。建议断电顺序与加电顺序相反。

电源解决方案

一旦已经估算出合适的电流,并且全部设计注意事项已知的话,电源设计人员可以开始器件选型。有几个选项可供选择,诸如低压降稳压器 (LDO)、开关模式电源 (SMPS) 和集成模块,它们都具有不同的优缺点。例如,由于其简单性和低输出噪声,LDO是某些较低电流FPGA电源的理想选择。而LDO的缺点在于,它们的效率不高,并且会在较高电流时,通过导通晶体管大量散热。它们通常适用于那些功率较低的应用,以及那些要求低噪声的应用。

当需要的电流值大于2安培,并且效率更为重要的话,设计人员可以选择开关电源 (SMPS)。这些器件在单相位配置中的效率可以达到90%以上,并且提供高达30A的电流。与LDO相比,它们的设计工作复杂,并且在较轻负载时的效率不太高,不过它们更加灵活,并且在较高电流时的效率较高。

电源模块,比如说LMZ31506电源 (simple switcher),可以将一个DC/DC转换器、功率金属氧化物场效应晶体管 (MOSFET)、一个屏蔽电感器,和无源组件集成在一个薄型四方扁平无引线 (QFN) 封装内。由于全部组件已经集成在一个封装内,并且仅需最少的外部组件,这样可以减少设计时间。

Webench FPGA架构设计工具

Webench FPGA架构设计工具(图4)是一款十分有用的工具,能够帮助电源设计人员在几分钟内构建多个FPGA电源输出。这个工具包含新上市的FPGA的详细电源需求。在这款工具中,你只需选择正在使用的FPGA,并且将电流调整到需要的水平上,而这款工具将自动形成一份综合性的设计报告。

图4 Webench FPGA架构设计工具

全文转自:

https://mp.weixin.qq.com/s/PC2CzdyccQXMqkQlLSj6ow

http://www.sohu.com/a/229649286_288206

图4 Webench FPGA架构设计工具

全文转自:

https://mp.weixin.qq.com/s/PC2CzdyccQXMqkQlLSj6ow

http://www.sohu.com/a/229649286_288206