data/attach/1907/xtgp6iwy6kwy6ixwr9zc8b5rfgfj6u6q.jpg

1.电源纹波产生的原因

首先说明一下芯片电源引脚产生纹波的原因。如下是一个典型的门电路输出级,当输出为高时,Q3导通,Q4截止;相反,当输出为低时,Q3截止,Q4导通,

这两种状态都在电源和地之间形成了高阻态,限制了电源的电流。

![]()

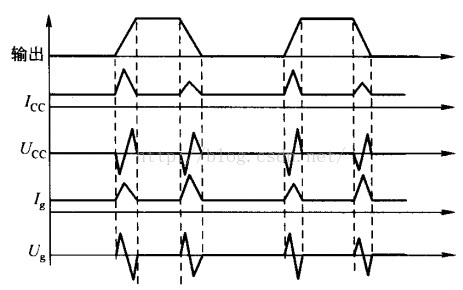

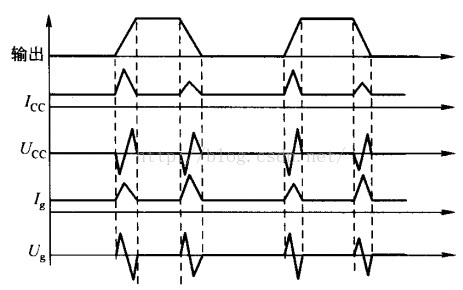

图1 典型门电路输出级 但是,当状态发生变化时,会有一段时间Q3 Q4同时导通,这时在电源与地之间形成短暂的低阻抗,产生30- 100mA的尖峰电流。当门输出有低变高时,电源不仅 提供短路的电流,还要给寄生电容充电,使这个电流的峰值更大。由于电源线和地线总是有不同程度的电感,当电流突变时,会在电源线和地线上产生压降,这就是电源线和地线上的噪声;尤其对于周期信号,这样的噪声更明显,如下图。

图2 电源线和地线上的噪声 去耦电源是去除噪声的一种方法。当所有的信号脚工作于最大容量负载下同时开关时,去耦电容还提供给元件在时钟和数据变化期间正常工作所需的动态电压和电流。 去耦是通过在信号和电源平面之间提供一个低阻抗的电源来实现的。 2.电容的阻抗与谐振频率与去耦 1)电容去耦原理:电容在频率升高到谐振点之前,随着频率升高,阻抗降低,这就给高频噪声提供了一个低阻抗的泄放途径,剩下的低频能量就不足以发射出去了。 2)常用电容: 0.1uF和0.01uF电容是当今高速电路中最常用的去耦电容。一般来说SMT的电容的自谐振点不会超过500MhZ,而0.01uF电容的自谐振点在50-150MhZ之间;而且在实际使用中引线电感及过孔的存在会进一步降低谐振点,这使得再小的电容,实际的去耦频率也不会超过300MhZ。 3)电容并联:相同容值的电容并联,引线电感和寄生电感会因为并联而减小,使得整体阻抗减小,这样有利于提高去耦频率,同时,电容并联也能提供更多的能量。 4)电源层与地层构成电容:在多层PCB中,依赖电源层和地层形成的板间电容,有着较低的ESL,这也是高频去耦的重要手段。 5)去耦电容的选择:去耦电容不要什么都用0.1uF,要考虑去耦器件的工作频率和谐波。工作主频20Mhz以下的,用0.1uF,20M hz以上的用0.01uF,甚至更小的,并与0.1uF并联使用。(若添加磁珠,电容靠近IC,磁珠远离IC)

图1 典型门电路输出级 但是,当状态发生变化时,会有一段时间Q3 Q4同时导通,这时在电源与地之间形成短暂的低阻抗,产生30- 100mA的尖峰电流。当门输出有低变高时,电源不仅 提供短路的电流,还要给寄生电容充电,使这个电流的峰值更大。由于电源线和地线总是有不同程度的电感,当电流突变时,会在电源线和地线上产生压降,这就是电源线和地线上的噪声;尤其对于周期信号,这样的噪声更明显,如下图。

图2 电源线和地线上的噪声 去耦电源是去除噪声的一种方法。当所有的信号脚工作于最大容量负载下同时开关时,去耦电容还提供给元件在时钟和数据变化期间正常工作所需的动态电压和电流。 去耦是通过在信号和电源平面之间提供一个低阻抗的电源来实现的。 2.电容的阻抗与谐振频率与去耦 1)电容去耦原理:电容在频率升高到谐振点之前,随着频率升高,阻抗降低,这就给高频噪声提供了一个低阻抗的泄放途径,剩下的低频能量就不足以发射出去了。 2)常用电容: 0.1uF和0.01uF电容是当今高速电路中最常用的去耦电容。一般来说SMT的电容的自谐振点不会超过500MhZ,而0.01uF电容的自谐振点在50-150MhZ之间;而且在实际使用中引线电感及过孔的存在会进一步降低谐振点,这使得再小的电容,实际的去耦频率也不会超过300MhZ。 3)电容并联:相同容值的电容并联,引线电感和寄生电感会因为并联而减小,使得整体阻抗减小,这样有利于提高去耦频率,同时,电容并联也能提供更多的能量。 4)电源层与地层构成电容:在多层PCB中,依赖电源层和地层形成的板间电容,有着较低的ESL,这也是高频去耦的重要手段。 5)去耦电容的选择:去耦电容不要什么都用0.1uF,要考虑去耦器件的工作频率和谐波。工作主频20Mhz以下的,用0.1uF,20M hz以上的用0.01uF,甚至更小的,并与0.1uF并联使用。(若添加磁珠,电容靠近IC,磁珠远离IC)