--续前文

作者:Hello,Panda

Zynq UltraScale+ MPSoC架构

Xilinx新一代Zynq针对控制、图像和网络应用推出了差异化的产品系,这在Xilinx早期的宣传和现在已经发布的文档里已经说得很清楚了。她的产品系如图2所示。

图2 产品表

从图2看到,这个系列的Zynq算是8核(或9核)异构产品:四核的ARM-CortexA53 CPU、双核的Cortex-R5 RPU、Mali-400 GPU(一个Geometry核,两个像素核)、PL逻辑以及视频编解码器Codec核。

在表2中,ZU2E、ZU3E为针对控制类应用,逻辑和Block RAM资源较少,没有Video Codec和高速收发器。ZU4E、ZU2E和ZU7E针对视频类应用,有内部的UltraRAM资源、Video Codec和GTH高速收发器。其他型号针对网络应用,除了Video Code没有外,其它高大上的东西都有,比如更高速的收发器GTY,还有150G Interlaken和100G Ethernet MAC/PCS/RS-FEC等。

熊猫君是做图像的,下面的描述都是针对图像版的Zynq UltraScale+而言的。

因为PS部分的资源是固定的,大家都一样,在后面一起说就行。PL部分因为有这三个东西,将使设计如虎添翼:

a)大量的Block RAM和Ultra RAM资源,小20Mb的内部RAM资源,对分块处理图像,那应该会带来不少的便捷;

b)Video Code:这个东西是集成在PL侧的硬核,有了它,图像压缩和解压缩都不用愁了;

c)GTH:PL端集成的GTH收发器,对SDI、DP等图像接口接入那是十分的方便,当然也可以做PCIe咯。

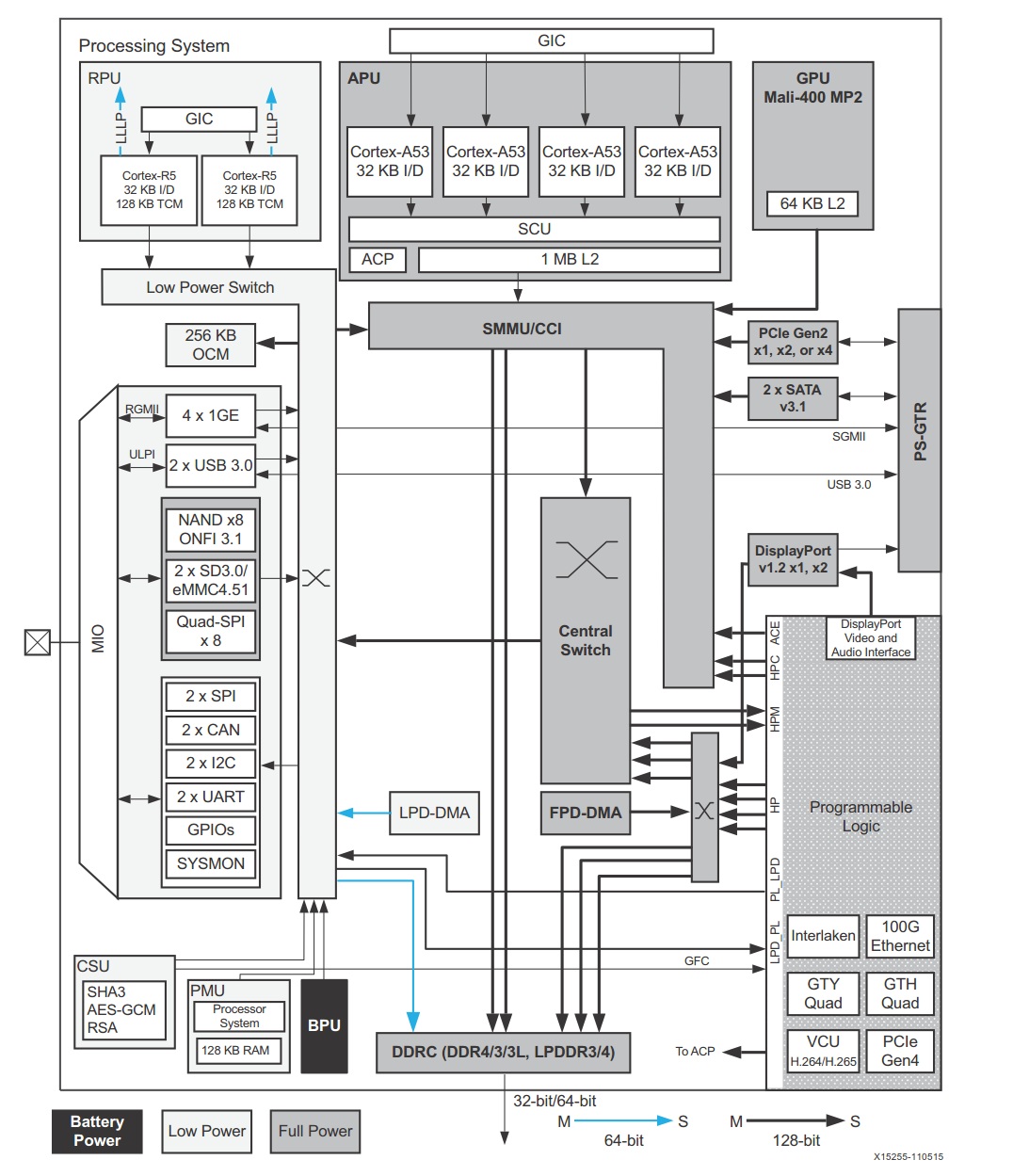

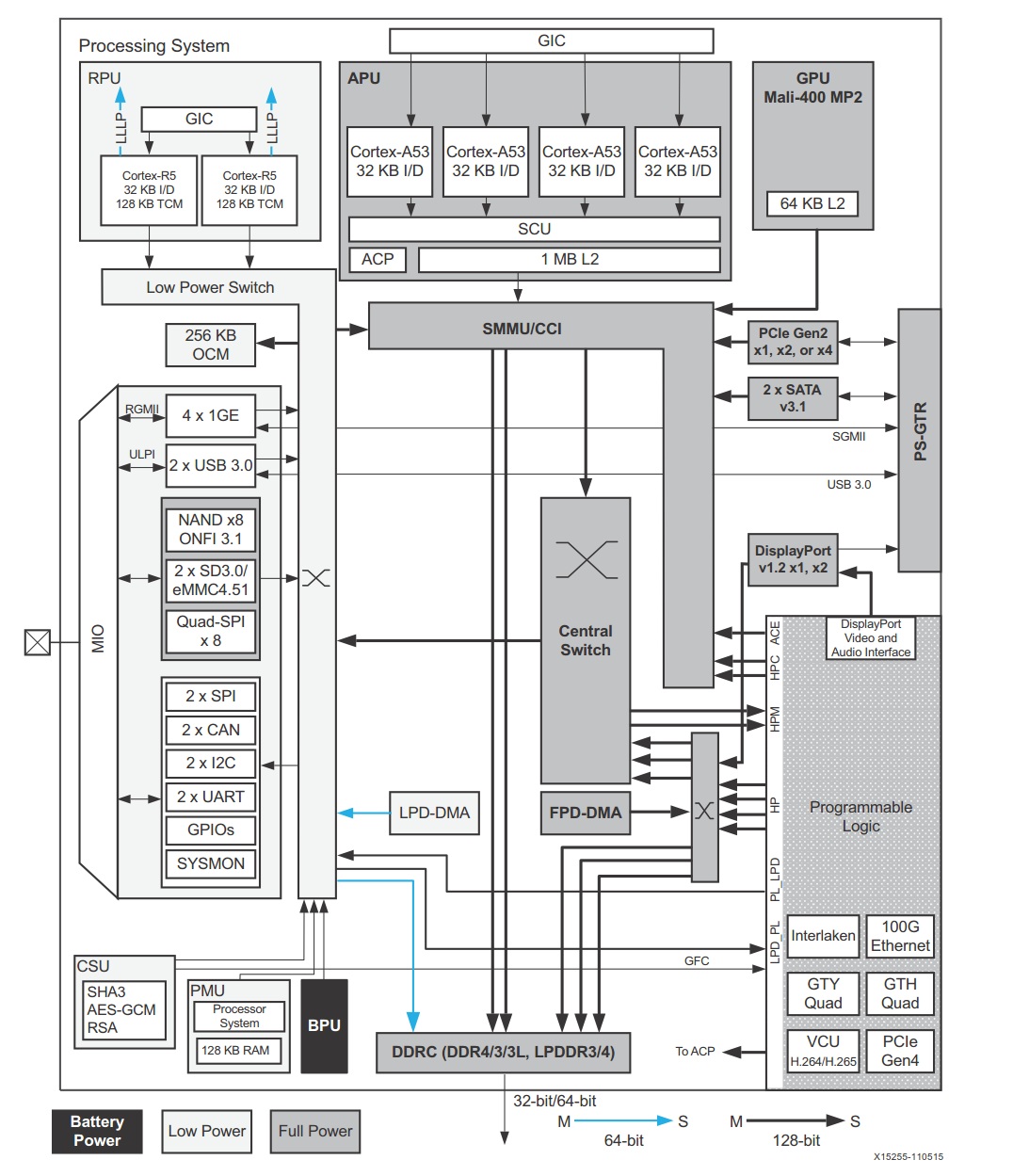

不多说了,熊猫君从Xilinx官方文档UG1085上截一个图来表示这个高大上通用SoC的系统级架构,也就是下面的图3啦。

图2 产品表

从图2看到,这个系列的Zynq算是8核(或9核)异构产品:四核的ARM-CortexA53 CPU、双核的Cortex-R5 RPU、Mali-400 GPU(一个Geometry核,两个像素核)、PL逻辑以及视频编解码器Codec核。

在表2中,ZU2E、ZU3E为针对控制类应用,逻辑和Block RAM资源较少,没有Video Codec和高速收发器。ZU4E、ZU2E和ZU7E针对视频类应用,有内部的UltraRAM资源、Video Codec和GTH高速收发器。其他型号针对网络应用,除了Video Code没有外,其它高大上的东西都有,比如更高速的收发器GTY,还有150G Interlaken和100G Ethernet MAC/PCS/RS-FEC等。

熊猫君是做图像的,下面的描述都是针对图像版的Zynq UltraScale+而言的。

因为PS部分的资源是固定的,大家都一样,在后面一起说就行。PL部分因为有这三个东西,将使设计如虎添翼:

a)大量的Block RAM和Ultra RAM资源,小20Mb的内部RAM资源,对分块处理图像,那应该会带来不少的便捷;

b)Video Code:这个东西是集成在PL侧的硬核,有了它,图像压缩和解压缩都不用愁了;

c)GTH:PL端集成的GTH收发器,对SDI、DP等图像接口接入那是十分的方便,当然也可以做PCIe咯。

不多说了,熊猫君从Xilinx官方文档UG1085上截一个图来表示这个高大上通用SoC的系统级架构,也就是下面的图3啦。

图3 Zynq UltraScale+ MPSoC系统架构图

当初刚看到这个架构的时候,可高兴坏熊猫宝宝了,一连吃了好几框竹笋才勉强压了惊。冷静之余,还让熊猫君慢慢道来。

什么16nm级工艺的先进性啊什么什么各种先进技术的应用之类的咱不聊,那是Xilinx的事儿,咱就重点闲掰扯一下这货怎么用。目前熊猫君打算就以下几个方面入手:

(1)关于硬件设计的:

a) 电源系统和上电时序;

b) 启动加载;

c) IO资源;

d) 系统整体性能汇总(根据Xilinx提供的官方资料整理)。

(2)内部互联结构

可不要小看了这一部分,这是SoC的核心内容,所以单独拿出来。

(3)关于软件设计的

好吧,熊猫君也没有拿到试用版的开发套件,只能根据自己的认识+官方文档聊聊了。

Part1:电源系统

相比于Zynq-7000,这个电源系统要复杂一些,咱抛开低功耗版本(-L)的不谈,就谈正常情况,PS端也把电源域分成了普通电源域和低功耗电源域,然后PS端的GTR也是单独供电的,还有还有,这个GTR的电压竟然和PL端的GTH完全不同。图4是Zynq-7000和Zynq UltraScale+ MPSoC电源系统的比较。

图3 Zynq UltraScale+ MPSoC系统架构图

当初刚看到这个架构的时候,可高兴坏熊猫宝宝了,一连吃了好几框竹笋才勉强压了惊。冷静之余,还让熊猫君慢慢道来。

什么16nm级工艺的先进性啊什么什么各种先进技术的应用之类的咱不聊,那是Xilinx的事儿,咱就重点闲掰扯一下这货怎么用。目前熊猫君打算就以下几个方面入手:

(1)关于硬件设计的:

a) 电源系统和上电时序;

b) 启动加载;

c) IO资源;

d) 系统整体性能汇总(根据Xilinx提供的官方资料整理)。

(2)内部互联结构

可不要小看了这一部分,这是SoC的核心内容,所以单独拿出来。

(3)关于软件设计的

好吧,熊猫君也没有拿到试用版的开发套件,只能根据自己的认识+官方文档聊聊了。

Part1:电源系统

相比于Zynq-7000,这个电源系统要复杂一些,咱抛开低功耗版本(-L)的不谈,就谈正常情况,PS端也把电源域分成了普通电源域和低功耗电源域,然后PS端的GTR也是单独供电的,还有还有,这个GTR的电压竟然和PL端的GTH完全不同。图4是Zynq-7000和Zynq UltraScale+ MPSoC电源系统的比较。

图 4 电源系统比较

典型的是,内核电压由1.0V降至0.85V,PS端多了专门的GTR电压。更低的核电压,更多的核消耗和更高的时钟频率意味着更大的电流,预估PL和PS的内核光静态电流就在3A左右。同时新的Zynq UltraScale+ PS端有两个电源域,分别是全功耗电源域和低功耗电源域。二者的PL和PS间都是独立的。

关于上电顺序,Zynq-7000的要求是:

a) PS : 先同时上VCCPINT、VCCPAUX和VCCPLL,再上VCCO(MIO、DDR),但VCCO上电延时相对于VCCPAUX有一个必须遵守的最大延迟时间。

b) PL : 先后依次是VCCINT、 VCCBRAM、 VCCAUX和 VCCO,VCCO上电延时相对于VCCAUX有一个必须遵守的最大延迟时间。

但是Zynq UltraScale+ MPSoC有不同的要求:

a) 在PS系统里,必须保证低功耗电源域先上电,待上电完成后再给全功耗系统上电。

b) 在低功耗电源域内的上电顺序是:VCCPINTLP先上电,然后VCCPAUX、VCCPADC、和VCCPLL没有特别要求,最后给VCCOPIO上电。

c) 在全功耗电源域内先给VCCPINTFP(VCCPINTFP_DDR)上电,然后VMGTRAVCC、 VCCPLL和 VCCDDRPLL以任何顺序上电,最后是给MGTRAVTT和VCCODDR上电。

d) PL 上电完全独立,依次是VCCINT、VCCINT_IO/VCCBRAM、VCCAUX/VCCAUX_IO和 VCCO。

对Xilinx UltraScale MPSoC感兴趣的同行可加入讨论群300148644进行进一步技术交流。

图 4 电源系统比较

典型的是,内核电压由1.0V降至0.85V,PS端多了专门的GTR电压。更低的核电压,更多的核消耗和更高的时钟频率意味着更大的电流,预估PL和PS的内核光静态电流就在3A左右。同时新的Zynq UltraScale+ PS端有两个电源域,分别是全功耗电源域和低功耗电源域。二者的PL和PS间都是独立的。

关于上电顺序,Zynq-7000的要求是:

a) PS : 先同时上VCCPINT、VCCPAUX和VCCPLL,再上VCCO(MIO、DDR),但VCCO上电延时相对于VCCPAUX有一个必须遵守的最大延迟时间。

b) PL : 先后依次是VCCINT、 VCCBRAM、 VCCAUX和 VCCO,VCCO上电延时相对于VCCAUX有一个必须遵守的最大延迟时间。

但是Zynq UltraScale+ MPSoC有不同的要求:

a) 在PS系统里,必须保证低功耗电源域先上电,待上电完成后再给全功耗系统上电。

b) 在低功耗电源域内的上电顺序是:VCCPINTLP先上电,然后VCCPAUX、VCCPADC、和VCCPLL没有特别要求,最后给VCCOPIO上电。

c) 在全功耗电源域内先给VCCPINTFP(VCCPINTFP_DDR)上电,然后VMGTRAVCC、 VCCPLL和 VCCDDRPLL以任何顺序上电,最后是给MGTRAVTT和VCCODDR上电。

d) PL 上电完全独立,依次是VCCINT、VCCINT_IO/VCCBRAM、VCCAUX/VCCAUX_IO和 VCCO。

对Xilinx UltraScale MPSoC感兴趣的同行可加入讨论群300148644进行进一步技术交流。

图2 产品表

从图2看到,这个系列的Zynq算是8核(或9核)异构产品:四核的ARM-CortexA53 CPU、双核的Cortex-R5 RPU、Mali-400 GPU(一个Geometry核,两个像素核)、PL逻辑以及视频编解码器Codec核。

在表2中,ZU2E、ZU3E为针对控制类应用,逻辑和Block RAM资源较少,没有Video Codec和高速收发器。ZU4E、ZU2E和ZU7E针对视频类应用,有内部的UltraRAM资源、Video Codec和GTH高速收发器。其他型号针对网络应用,除了Video Code没有外,其它高大上的东西都有,比如更高速的收发器GTY,还有150G Interlaken和100G Ethernet MAC/PCS/RS-FEC等。

熊猫君是做图像的,下面的描述都是针对图像版的Zynq UltraScale+而言的。

因为PS部分的资源是固定的,大家都一样,在后面一起说就行。PL部分因为有这三个东西,将使设计如虎添翼:

a)大量的Block RAM和Ultra RAM资源,小20Mb的内部RAM资源,对分块处理图像,那应该会带来不少的便捷;

b)Video Code:这个东西是集成在PL侧的硬核,有了它,图像压缩和解压缩都不用愁了;

c)GTH:PL端集成的GTH收发器,对SDI、DP等图像接口接入那是十分的方便,当然也可以做PCIe咯。

不多说了,熊猫君从Xilinx官方文档UG1085上截一个图来表示这个高大上通用SoC的系统级架构,也就是下面的图3啦。

图2 产品表

从图2看到,这个系列的Zynq算是8核(或9核)异构产品:四核的ARM-CortexA53 CPU、双核的Cortex-R5 RPU、Mali-400 GPU(一个Geometry核,两个像素核)、PL逻辑以及视频编解码器Codec核。

在表2中,ZU2E、ZU3E为针对控制类应用,逻辑和Block RAM资源较少,没有Video Codec和高速收发器。ZU4E、ZU2E和ZU7E针对视频类应用,有内部的UltraRAM资源、Video Codec和GTH高速收发器。其他型号针对网络应用,除了Video Code没有外,其它高大上的东西都有,比如更高速的收发器GTY,还有150G Interlaken和100G Ethernet MAC/PCS/RS-FEC等。

熊猫君是做图像的,下面的描述都是针对图像版的Zynq UltraScale+而言的。

因为PS部分的资源是固定的,大家都一样,在后面一起说就行。PL部分因为有这三个东西,将使设计如虎添翼:

a)大量的Block RAM和Ultra RAM资源,小20Mb的内部RAM资源,对分块处理图像,那应该会带来不少的便捷;

b)Video Code:这个东西是集成在PL侧的硬核,有了它,图像压缩和解压缩都不用愁了;

c)GTH:PL端集成的GTH收发器,对SDI、DP等图像接口接入那是十分的方便,当然也可以做PCIe咯。

不多说了,熊猫君从Xilinx官方文档UG1085上截一个图来表示这个高大上通用SoC的系统级架构,也就是下面的图3啦。

图3 Zynq UltraScale+ MPSoC系统架构图

当初刚看到这个架构的时候,可高兴坏熊猫宝宝了,一连吃了好几框竹笋才勉强压了惊。冷静之余,还让熊猫君慢慢道来。

什么16nm级工艺的先进性啊什么什么各种先进技术的应用之类的咱不聊,那是Xilinx的事儿,咱就重点闲掰扯一下这货怎么用。目前熊猫君打算就以下几个方面入手:

(1)关于硬件设计的:

a) 电源系统和上电时序;

b) 启动加载;

c) IO资源;

d) 系统整体性能汇总(根据Xilinx提供的官方资料整理)。

(2)内部互联结构

可不要小看了这一部分,这是SoC的核心内容,所以单独拿出来。

(3)关于软件设计的

好吧,熊猫君也没有拿到试用版的开发套件,只能根据自己的认识+官方文档聊聊了。

Part1:电源系统

相比于Zynq-7000,这个电源系统要复杂一些,咱抛开低功耗版本(-L)的不谈,就谈正常情况,PS端也把电源域分成了普通电源域和低功耗电源域,然后PS端的GTR也是单独供电的,还有还有,这个GTR的电压竟然和PL端的GTH完全不同。图4是Zynq-7000和Zynq UltraScale+ MPSoC电源系统的比较。

图3 Zynq UltraScale+ MPSoC系统架构图

当初刚看到这个架构的时候,可高兴坏熊猫宝宝了,一连吃了好几框竹笋才勉强压了惊。冷静之余,还让熊猫君慢慢道来。

什么16nm级工艺的先进性啊什么什么各种先进技术的应用之类的咱不聊,那是Xilinx的事儿,咱就重点闲掰扯一下这货怎么用。目前熊猫君打算就以下几个方面入手:

(1)关于硬件设计的:

a) 电源系统和上电时序;

b) 启动加载;

c) IO资源;

d) 系统整体性能汇总(根据Xilinx提供的官方资料整理)。

(2)内部互联结构

可不要小看了这一部分,这是SoC的核心内容,所以单独拿出来。

(3)关于软件设计的

好吧,熊猫君也没有拿到试用版的开发套件,只能根据自己的认识+官方文档聊聊了。

Part1:电源系统

相比于Zynq-7000,这个电源系统要复杂一些,咱抛开低功耗版本(-L)的不谈,就谈正常情况,PS端也把电源域分成了普通电源域和低功耗电源域,然后PS端的GTR也是单独供电的,还有还有,这个GTR的电压竟然和PL端的GTH完全不同。图4是Zynq-7000和Zynq UltraScale+ MPSoC电源系统的比较。

图 4 电源系统比较

典型的是,内核电压由1.0V降至0.85V,PS端多了专门的GTR电压。更低的核电压,更多的核消耗和更高的时钟频率意味着更大的电流,预估PL和PS的内核光静态电流就在3A左右。同时新的Zynq UltraScale+ PS端有两个电源域,分别是全功耗电源域和低功耗电源域。二者的PL和PS间都是独立的。

关于上电顺序,Zynq-7000的要求是:

a) PS : 先同时上VCCPINT、VCCPAUX和VCCPLL,再上VCCO(MIO、DDR),但VCCO上电延时相对于VCCPAUX有一个必须遵守的最大延迟时间。

b) PL : 先后依次是VCCINT、 VCCBRAM、 VCCAUX和 VCCO,VCCO上电延时相对于VCCAUX有一个必须遵守的最大延迟时间。

但是Zynq UltraScale+ MPSoC有不同的要求:

a) 在PS系统里,必须保证低功耗电源域先上电,待上电完成后再给全功耗系统上电。

b) 在低功耗电源域内的上电顺序是:VCCPINTLP先上电,然后VCCPAUX、VCCPADC、和VCCPLL没有特别要求,最后给VCCOPIO上电。

c) 在全功耗电源域内先给VCCPINTFP(VCCPINTFP_DDR)上电,然后VMGTRAVCC、 VCCPLL和 VCCDDRPLL以任何顺序上电,最后是给MGTRAVTT和VCCODDR上电。

d) PL 上电完全独立,依次是VCCINT、VCCINT_IO/VCCBRAM、VCCAUX/VCCAUX_IO和 VCCO。

对Xilinx UltraScale MPSoC感兴趣的同行可加入讨论群300148644进行进一步技术交流。

图 4 电源系统比较

典型的是,内核电压由1.0V降至0.85V,PS端多了专门的GTR电压。更低的核电压,更多的核消耗和更高的时钟频率意味着更大的电流,预估PL和PS的内核光静态电流就在3A左右。同时新的Zynq UltraScale+ PS端有两个电源域,分别是全功耗电源域和低功耗电源域。二者的PL和PS间都是独立的。

关于上电顺序,Zynq-7000的要求是:

a) PS : 先同时上VCCPINT、VCCPAUX和VCCPLL,再上VCCO(MIO、DDR),但VCCO上电延时相对于VCCPAUX有一个必须遵守的最大延迟时间。

b) PL : 先后依次是VCCINT、 VCCBRAM、 VCCAUX和 VCCO,VCCO上电延时相对于VCCAUX有一个必须遵守的最大延迟时间。

但是Zynq UltraScale+ MPSoC有不同的要求:

a) 在PS系统里,必须保证低功耗电源域先上电,待上电完成后再给全功耗系统上电。

b) 在低功耗电源域内的上电顺序是:VCCPINTLP先上电,然后VCCPAUX、VCCPADC、和VCCPLL没有特别要求,最后给VCCOPIO上电。

c) 在全功耗电源域内先给VCCPINTFP(VCCPINTFP_DDR)上电,然后VMGTRAVCC、 VCCPLL和 VCCDDRPLL以任何顺序上电,最后是给MGTRAVTT和VCCODDR上电。

d) PL 上电完全独立,依次是VCCINT、VCCINT_IO/VCCBRAM、VCCAUX/VCCAUX_IO和 VCCO。

对Xilinx UltraScale MPSoC感兴趣的同行可加入讨论群300148644进行进一步技术交流。