3. 电源

3.1 电压和电源域

每个模块都属于核逻辑电压域(CoreLogic Voltage)、内存电压域(Memory Voltage Domain)和电源域(Power Domain)。

3.1.1 核逻辑电压域

器件包含4个核逻辑电压域,这些域定义一组模块共享同一个供电电压为其内核逻辑供电。每个核逻辑电压域由一个专用的电源供电,表7-2描述了内核逻辑电压域和它们相关的供电脚。 注意:每个内核逻辑电压域必须始终供电,而不管内核逻辑电源域状态如何。

3.1.2 内存电压域

每个模块里的SRAM被分配为4个内存电压域之一,每个内存电压域的电压由内部LDO独立控制,由VDDA_1P8脚提供电源。 LDO的输出电压可以通过控制模块中的RAMLDO_CTRLx寄存器来编程,内存电压域电压必须基于该域的内核逻辑电压域电压来编程,也就是说对应于ARM_M电压域的内核逻辑电压域ARM_C等等,表7-3显示了内存电压域电压要求:

3.1.3 电源域

器件包括6个电源域,它为相关模块的内核逻辑和SRAM供电,除了ALWAYSON域,其它电源域都有个内部开关,从而可以关闭该域的供电。 在复位后的缺省状态,所有的电源开关是OFF状态,软件可以通过控制模块单独对它们进行ON/OFF。 注意:当域的电源被OFF掉后,该电源域中的所有模块均不能使用。3.1.4 动态电压频率调整

每个内核逻辑电压域能独立运行在不同的OPPs(Operating Performance Points运行性能点),对于一个特定的内核逻辑电压域,OPP定义如下:(1)最高运行频率,(2)相关的供电电压范围。作为性能和功耗的交易,具有较低的最大频率OPPs同时其电源电压也较低,从而降低功耗。 一个域的OPP可以实时改变而无需复位,这个特征称为动态电压频率调整(DVFS),表7-4包含一个电压范围和最高运行频率的列表。

注意: (1) 在改变DDR频率之前,所有DDR存取必须暂停。 (2) 仅DM816x SR3.0器件支持750MHz的DSP频率,更多信息见器件数据手册 虽然每个逻辑电压域的OPP是独立可选择的,但是并不是所有的OPPs组合都支持,表7-5给出了这些支持的组合。

注意: (1) ”x”表示支持的组合 (2) 在CVDD和任何其它CVDD_x电压域之间的最大电压差必须小于150mV

3.2 内存电源管理

为了减少SRAM的泄漏,许多SRAM模块能从ACTIVE切换到SHUTDOWN模式,当SRAM进入到SHUTDOWN模式时,电源会自动关闭,SRAM内的所有数据消失。 所有处于可ON/OFF电源域的SRAM(除了ALWAYS_ON域外),每当相关的电源域进入OFF态时,它能自动进入SHUTDOWN状态;而当相关的电源域进入ON态时,它能自动返回ACTIVE状态。 另外,下面的处于ALWAYS_ON电源域的SRAM,也能通过对控制模块里的x_MEM_PWRDN寄存器编程,单独进入SHUTDOWN态:- 媒体控制器SRAM

- OCMC SRAM

3.3 SERDES_CLKP和SERDES_CLKIN LDO

SERDES_CLKP和SERDES_CLKN输入缓冲能通过内部LDO供电,这是通过对控制模块里的REFCLK_LJCBLDO_CTRL寄存器编程来实现的。3.4 双电压I/Os

器件支持某些IOs为双电压,这些I/Os分成下面几组:每组有自己的专门电源脚:DVDD、DVDD_GPMC、DVDD_C和DVDD_SD。这些电源脚可以用3.3V或1.8V供电。 关于电源脚和电源组的映射见datasheet 另外,每个DDR接口的I/O电压是在1.5V和1.8V之间独立可选择的,以支持不同的DDR类型,每个DDR接口的I/O供电时分开的隔离的,这在每个接口上可以使用不同类型的内存。3.5 I/O掉电模式

下面的PHYs可以工作于节电模式:- 视频DAC

- DDR

- USB

- HDMI

- PCIE

- SATA

3.6 待机模式

器件支持低功耗待机模式,如下面描述: 待机模式:- 所有可切换电源域都是处于OFF状态

- ARM Cortex-A8以最低运行频率执行IDLE循环

- 所有应用不需要的功能模块时钟停运

3.7 供电顺序

器件电源按顺序分成4组: 1) 所有的CVDD电源(CVDD、CVDD_x) 2) 所有的1.5-/1.8-V DVDD_DDR[x]电源(对DDR3是1.5V,DDR2是1.8V) 3) 所有的1.8-V电源(DVDD_x,DVDD_M、DVDDA_x_1P8、VDDA_1P8) 4) 所有3.3V电源(DVDD、DVDD_x、DVDD_C、VDDA_x_3P3) 为了保证芯片正常工作,芯片上电或者掉电必须满足规定。3.7.1 上电顺序

上电顺序如表7-6和图7-1。

3.7.2 掉电顺序

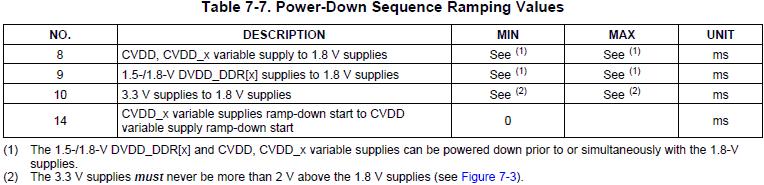

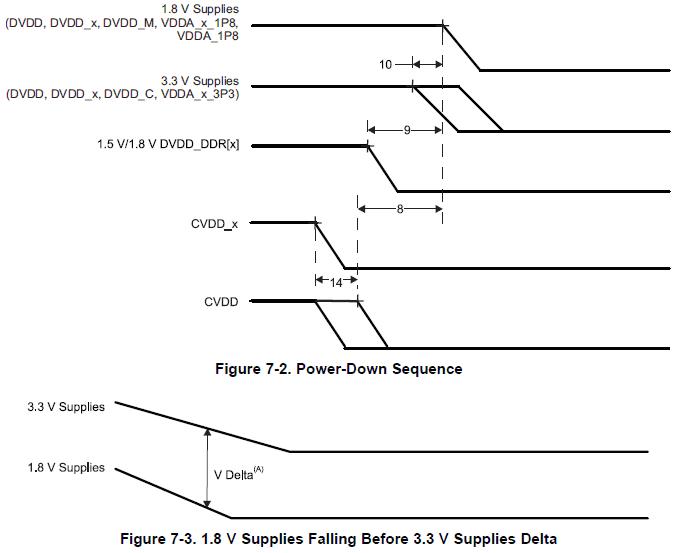

为了保证器件正常操作,表7-7和图7-2所描述的掉电顺序必须满足: