下面列出这几天在JZ4775平台折腾OV9712的调试编程步骤.

1.DATASHEET AND SAMPLE CODE: 数据手册和参考代码,这一点最好向厂家或其下的代理商要,一般都有会,也会给. 1-1.DATASHEET: 拿到DATASHEET首先要看的当然是features这一章节,在这一章节我们可以知道CMOS功能和宏观特性.如OV9712关于features内容如下:

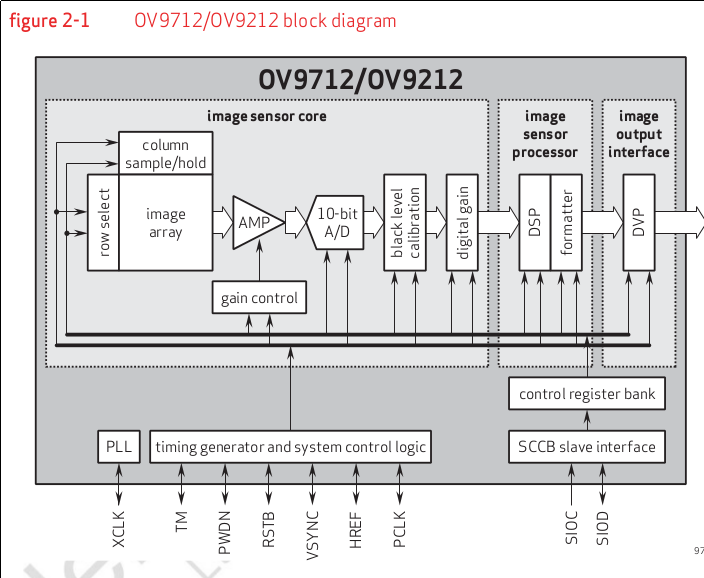

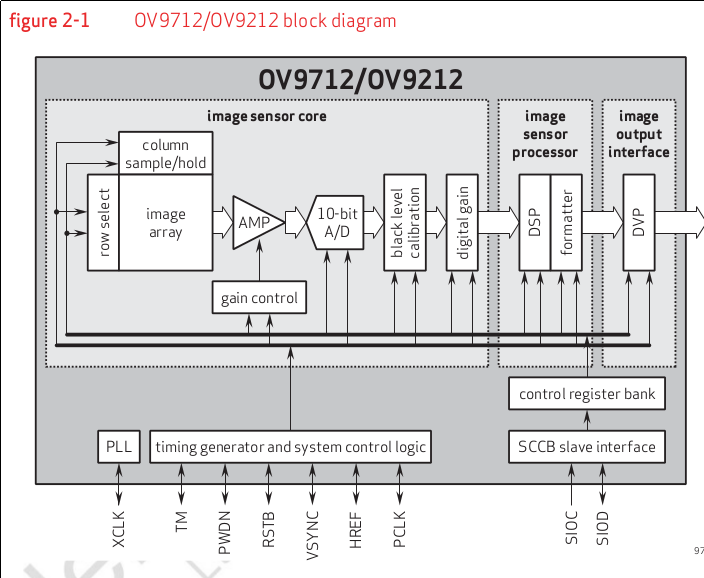

3.CMOS内部结构宏观示意图: 理解CMOS宏观的内部结构图,可以大体知道有哪些PIN脚,内部集成哪些功能模块: 由上图可知,支持的pin脚有时钟pinXCLK,电源pinPWDN,复位pinRSTB,像素pinPCLK还有SCCB的两根pinSIOC和SIOD.并行数据pinDVP.如果怀疑硬件有问题的时候,是需要查这些pin脚的.

由上图可知,支持的pin脚有时钟pinXCLK,电源pinPWDN,复位pinRSTB,像素pinPCLK还有SCCB的两根pinSIOC和SIOD.并行数据pinDVP.如果怀疑硬件有问题的时候,是需要查这些pin脚的.

4.pin脚的说明: 有些怀疑硬件问题的时候,需要用示波器量一下相应的pin是否正常工作,如是否有XCLK,是否有PCLK信号等,因此,各个pin脚的意义是必须要熟悉的.部分pin脚说明如下:

5.参考原理图: 一般来讲,硬件设计人员都是参考原厂提供的原理图画的,如果需要在原来参考的原理图上进行本质性的改动,最好咨询一下原厂.如OV9712数据手册上提供的原理图的DVP为10,但是JZ4775平台的DVP只有8根,把OV9712的DVP修改成8根也是向OV9712公司确认是可行的.尤其是上电硬件复位的电路部分,更是需要注意的.有些低端的SENSOR的参考原理图也是有点问题,有时就出现上电复位不成功导致了IC工作异常(搞死人).其意义比软件sample code大多了. OV9712参考原理图如下:

如果有特别注意的地方,参考原理图会标识出来的,如上述的note1和note2.当然,这是硬件工程师需要特别关注的.驱动软件的话,略懂略懂.

1.DATASHEET AND SAMPLE CODE: 数据手册和参考代码,这一点最好向厂家或其下的代理商要,一般都有会,也会给. 1-1.DATASHEET: 拿到DATASHEET首先要看的当然是features这一章节,在这一章节我们可以知道CMOS功能和宏观特性.如OV9712关于features内容如下:

从上图我们可以知道,OV9712一些特性,如:低照明模式(夜间模式)、自动曝光、自动调节增益、自动白平衡、可以实现16的区域的局部曝光控制(一些高档的CMOS都有此功能,如MI367)、镜片校正等;输出格式为rawRGB(bayer是rawRGB格式的一种);支持的图像大小为WXGA(1280x800)和640x400;可编程总线协议为SCCB(兼容IIC);DVP(即图像传输线)为并行输出;另外,OV9712还支持PLL倍频或降频.如我手头给OV9712的MCLK为24MHZ,其PCLK即为48MHZ.这些只是一些宏观的功能,具体实现的话,可以通过SCCB控制内部寄存器实现.

除了features之外,目录是第二个要看的,主要要知道一些编程相关的信息,如SCCB接口在哪、VSYNC、HSYNC、PCLK极性配置、DVP接口、寄存器相关.

1-2.SAMPLE CODE:

厂家提供的参考代码,通过厂家提供的代码可以更好地理解datasheet.OV9712(WXGA)的SAMPLE CODE如下:

@@ Res_1280x800

60 12 80 ;Reset

60 09 10

;;---------------------------------------------------------

;;Core Settings

;;---------------------------------------------------------

60 1e 07

60 5f 18

60 69 04

60 65 2a

60 68 0a

60 39 28

60 4d 90

60 c1 80

60 0c 30

60 6d 02

;;---------------------------------------------------------

;;DSP

;;---------------------------------------------------------

60 96 f1 ; DSP options enable

60 bc 68 ; [7] reserved; [6:5] bd_sel; [4] th_opt; [3:0] thresh_hold

;;---------------------------------------------------------

;;Resolution and Format

;;---------------------------------------------------------

60 12 00

60 3b 00 ; DSP Downsample

60 97 80 ; [7] smph_mean; [6] reserved; [5:4] smph_drop

;;---- Place generated settings here ----;;

60 17 25

60 18 A2

60 19 01

60 1a CA

60 03 0A

60 32 07

60 98 00

60 99 00

60 9a 00

60 57 00

60 58 C8

60 59 A0

60 4c 13

60 4b 36

60 3d 3c

60 3e 03

60 bd A0

60 be c8

;;---------------------------------------------------------

;;AWB

;;---------------------------------------------------------

;;

;;---------------------------------------------------------

;;Lens Correction

;;---------------------------------------------------------

;;---- Place lens correction settins here ----;;

;; Lens model :

;; Module type :

;;---------------------------------------------------------

;;YAVG

;;---------------------------------------------------------

;;---- Place generated "WIndows Weight" settings here ----;;

60 4e 55 ;AVERAGE

60 4f 55 ;

60 50 55 ;

60 51 55 ;

60 24 55 ;Exposure windows

60 25 40

60 26 a1

;;---------------------------------------------------------

;;Clock

;;---------------------------------------------------------

60 5c 52

60 5d 00

60 11 01

60 2a 98

60 2b 06

60 2d 00

60 2e 00

;;---------------------------------------------------------

;;General

;;---------------------------------------------------------

60 13 A5

60 14 40 ;Gain Ceiling 8X

;;---------------------------------------------------------

;;Banding

;;---------------------------------------------------------

60 4a 00

60 49 ce

60 22 03

60 09 00

3.CMOS内部结构宏观示意图: 理解CMOS宏观的内部结构图,可以大体知道有哪些PIN脚,内部集成哪些功能模块:

由上图可知,支持的pin脚有时钟pinXCLK,电源pinPWDN,复位pinRSTB,像素pinPCLK还有SCCB的两根pinSIOC和SIOD.并行数据pinDVP.如果怀疑硬件有问题的时候,是需要查这些pin脚的.

由上图可知,支持的pin脚有时钟pinXCLK,电源pinPWDN,复位pinRSTB,像素pinPCLK还有SCCB的两根pinSIOC和SIOD.并行数据pinDVP.如果怀疑硬件有问题的时候,是需要查这些pin脚的.

4.pin脚的说明: 有些怀疑硬件问题的时候,需要用示波器量一下相应的pin是否正常工作,如是否有XCLK,是否有PCLK信号等,因此,各个pin脚的意义是必须要熟悉的.部分pin脚说明如下:

5.参考原理图: 一般来讲,硬件设计人员都是参考原厂提供的原理图画的,如果需要在原来参考的原理图上进行本质性的改动,最好咨询一下原厂.如OV9712数据手册上提供的原理图的DVP为10,但是JZ4775平台的DVP只有8根,把OV9712的DVP修改成8根也是向OV9712公司确认是可行的.尤其是上电硬件复位的电路部分,更是需要注意的.有些低端的SENSOR的参考原理图也是有点问题,有时就出现上电复位不成功导致了IC工作异常(搞死人).其意义比软件sample code大多了. OV9712参考原理图如下:

如果有特别注意的地方,参考原理图会标识出来的,如上述的note1和note2.当然,这是硬件工程师需要特别关注的.驱动软件的话,略懂略懂.