KCU105自测

一、KCU105组成元件

KCU105组成元件如图1所示。

图1 KCU105组成元件

二、KCU105自测

Step1:设置配置开关

图1 KCU105组成元件

二、KCU105自测

Step1:设置配置开关

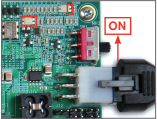

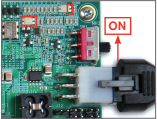

将开关SW15-6打在关闭状态(如图1中28区域所示)。

备注:SW15-6(FPGA_M2)用于选择配置模式,其中0代表masterSPI 配置模式;1代表JTAG配置模式。

Step2:连接电源

将开关SW15-6打在关闭状态(如图1中28区域所示)。

备注:SW15-6(FPGA_M2)用于选择配置模式,其中0代表masterSPI 配置模式;1代表JTAG配置模式。

Step2:连接电源

将电源插头与J15(如图1中39区域所示)相连。打开开关SW1(如图1中30区域所示)。

备注:LED-DS3绿 {MOD}代表电源系统正常。

Step3:初始化配置

将电源插头与J15(如图1中39区域所示)相连。打开开关SW1(如图1中30区域所示)。

备注:LED-DS3绿 {MOD}代表电源系统正常。

Step3:初始化配置

按下SW4(如图1中27区域所示),初始化配置。

Step4:执行自测

按下SW4(如图1中27区域所示),初始化配置。

Step4:执行自测

自测由一系列测试组成。当一个测试通过时,对应的LED灯会亮起(如图1中区域23所示)。其中CLOCK、DDR、BRAM、FLASH、I2C测试不需要用户输入;DIP、PB、Rotary测试需要用户开启相关开关。

备注:DIP测试通过,仅当DIP开关SW12(如图1中26区域所示)全部打开;PB测试通过,仅当push-buttons均被按过(如图1中区域24所示),上下左右按键不要求按下顺序,但中心按键要求最后按下;Rotary测试通过要求旋转开关SW13(如图1中40区域所示)。

Step5:安装vivado设计套件

Step6:进一步学习

AXI

AXI(AdvancedeXtensible Interface)是Xilinx从6系列的FPGA开始引入的一个接口协议,主要描述了主设备和从设备之间的数据传输方式。在ZYNQ中继续使用,版本是AXI4,ZYNQ内部设备都有AXI接口。其实AXI就是ARM公司提出的AMBA(AdvancedMicrocontroller Bus Architecture)的一个部分,是一种高性能、高带宽、低延迟的片内总线,也用来替代以前的AHB和APB总线。第一个版本的AXI(AXI3)包含在2003年发布的AMBA3.0中,AXI的第二个版本AXI(AXI4)包含在2010年发布的AMBA

4.0之中。

一、AXI4的三种接口

AXI4——Forhigh-performance memory-mapped requirements

自测由一系列测试组成。当一个测试通过时,对应的LED灯会亮起(如图1中区域23所示)。其中CLOCK、DDR、BRAM、FLASH、I2C测试不需要用户输入;DIP、PB、Rotary测试需要用户开启相关开关。

备注:DIP测试通过,仅当DIP开关SW12(如图1中26区域所示)全部打开;PB测试通过,仅当push-buttons均被按过(如图1中区域24所示),上下左右按键不要求按下顺序,但中心按键要求最后按下;Rotary测试通过要求旋转开关SW13(如图1中40区域所示)。

Step5:安装vivado设计套件

Step6:进一步学习

AXI

AXI(AdvancedeXtensible Interface)是Xilinx从6系列的FPGA开始引入的一个接口协议,主要描述了主设备和从设备之间的数据传输方式。在ZYNQ中继续使用,版本是AXI4,ZYNQ内部设备都有AXI接口。其实AXI就是ARM公司提出的AMBA(AdvancedMicrocontroller Bus Architecture)的一个部分,是一种高性能、高带宽、低延迟的片内总线,也用来替代以前的AHB和APB总线。第一个版本的AXI(AXI3)包含在2003年发布的AMBA3.0中,AXI的第二个版本AXI(AXI4)包含在2010年发布的AMBA

4.0之中。

一、AXI4的三种接口

AXI4——Forhigh-performance memory-mapped requirements

AXI4-Lite——For simple,low-throughput memory-mapped communication

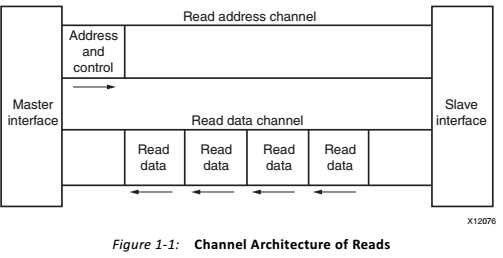

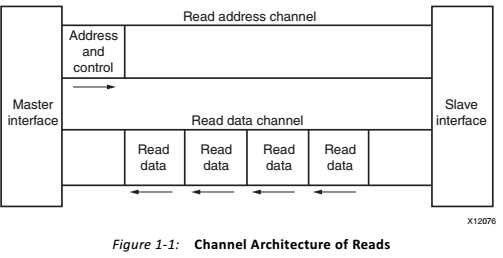

AXI4-Stream——For high-speedstreaming data AXI4协议相当于原来的AHB协议,提供高速的系统内部互连通道,可以支持burst模式,主要用于处理器访问存储等需要高速数据的场合;AXI4-Lite为外设提供单个数据传输,相当于原来的APB协议,用于访问一些低速外设;AXI4-Stream接口就像FIFO一样,数据传输的时候不需要地址,而是主从设备直接连续读写数据,主要用于如视频、高速AD、PCIe、DMA接口等需要高速数据传输的场合,跟Xilinx原来的LocalLink协议类似。 二、工作模式 AXI4和AXI4-Lite接口包含5个不同的通道: Read Address Channel

Write Address Channel

Read Data Channel

Write Data Channel

Write Response Channel 图1-1和1-2表式主从设备之间的读写信道模式。AXI4提供独立的数据和地址的读写连接,允许同时的、双向的数据传输;AXI4要求1个地址,传输256字的数据;AXI4协议描述了各种选择,来实现高速数据输出。AXI4-Lite很多地方与AXI4相似,但是不支持突发数据传输。AXI4-Stream协议定义一个独立信道传输数据流,与AXI4不同,AXI4-Stream接口支持不限数量的突发数据传输。

图1 KCU105组成元件

二、KCU105自测

Step1:设置配置开关

图1 KCU105组成元件

二、KCU105自测

Step1:设置配置开关

将开关SW15-6打在关闭状态(如图1中28区域所示)。

备注:SW15-6(FPGA_M2)用于选择配置模式,其中0代表masterSPI 配置模式;1代表JTAG配置模式。

Step2:连接电源

将开关SW15-6打在关闭状态(如图1中28区域所示)。

备注:SW15-6(FPGA_M2)用于选择配置模式,其中0代表masterSPI 配置模式;1代表JTAG配置模式。

Step2:连接电源

将电源插头与J15(如图1中39区域所示)相连。打开开关SW1(如图1中30区域所示)。

备注:LED-DS3绿 {MOD}代表电源系统正常。

Step3:初始化配置

将电源插头与J15(如图1中39区域所示)相连。打开开关SW1(如图1中30区域所示)。

备注:LED-DS3绿 {MOD}代表电源系统正常。

Step3:初始化配置

按下SW4(如图1中27区域所示),初始化配置。

Step4:执行自测

按下SW4(如图1中27区域所示),初始化配置。

Step4:执行自测

自测由一系列测试组成。当一个测试通过时,对应的LED灯会亮起(如图1中区域23所示)。其中CLOCK、DDR、BRAM、FLASH、I2C测试不需要用户输入;DIP、PB、Rotary测试需要用户开启相关开关。

备注:DIP测试通过,仅当DIP开关SW12(如图1中26区域所示)全部打开;PB测试通过,仅当push-buttons均被按过(如图1中区域24所示),上下左右按键不要求按下顺序,但中心按键要求最后按下;Rotary测试通过要求旋转开关SW13(如图1中40区域所示)。

Step5:安装vivado设计套件

Step6:进一步学习

AXI

AXI(AdvancedeXtensible Interface)是Xilinx从6系列的FPGA开始引入的一个接口协议,主要描述了主设备和从设备之间的数据传输方式。在ZYNQ中继续使用,版本是AXI4,ZYNQ内部设备都有AXI接口。其实AXI就是ARM公司提出的AMBA(AdvancedMicrocontroller Bus Architecture)的一个部分,是一种高性能、高带宽、低延迟的片内总线,也用来替代以前的AHB和APB总线。第一个版本的AXI(AXI3)包含在2003年发布的AMBA3.0中,AXI的第二个版本AXI(AXI4)包含在2010年发布的AMBA

4.0之中。

一、AXI4的三种接口

AXI4——Forhigh-performance memory-mapped requirements

自测由一系列测试组成。当一个测试通过时,对应的LED灯会亮起(如图1中区域23所示)。其中CLOCK、DDR、BRAM、FLASH、I2C测试不需要用户输入;DIP、PB、Rotary测试需要用户开启相关开关。

备注:DIP测试通过,仅当DIP开关SW12(如图1中26区域所示)全部打开;PB测试通过,仅当push-buttons均被按过(如图1中区域24所示),上下左右按键不要求按下顺序,但中心按键要求最后按下;Rotary测试通过要求旋转开关SW13(如图1中40区域所示)。

Step5:安装vivado设计套件

Step6:进一步学习

AXI

AXI(AdvancedeXtensible Interface)是Xilinx从6系列的FPGA开始引入的一个接口协议,主要描述了主设备和从设备之间的数据传输方式。在ZYNQ中继续使用,版本是AXI4,ZYNQ内部设备都有AXI接口。其实AXI就是ARM公司提出的AMBA(AdvancedMicrocontroller Bus Architecture)的一个部分,是一种高性能、高带宽、低延迟的片内总线,也用来替代以前的AHB和APB总线。第一个版本的AXI(AXI3)包含在2003年发布的AMBA3.0中,AXI的第二个版本AXI(AXI4)包含在2010年发布的AMBA

4.0之中。

一、AXI4的三种接口

AXI4——Forhigh-performance memory-mapped requirementsAXI4-Lite——For simple,low-throughput memory-mapped communication

AXI4-Stream——For high-speedstreaming data AXI4协议相当于原来的AHB协议,提供高速的系统内部互连通道,可以支持burst模式,主要用于处理器访问存储等需要高速数据的场合;AXI4-Lite为外设提供单个数据传输,相当于原来的APB协议,用于访问一些低速外设;AXI4-Stream接口就像FIFO一样,数据传输的时候不需要地址,而是主从设备直接连续读写数据,主要用于如视频、高速AD、PCIe、DMA接口等需要高速数据传输的场合,跟Xilinx原来的LocalLink协议类似。 二、工作模式 AXI4和AXI4-Lite接口包含5个不同的通道: Read Address Channel

Write Address Channel

Read Data Channel

Write Data Channel

Write Response Channel 图1-1和1-2表式主从设备之间的读写信道模式。AXI4提供独立的数据和地址的读写连接,允许同时的、双向的数据传输;AXI4要求1个地址,传输256字的数据;AXI4协议描述了各种选择,来实现高速数据输出。AXI4-Lite很多地方与AXI4相似,但是不支持突发数据传输。AXI4-Stream协议定义一个独立信道传输数据流,与AXI4不同,AXI4-Stream接口支持不限数量的突发数据传输。