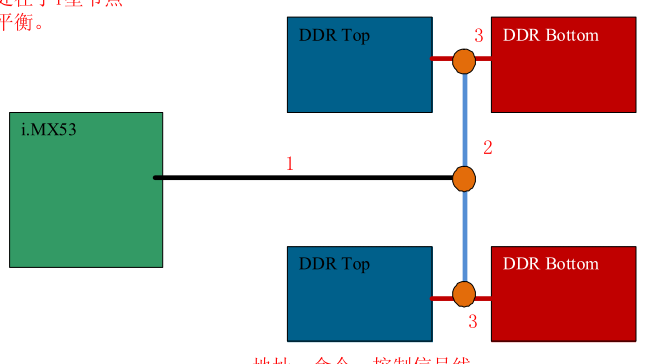

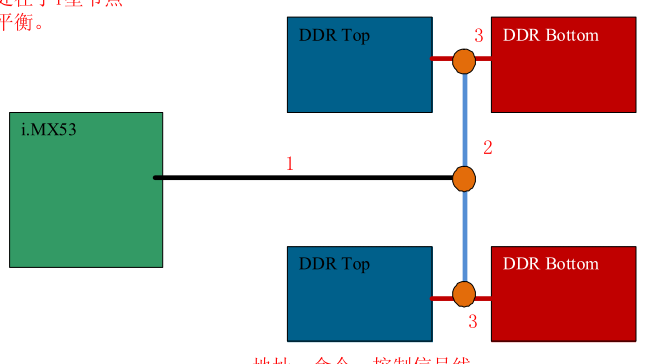

使用 2 片 16bits 的 DDR3和 4 片 8bits DDR3(双面贴片) 拓扑结构与 2 片 DDR 的要求基本一致,在此重点说明4片DDR3双面贴片,其效果图如下所示:

此设计重点为严格T型对称。 布线设计步骤优先级: 1.首先设计好时钟分叉点所有等长,优先将CPU至对称点布线完成,在布线时尽量在此阶段满足所有地址线等 长; 2.选择左右任意一个DDR3进行线段与对称中心点布线,布线完成后按照此区域布线特点进行另一边DDR3设 计。 布线约束要求: 1.4根时钟分叉线点严格等长,此为必须条件; 2.4根地址线分叉线严格等长为可选条件,等长要求可以在一定程度上进行调整。 若地址线象时钟分叉线严格等长,则中心对称点要严格位于中间,布线具有一定难度; 若地址线象时钟分叉线非严格等长,则对称点要严格可左右进行一定程度偏移,布线较容易。

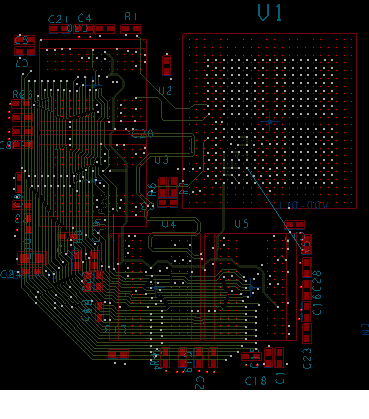

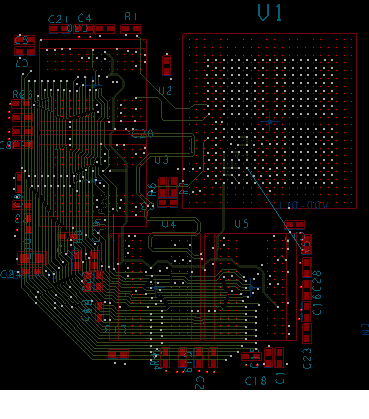

非严格对称 可见中间过孔在DDR之间严格对称 为了满足地址线对称等长,在DDR3区域下方需要较大空间来进行绕线满足等长要求,一般地址线数量为12到15根左右。

非严格对称 可见中间过孔在DDR之间严格对称 为了满足地址线对称等长,在DDR3区域下方需要较大空间来进行绕线满足等长要求,一般地址线数量为12到15根左右。

L型布局

L型布局

一字型布局不同点: L型器件必须离CPU很近,这样才能满足时钟线与地址线即DQS在一定约束范围内,距离保持在3mm内为好; 一字型器件可以离CPU较远,距离保持在5mm为好。 造成此差异是地址线在中间分叉点不易对称,造成地址线和时钟线差值较大。类同点: 最下方地址线不易离DDR器件过远,此会造成最长的地址线分叉点与时钟线差异很大,所以DDR3下方超出地址线根数以6为最大数。

布线设计步骤优先级:

首先设计好时钟分叉点所有等长; 再次从最上方或者最左边设计完该DDR3的所有地址线布线,然后按照同样过孔即走线方式完成相邻的DDR3布线直到所有DDR3被完成; 最后布线从CPU到中间分叉点的走线。

第二种约束情况,其器件布局如下图所示,即:

布线设计步骤优先级: 首先完成从从CPU到中间分叉点的走线,所有走线必须等长,过孔阵列必须严格位于4片DDR3的正中间; 再次从最左边设计完该DDR3的所有地址线布线,然后按照同样走线方式完成相邻的DDR3布线直到所有DDR3被完成。 最后需要调整左边2片和右边2片DDR3严格等长对称。 在约束中,每个DDR3的时钟和地址严格等长,最长和最短地址线差值需控制在500mil之内。

由于需要完成中间分叉点至CPU的所有线等长,所以和第一种约束相互比较,DDR3下方超出地址线根数最好保持在9根以上。同时CPU到DDR3的距离要大大增加,这样会造成DQS与时钟线差值大于1500mil,所以在距离上也不能太远,最好复制参考电源的器件布局距离。

第三种约束情况,其器件布局如下图所示,即:

布线设计步骤优先级: 首先完成从从CPU到中间分叉点的走线,所有走线必须等长; 再次从最左边设计完该DDR3的所有地址线布线,然后按照同样走线方式完成相邻的DDR3布线直到所有DDR3被完成。 最后需要完成时钟线和地址线所有分叉线等长,但是可以在时钟线与地址线约束方面降低一些要求。

注意此时地址线和时钟线分叉方式一模一样,即进行两次分叉。 若CPU和DDR3距离不够远,则需要将地址线往外或者下方移动,以避开DDR3地和电源过孔,这些过孔会极大的降低绕线效率。如上图所示,DDR器件外面的地址线为12根以上。

最后注意: 首先设计时钟分叉线; 器件布局很重要,最好复制原厂给出的参考PCB的数据,这样可以大大减少设计风险。

此设计重点为严格T型对称。 布线设计步骤优先级: 1.首先设计好时钟分叉点所有等长,优先将CPU至对称点布线完成,在布线时尽量在此阶段满足所有地址线等 长; 2.选择左右任意一个DDR3进行线段与对称中心点布线,布线完成后按照此区域布线特点进行另一边DDR3设 计。 布线约束要求: 1.4根时钟分叉线点严格等长,此为必须条件; 2.4根地址线分叉线严格等长为可选条件,等长要求可以在一定程度上进行调整。 若地址线象时钟分叉线严格等长,则中心对称点要严格位于中间,布线具有一定难度; 若地址线象时钟分叉线非严格等长,则对称点要严格可左右进行一定程度偏移,布线较容易。

非严格对称 可见中间过孔在DDR之间严格对称 为了满足地址线对称等长,在DDR3区域下方需要较大空间来进行绕线满足等长要求,一般地址线数量为12到15根左右。

非严格对称 可见中间过孔在DDR之间严格对称 为了满足地址线对称等长,在DDR3区域下方需要较大空间来进行绕线满足等长要求,一般地址线数量为12到15根左右。- 使用 4 片 8bits 的 DDR3 (单面贴片)

L型布局

L型布局

一字型布局不同点: L型器件必须离CPU很近,这样才能满足时钟线与地址线即DQS在一定约束范围内,距离保持在3mm内为好; 一字型器件可以离CPU较远,距离保持在5mm为好。 造成此差异是地址线在中间分叉点不易对称,造成地址线和时钟线差值较大。类同点: 最下方地址线不易离DDR器件过远,此会造成最长的地址线分叉点与时钟线差异很大,所以DDR3下方超出地址线根数以6为最大数。

布线设计步骤优先级:

首先设计好时钟分叉点所有等长; 再次从最上方或者最左边设计完该DDR3的所有地址线布线,然后按照同样过孔即走线方式完成相邻的DDR3布线直到所有DDR3被完成; 最后布线从CPU到中间分叉点的走线。

第二种约束情况,其器件布局如下图所示,即:

布线设计步骤优先级: 首先完成从从CPU到中间分叉点的走线,所有走线必须等长,过孔阵列必须严格位于4片DDR3的正中间; 再次从最左边设计完该DDR3的所有地址线布线,然后按照同样走线方式完成相邻的DDR3布线直到所有DDR3被完成。 最后需要调整左边2片和右边2片DDR3严格等长对称。 在约束中,每个DDR3的时钟和地址严格等长,最长和最短地址线差值需控制在500mil之内。

由于需要完成中间分叉点至CPU的所有线等长,所以和第一种约束相互比较,DDR3下方超出地址线根数最好保持在9根以上。同时CPU到DDR3的距离要大大增加,这样会造成DQS与时钟线差值大于1500mil,所以在距离上也不能太远,最好复制参考电源的器件布局距离。

第三种约束情况,其器件布局如下图所示,即:

布线设计步骤优先级: 首先完成从从CPU到中间分叉点的走线,所有走线必须等长; 再次从最左边设计完该DDR3的所有地址线布线,然后按照同样走线方式完成相邻的DDR3布线直到所有DDR3被完成。 最后需要完成时钟线和地址线所有分叉线等长,但是可以在时钟线与地址线约束方面降低一些要求。

注意此时地址线和时钟线分叉方式一模一样,即进行两次分叉。 若CPU和DDR3距离不够远,则需要将地址线往外或者下方移动,以避开DDR3地和电源过孔,这些过孔会极大的降低绕线效率。如上图所示,DDR器件外面的地址线为12根以上。

最后注意: 首先设计时钟分叉线; 器件布局很重要,最好复制原厂给出的参考PCB的数据,这样可以大大减少设计风险。