PCB设计操作流程和注意事项

最后修改时间:2014-12-10

本文主要描述PCB设计的流程和注意事项。汇总了一些小技巧和软件设置。主要使用的软件有:Cadence Allegro 15.5,CAM350 V10.5,PROE5,Si9000等。

在allegro15.7中也有效。

使用Allegro 15.7中的Orcad Capture CIS(or Allegro Design Entry CIS)会出现如下问题的说明:

exception access violation

threads has read from or write to a virtual address for which it does not have the appropriate access

当用Allegro 15.7的Orcad Capture CIS(or Allegro Design Entry CIS)打开一个文件时,弹出错误窗口,大意是一个线程读取虚拟地址错误,程序将关闭,点确定是保存后再关闭,点取消是直接关闭程序

解决方法:

step1: 从开始菜单中点击运行,输入regedit,进入注册表编辑器;

HKEY_CURRENT_USER SoftwareMicrosoftWindowsCurrentVersionPoliciesExplorer下的 NoRecentDocsHistory注册表项(DWORD类型的)设置为0;

step2: 用windows任务管理器结束explorer.exe进程,然后再用其新建一个任务,输入explorer,再次启动Orcad Capture CIS(or Allegro Design Entry CIS)即可。

来源:http://fcy007.blog.163.com/blog/static/6218020087425653551/

创建网表 Creat Netlist

在原理图中点击选中Design Resources下的.dsn文件,Tools --> Creat Netlist;或者直接点击Creat Netlist按钮。弹出Undo warning,选yes。然后一路yes下去。

设置封装库路径

若封装不齐,无法导入网表。

在PCB editor中,Setup --> User Preferences Editor --> Design_paths:padpath & psmpath。这两个路径设置为封装所在的文件夹路径。

PCB导入网表

打开.brd文件。File --> Import --> Logic。Import logic type选择Design entry CIS;Place changed component:Always;勾选Ignore FIXED property。找到网表所在的allegro文件夹,Import Cadence确认导入。

如果是规则的外框,可以自己画一个outline,并且做好倒角。做倒角的时候可以在Control栏的option中选择倒角半径。然后设置离板边40mil的Route keepin,和离板边80mil的Package keepin框。

将line转换成shape。Shape --> Compose Shape,依次选中各个线段。在option中,active class:Board Geometry;add Shape to Subclass:Outline。这里的line必须严格封闭成一个区域。否则可能无法生成Shape。

如果生成Outline Shape失败。在line的不连接处会生成一些小导线。一般在Top层。使用Tools --> Reports --> Dangling Lines Report可以找到它们。把它们删掉。检查line的中断处,用show measure来查看线头间距。Vertex --> ix(iy)来准确地连接上。

也可以使用allegro的change功能将DXF的线段变成outline。Edit --> change,在右边Control的Option中选择目标图层和线宽。change后DXF的线段直接变成outline。change成的outline线段连接紧密,可以直接做倒角。

使用Edit --> Z-Copy生成package keepin 和 route keepin。器件布放区域一般离板边80mil(或2mm),禁止布线区离板边40mil(或1mm)。

放入器件

Place中有manually和Quickplace两种方式。如果器件较少,可以手动放置。如果器件较多,成百上千各器件,Quickplace是首选。Quickplace需要board geometry outline。软件会把器件自动放置在板边界旁边。

1oz铜厚约为34微米,约1.3386mil。一般取1oz铜厚。

计算值尽量接近目标值。这样也方便工厂调整阻抗。

得到W1 = 8.01,S1 = 5.01,D1 = 6.00。设置差分线规则的时候可以参考这些数值。

对于信号线来说,目的在于控制阻抗而不是线宽。把线宽设置成5.01或5.02这种有小数的形式,让工厂快速地找到相应的信号线。

点天平图标Cns打开规则设置。Spacing rule set设置的是间距。Physical(lines/vias) rule set设置的是线宽等导线的属性。两个大类都分别有4个选项。

Set values为设置规则。新增规则时,填好规则名,先点Add,再去设置各个选项。具体的设置参考设计说明书。

Attach property,nets... 为信号线赋予执行规则。可以在板上点选net,也可以用More键来找需要的net。Find by Name or Property的Object type下拉框中选择 net。在左边的备选框里选择需要的网络信号。右边是已选择的信号。选择完成后,点击apply。这时是Edit Property和Show Properties两个框。在Edit Property里选择规则类型,规则名填在value中,apply即可。

Assignment Table为Net选择执行的区域。Area Property是信号所在的区域。右边的下拉框中选择在这个区域内执行的规则。

Set DRC models一般保持默认状态。

打开Spacing rule set里的same net DRC检查选项。

参考设计说明书,把Spacing和Physical的规则设置好。然后用Attach Property赋予各个信号规则。设置好规则后,Assignment Table指定在各个区域内执行的规则。

规则设置也是按照模块的顺序来进行。这样不会漏掉规则。在Cmgr中设置Bus与Group。设置Bus是为了方便查找信号。用Group来设置等长线。还需要设置最大过孔数(Max Via Count),最大线长。

设置Crt_RGB信号等长时需引入封装引线长度。封装引线长度在原理图中设置。

打开Cns,在Physical Rule中新建一个规则。起名为85OHM-W5.01S6.99。

如图所示,填入各项参数。 在Physical rule set的assign table中,指定区域的执行规则。举例如下:

在Physical rule set的assign table中,指定区域的执行规则。举例如下:

将两个信号(Nets)设置为差分对。点击Cmgr打开Constrain Management,左边找到Net下的Routing --> Differential Pair。框选差分信号,右键Creat --> Differencial Pair。Phase Tolerance是差分线组间的长度差距,一般设5mil。Neck gap设为4mil。给这对差分信号赋予规则。一定要2个NET都赋予同样的规则。

Net: EXAMPLE

DIFFP_MIN_SPACE = 6.99 MIL

DIFFP_PHASE_TOL = 5 mil

LOGICAL_PATH = @123.schematic1(sch_1):loutn

NET_PHYSICAL_TYPE = 85OHM-W5.01S6.99

NET_SPACING_TYPE = 20 MIL

前两项可以在Cmgr中设置。NET_PHYSICAL_TYPE用前面定义好的85欧姆规则。NET_SPACING_TYPE指的是差分线和其他信号线之间的距离。

在Color and Visibility中选中Drc的Through All、Package_Top、Package_Bottom。可以显示CC DRC。在器件的place_bound_top重叠时会有CC DRC。

有些器件底部要挖空一部分。器件封装上会画有outline来提示。需要根据器件的outline来修改板子的形状。

把各个接口对齐放置好。根据DXF,接口的外边在一条水平线上。若不平行,测量并用move - iy的方式调整。两个并排放置的USB接头可以根据走线的实际情况来互换位置。要有封装才能导入logic。首先完善封装库。封装可以从之前的Brd文件中导出来。

正片与负片

Xsection(Layout Cross Section)中有层的选项。Film type:Negative/Positive。TOP和BOTTOM层(信号层)一般都是正片。中间电源层和地层为负片。负片用Anti-Etch来划分区域。制造过程中,正片是留下有线的部分。而负片是腐蚀掉有线的部分。

特殊区域规则设置

首先设置一条规则;其次赋予该特殊区域规则;当两个规则相遇,设置优先执行的规则;最后更新一下区域。

设置规则:天平图标Cns中,在Spacing rule set 的“Set value...”选项中,Add一个新的规则。编辑shape的属性,指定执行规则。在Assignment table...中可以设定优先规则,在最右边的下拉框里选择。最后把shape拖动一下或edit一下,让软件更新操作。

铜箔边界得和pin平行。输入数值50,间距小于50mil的都不会产生尖角。

设置Minimum aperture for artwork fill的参数,可以让铜箔不进入宽度小于这个参数的缝隙。

如果连接上差分对后还是显示黄 {MOD}。点击菜单栏Analyze --> Analysis modes。在DRC Modes里把All differential pair设置为On。确定即可。

设置PCB元器件的封装。对于一些焊盘、测试点类的封装,package_Height_Max = 0.1 MIL 最好不要设置为0。在proe中建立3D元件库,文件名和allegro封装库一致。导入的时候会根据文件名搜寻匹配模型。

对于机械孔,只需要mechanical pin即可。不需要place_bound_top等信息。

基准点MASK,视为无器件高度。将package_height设置为0.01mil。PROE根据place_bound_top的形状和高度信息。

PROE中导入的零件来自allegro的封装库。emp文件像是一个索引。在.brd文件中修改器件的参数,比如器件高度。导入PROE中不会受影响。因为PROE使用的是封装库里的器件参数。

使用拼板前的PCB。只应有单板。输出emn和emp之前应先备份,取另一个文件名。文件名不能有空格下划线等字符。

PROE5对应IDF3.0格式。目前我们导出IDF2.0格式。使用IDF3.0格式也可以。

PROE中要有相对应的零件(.prt)。文件名和PCB元件封装名一致。导入时PROE会根据文件名自动寻找零件。这些零件需要放在安装目录的bin文件夹中。或者放在自定义的library文件夹中。如果找不到对应的零件,PROE会根据器件的place_bound_top形状和器件高度拉伸一个零件出来。

PCB元件封装的原点要和.prt的基准点对应起来。元件封装和零件的X、Y轴正方向一致。根据右手螺旋定则可以得到Z轴正方向。零件的基准点要放在器件和PCB重合的那个面上。

可以看到单位是ELA2.6,即6位小数,2位整数。这个要调整到和Gerber一样的状态。

这里调整为5.5,应用到所有图层。调整好,点击Finish即可。

如果不进行此项设置,CAM350 V10可能会在导入某层Gerber时卡死。

有的时候CAM350 V10.5导入274-X文件时卡死,原因是数据量太大。输出Gerber时不要把好几层都叠在一个文件中。

最后修改时间:2014-12-10

本文主要描述PCB设计的流程和注意事项。汇总了一些小技巧和软件设置。主要使用的软件有:Cadence Allegro 15.5,CAM350 V10.5,PROE5,Si9000等。

导入网表

Allegro 15.5打开*.dsn/*.opj文件出错解决方法在allegro15.7中也有效。

使用Allegro 15.7中的Orcad Capture CIS(or Allegro Design Entry CIS)会出现如下问题的说明:

exception access violation

threads has read from or write to a virtual address for which it does not have the appropriate access

当用Allegro 15.7的Orcad Capture CIS(or Allegro Design Entry CIS)打开一个文件时,弹出错误窗口,大意是一个线程读取虚拟地址错误,程序将关闭,点确定是保存后再关闭,点取消是直接关闭程序

解决方法:

step1: 从开始菜单中点击运行,输入regedit,进入注册表编辑器;

HKEY_CURRENT_USER SoftwareMicrosoftWindowsCurrentVersionPoliciesExplorer下的 NoRecentDocsHistory注册表项(DWORD类型的)设置为0;

step2: 用windows任务管理器结束explorer.exe进程,然后再用其新建一个任务,输入explorer,再次启动Orcad Capture CIS(or Allegro Design Entry CIS)即可。

来源:http://fcy007.blog.163.com/blog/static/6218020087425653551/

创建网表 Creat Netlist

在原理图中点击选中Design Resources下的.dsn文件,Tools --> Creat Netlist;或者直接点击Creat Netlist按钮。弹出Undo warning,选yes。然后一路yes下去。

设置封装库路径

若封装不齐,无法导入网表。

在PCB editor中,Setup --> User Preferences Editor --> Design_paths:padpath & psmpath。这两个路径设置为封装所在的文件夹路径。

PCB导入网表

打开.brd文件。File --> Import --> Logic。Import logic type选择Design entry CIS;Place changed component:Always;勾选Ignore FIXED property。找到网表所在的allegro文件夹,Import Cadence确认导入。

导入DXF,绘制PCB的形状

在Board Geometry 层新建一个Dxf层,把DXF文件全部导入进去。在Setup - Subclasses里为BOARD GEOMETRY新建一个层,名字自取。然后Import-DXF。DXF units选择MM。因为DXF使用的是MM。勾选Incremental addition。在Edit/View layers..里Sellect all,下方的Class选择BOARD GEOMETRY,Subclass选择DXF。点击Map,选中的图层都会设为DXF。汉字部分不会导入。如果是规则的外框,可以自己画一个outline,并且做好倒角。做倒角的时候可以在Control栏的option中选择倒角半径。然后设置离板边40mil的Route keepin,和离板边80mil的Package keepin框。

将line转换成shape。Shape --> Compose Shape,依次选中各个线段。在option中,active class:Board Geometry;add Shape to Subclass:Outline。这里的line必须严格封闭成一个区域。否则可能无法生成Shape。

如果生成Outline Shape失败。在line的不连接处会生成一些小导线。一般在Top层。使用Tools --> Reports --> Dangling Lines Report可以找到它们。把它们删掉。检查line的中断处,用show measure来查看线头间距。Vertex --> ix(iy)来准确地连接上。

也可以使用allegro的change功能将DXF的线段变成outline。Edit --> change,在右边Control的Option中选择目标图层和线宽。change后DXF的线段直接变成outline。change成的outline线段连接紧密,可以直接做倒角。

使用Edit --> Z-Copy生成package keepin 和 route keepin。器件布放区域一般离板边80mil(或2mm),禁止布线区离板边40mil(或1mm)。

放入器件

Place中有manually和Quickplace两种方式。如果器件较少,可以手动放置。如果器件较多,成百上千各器件,Quickplace是首选。Quickplace需要board geometry outline。软件会把器件自动放置在板边界旁边。

使用Si9000计算阻抗

打开Si9000,输入相关参数来计算目标阻抗。比如2层板的SATA差分信号。设置单位为mil。目标阻抗85欧姆(±10%)。FR4基板的电介质常数设为4.2。板厚1.6mm(62.9921mil)。用板厚减去铜厚和盖油厚度可得基板厚度。盖油的厚度一般由工厂控制。我们可取C1 = 1.7;C2 = 0.5。基板厚度H1 = 62.9921 - C2 - 2 * T1。这里取59.1921mil。1oz铜厚约为34微米,约1.3386mil。一般取1oz铜厚。

计算值尽量接近目标值。这样也方便工厂调整阻抗。

得到W1 = 8.01,S1 = 5.01,D1 = 6.00。设置差分线规则的时候可以参考这些数值。

对于信号线来说,目的在于控制阻抗而不是线宽。把线宽设置成5.01或5.02这种有小数的形式,让工厂快速地找到相应的信号线。

约束规则设置

设置约束规则,赋予规则点天平图标Cns打开规则设置。Spacing rule set设置的是间距。Physical(lines/vias) rule set设置的是线宽等导线的属性。两个大类都分别有4个选项。

Set values为设置规则。新增规则时,填好规则名,先点Add,再去设置各个选项。具体的设置参考设计说明书。

Attach property,nets... 为信号线赋予执行规则。可以在板上点选net,也可以用More键来找需要的net。Find by Name or Property的Object type下拉框中选择 net。在左边的备选框里选择需要的网络信号。右边是已选择的信号。选择完成后,点击apply。这时是Edit Property和Show Properties两个框。在Edit Property里选择规则类型,规则名填在value中,apply即可。

Assignment Table为Net选择执行的区域。Area Property是信号所在的区域。右边的下拉框中选择在这个区域内执行的规则。

Set DRC models一般保持默认状态。

打开Spacing rule set里的same net DRC检查选项。

参考设计说明书,把Spacing和Physical的规则设置好。然后用Attach Property赋予各个信号规则。设置好规则后,Assignment Table指定在各个区域内执行的规则。

规则设置也是按照模块的顺序来进行。这样不会漏掉规则。在Cmgr中设置Bus与Group。设置Bus是为了方便查找信号。用Group来设置等长线。还需要设置最大过孔数(Max Via Count),最大线长。

设置Crt_RGB信号等长时需引入封装引线长度。封装引线长度在原理图中设置。

电流与线宽

一般认为,线宽与电流大小呈正相关。保守估计,10mil承载250mA电流,20mil承载500mA电流,40mil承载1A电流。即1mm线宽约能过1A电流。差分线设置

用Si9000计算出合适的线宽线距后,设置相应的规则。比如,6层板,参考层为Gnd,目标阻抗85欧姆(±10%)。根据计算,设置差分线线宽为5.01mil,差分线间air gap(DiffPair primary gap)为6.99mil,DiffPair neck gap为4mil。打开Cns,在Physical Rule中新建一个规则。起名为85OHM-W5.01S6.99。

如图所示,填入各项参数。

在Physical rule set的assign table中,指定区域的执行规则。举例如下:

在Physical rule set的assign table中,指定区域的执行规则。举例如下:

将两个信号(Nets)设置为差分对。点击Cmgr打开Constrain Management,左边找到Net下的Routing --> Differential Pair。框选差分信号,右键Creat --> Differencial Pair。Phase Tolerance是差分线组间的长度差距,一般设5mil。Neck gap设为4mil。给这对差分信号赋予规则。一定要2个NET都赋予同样的规则。

Net: EXAMPLE

DIFFP_MIN_SPACE = 6.99 MIL

DIFFP_PHASE_TOL = 5 mil

LOGICAL_PATH = @123.schematic1(sch_1):loutn

NET_PHYSICAL_TYPE = 85OHM-W5.01S6.99

NET_SPACING_TYPE = 20 MIL

前两项可以在Cmgr中设置。NET_PHYSICAL_TYPE用前面定义好的85欧姆规则。NET_SPACING_TYPE指的是差分线和其他信号线之间的距离。

布局相关

设置好约束规则,开始布局。在Color and Visibility中选中Drc的Through All、Package_Top、Package_Bottom。可以显示CC DRC。在器件的place_bound_top重叠时会有CC DRC。

有些器件底部要挖空一部分。器件封装上会画有outline来提示。需要根据器件的outline来修改板子的形状。

把各个接口对齐放置好。根据DXF,接口的外边在一条水平线上。若不平行,测量并用move - iy的方式调整。两个并排放置的USB接头可以根据走线的实际情况来互换位置。要有封装才能导入logic。首先完善封装库。封装可以从之前的Brd文件中导出来。

正片与负片

Xsection(Layout Cross Section)中有层的选项。Film type:Negative/Positive。TOP和BOTTOM层(信号层)一般都是正片。中间电源层和地层为负片。负片用Anti-Etch来划分区域。制造过程中,正片是留下有线的部分。而负片是腐蚀掉有线的部分。

特殊区域规则设置

首先设置一条规则;其次赋予该特殊区域规则;当两个规则相遇,设置优先执行的规则;最后更新一下区域。

设置规则:天平图标Cns中,在Spacing rule set 的“Set value...”选项中,Add一个新的规则。编辑shape的属性,指定执行规则。在Assignment table...中可以设定优先规则,在最右边的下拉框里选择。最后把shape拖动一下或edit一下,让软件更新操作。

走线相关

布局完成后,开始layout。Fix和UnFix

这是个很好用的功能。能把导线、铜箔、器件等等板上的元素保护起来。刚开始布线的时候,有好几次把电源层的平面删除。重新设置了电源层后将它们Fix。这样避免了误操作。这也提醒用户,在操作时注意Find中选中的对象。关于铺铜时creat pin voids

铺铜时,由于铜箔与pin的间距问题,在pin和pin之间经常会产生一些尖角。一个个修改铜箔边界又很麻烦。在shape的parameters里面有个功能,Void controls选项卡create pin voids选中In-Line,distance between pins里填上引脚间距,铜箔会自动避让开,边界成一条直线。填入的数值必须大于引脚间距。否则不会避让。即这个间距以下的都不会产生尖角。一个铜箔只能避让一种间距的引脚。parameter可以用shape select选中后右键找到。铜箔边界得和pin平行。输入数值50,间距小于50mil的都不会产生尖角。

设置Minimum aperture for artwork fill的参数,可以让铜箔不进入宽度小于这个参数的缝隙。

查看差分线误差信息

打开Cmgr,左边框Net --> Routing --> Differential Pair,在右边可以看到差分线信息。Phase Tolerance是差分对组内线长差。右键Analyze可以计算当前差值。绿 {MOD}表示满足要求。如果连接上差分对后还是显示黄 {MOD}。点击菜单栏Analyze --> Analysis modes。在DRC Modes里把All differential pair设置为On。确定即可。

allegro与proe交互

主要输出.emn,.emp2个文件。

设置PCB元器件的封装。对于一些焊盘、测试点类的封装,package_Height_Max = 0.1 MIL 最好不要设置为0。在proe中建立3D元件库,文件名和allegro封装库一致。导入的时候会根据文件名搜寻匹配模型。

对于机械孔,只需要mechanical pin即可。不需要place_bound_top等信息。

基准点MASK,视为无器件高度。将package_height设置为0.01mil。PROE根据place_bound_top的形状和高度信息。

PROE中导入的零件来自allegro的封装库。emp文件像是一个索引。在.brd文件中修改器件的参数,比如器件高度。导入PROE中不会受影响。因为PROE使用的是封装库里的器件参数。

使用拼板前的PCB。只应有单板。输出emn和emp之前应先备份,取另一个文件名。文件名不能有空格下划线等字符。

PROE5对应IDF3.0格式。目前我们导出IDF2.0格式。使用IDF3.0格式也可以。

PROE中要有相对应的零件(.prt)。文件名和PCB元件封装名一致。导入时PROE会根据文件名自动寻找零件。这些零件需要放在安装目录的bin文件夹中。或者放在自定义的library文件夹中。如果找不到对应的零件,PROE会根据器件的place_bound_top形状和器件高度拉伸一个零件出来。

PCB元件封装的原点要和.prt的基准点对应起来。元件封装和零件的X、Y轴正方向一致。根据右手螺旋定则可以得到Z轴正方向。零件的基准点要放在器件和PCB重合的那个面上。

使用CAM350查看Gerber文件

CAM350 V10.5导入RS-274-D Gerber文件

CAM350导入时,注意把CAM350的精度设置成和Gerber一样。autoimport时,先检查单位,再点finish。

可以看到单位是ELA2.6,即6位小数,2位整数。这个要调整到和Gerber一样的状态。

这里调整为5.5,应用到所有图层。调整好,点击Finish即可。

CAM350 V10导入RS-274-X的Gerber文件

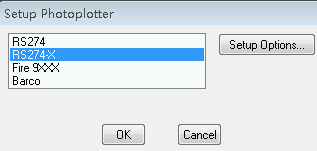

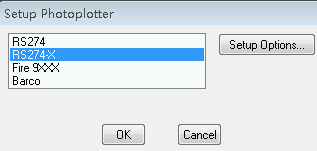

新打开CAM350 V10,工作区内没有打开的文件。File --> Setup --> Photoplotter;选择RS274-X。再AutoImport Gerber文件即可。如果不进行此项设置,CAM350 V10可能会在导入某层Gerber时卡死。

有的时候CAM350 V10.5导入274-X文件时卡死,原因是数据量太大。输出Gerber时不要把好几层都叠在一个文件中。