这篇文章主要为大家介绍了在综合布线时,我们怎么去计算布局传输延迟,下面介绍了PCB中布线的传播延时公式和计算方法,需要的朋友可以参考下

传播延时(tPD)是信号从一个点传播到另一个点所需要的时间。传输线传播延时是材料相对介电常数的函数。

微带布局传播延时

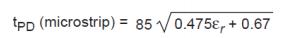

您可以使用公式 5 来计算微带线布局传播延时。

公式 5:

传播延时(tPD)是信号从一个点传播到另一个点所需要的时间。传输线传播延时是材料相对介电常数的函数。

微带布局传播延时

您可以使用公式 5 来计算微带线布局传播延时。

公式 5:

带状线布局传播延时

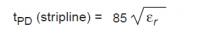

您可以使用公式 6 来计算带状线布局传播延时。

公式 6:

带状线布局传播延时

您可以使用公式 6 来计算带状线布局传播延时。

公式 6:

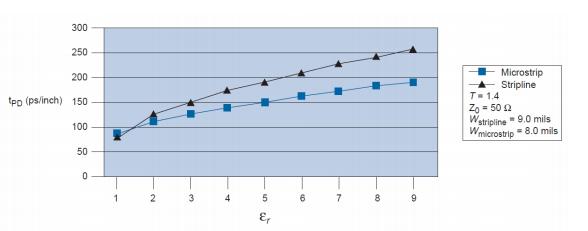

图 9 显示了微带线和带状线传播延时与相对介电常数的关系。随着 εr 的增大,传播延时(tPD)也在增大。

图 9 显示了微带线和带状线传播延时与相对介电常数的关系。随着 εr 的增大,传播延时(tPD)也在增大。

图 9.微带线和带状线传播延时和相对介电常数的关系

图 9.微带线和带状线传播延时和相对介电常数的关系

传播延时(tPD)是信号从一个点传播到另一个点所需要的时间。传输线传播延时是材料相对介电常数的函数。

微带布局传播延时

您可以使用公式 5 来计算微带线布局传播延时。

公式 5:

传播延时(tPD)是信号从一个点传播到另一个点所需要的时间。传输线传播延时是材料相对介电常数的函数。

微带布局传播延时

您可以使用公式 5 来计算微带线布局传播延时。

公式 5:

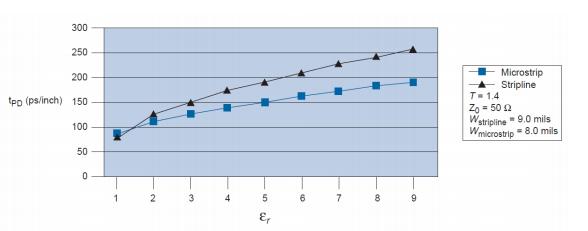

图 9.微带线和带状线传播延时和相对介电常数的关系

图 9.微带线和带状线传播延时和相对介电常数的关系