进行到这一步,应该已经完成原理图绘制和元件封装设计了。接下来要做的工作是将Orcad绘制的原理图转成网表,输入到allegro中,进行PCB设计。

Orcad是一个强大的并且好用的原理图绘制软件,生成的网表可以输入到多种PCB设计工具中,包括Allegro、AD等。导入到Allegro是系统默认的网表生成方式,接下来就让我们看看如何生成网表文件:

1、原理图DRC检查:画完原理图后做的第一件事是进行DRC检查,选中要进行DRC检查的.dsn原理图,工具栏选择tools->Design Rules check,打开Design Rules check选项,进行DRC检查项的设置,如下图所示:

上图中方框中是设置检查报告的输出路径,一般检查完如果有错误,会自动显示报告单,所以此项设置可以不用理会,其他选项系统默认即可。接下来点击Electrical rules进行检查项设置:

如图中所示是所有可以进行DRC检查的检查项,包括单端网络、引脚冲突等等,所有的检查项都可以勾选上,在报告单中提示的错误如果确认没有问题,可以把对应的检查项勾掉,再重新进行DRC规则检查。生成的DRC报告如下图所示:

我生成的检查报告的警告主要有一个问题:WARNING(ORCAP-1611): Two nets in same schematic have the same name, but there is no off-page connector GPS_TIMEPULSE。没有off-page connector,在原理图不同page之间应该加上off-page connector符号,表明输入输出关系,这不是必须要添加的,所以此警告可以忽略。

2、生成网表文件:接下来进入正菜,生成网表文件!DRC检查通过没有问题后,开始生成网表文件,选中要生成网表的.dsn文件,在工具栏点击tools->creat netlist,如下图所示:

在PCB Editor栏,用于设置网表文件的输出路径,网表文件的类型等。首先是勾选create PCB Editor Netlist,在Netlist file中选择生成网表文件的保存路径,系统默认会建立一个allegro的文件夹,可以保存到自动建立的文件夹中,点击…可以选择保存路径,在此使用默认路径。接下来勾选Create or Update PCB Editor Board,意思是创建或更新PCB Editor Board文件,这时会新建一个PCB文件,后缀名为.brd,如果我们自己有建立好的PCB文件,此项可以不勾选,直接生成网表,在我们早已建好的PCB文件中输入网表即可(加下来介绍)。只有勾选了创建或更新PCB Editor文件,才需要设置新建的.brd文件的保存路径,根据个人需要设置即可。最下面红框中用于选择是否打开Allegro PCB Editor软件,在此选择不打开,其他选项不需要设置,默认即可,点击确定,就开始生成网表文件了。如果原理图有问题,那么就不会生成网表,会显示生成网表错误,并会提示错误信息的打印路径,如下图所示:

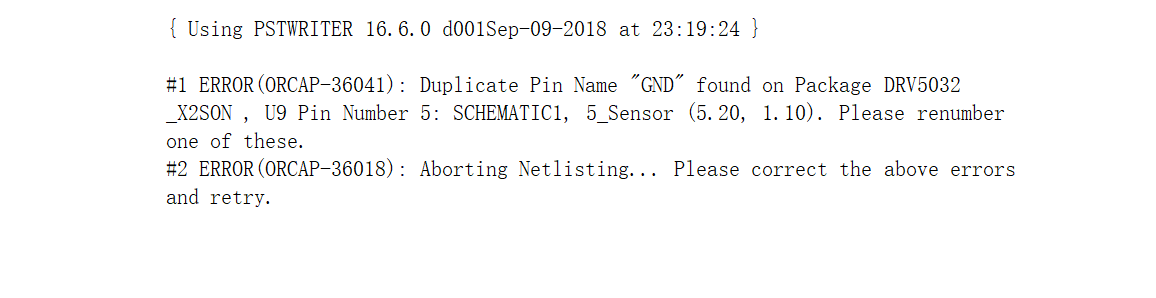

根据提示错误信息保存在ntelist.log中,该文件在之前设置的网表文件存储路径下,打开之后查看是什么错误对应修改即可,如下图所示:

导致该错误的原因是原理图符号中的引脚定义重复了,有两个GND,修改一下原理图符号,把其中一个GND命名修改为GND1即可。首先打开原理图符号,修改命名,修改完成后保存,接下来更新一下design cache,否则系统调用的原理图符号还是之前缓存在内存里的旧原理图符号,更新完成后就可以看到原理图符号改变了。再重新生成网表,直到没有错误为止,修改如下图所示:

3、allegro中导入网表:接下来进行最后一步,将生成的网表导入到allegro中。导入之前需要确定padpath路径和psmpath路径包含原理图网表中用到的所有封装、焊盘、FLash所在的路径,否则输入时会报错显示无法找到封装。设置方法是setup-> user preferences->library->path,设置如下图所示:

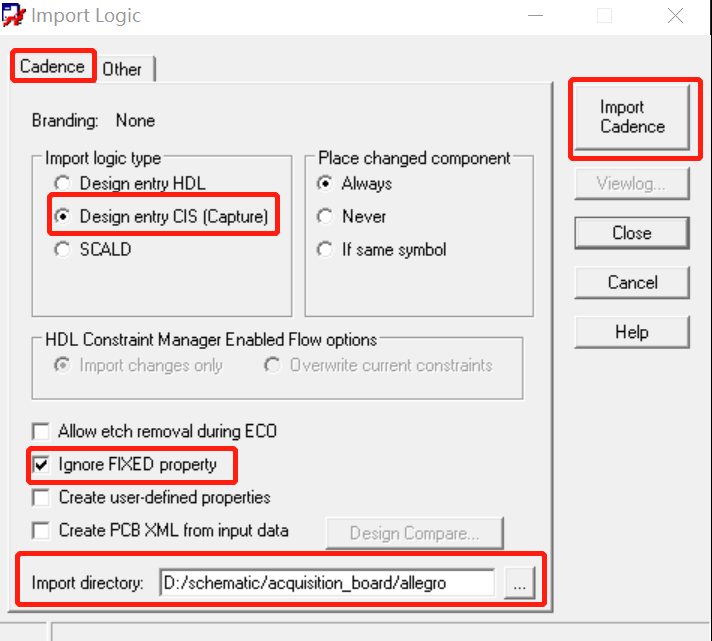

点击…将封装文件路径添加进来。接下来还要画出板的边框outline,否则无法Place元件(板边框绘制会在下篇文章单独介绍)。有了板边框,就可以导入网表了,点击File->Import->Logic,设置网表生成设置,如下图所示:

import logic type选择 Orcad Capture,输入路径选择网表文件的生成路径,点击import Cadence,即可将网表输入到allegro中。如果是其他软件建立的网表,可以在other中设置输入。点击import Cadence后,如果有错误或者警告,会产生提示信息。错误是必须修改的,必须封装的引脚和原理图符号不对应,没有找到封装等。警告是可以忽略的,可改可不改。输入网表成功后,你会发现并没有任何的元件出现在界面中(与AD不同),这是因为Allegro需要点击Place来放置元件到PCB板上。操作方法如下:点击工具栏Place->quickplace,是将所有元件都放置到界面里,在手动布局,如下图所示:

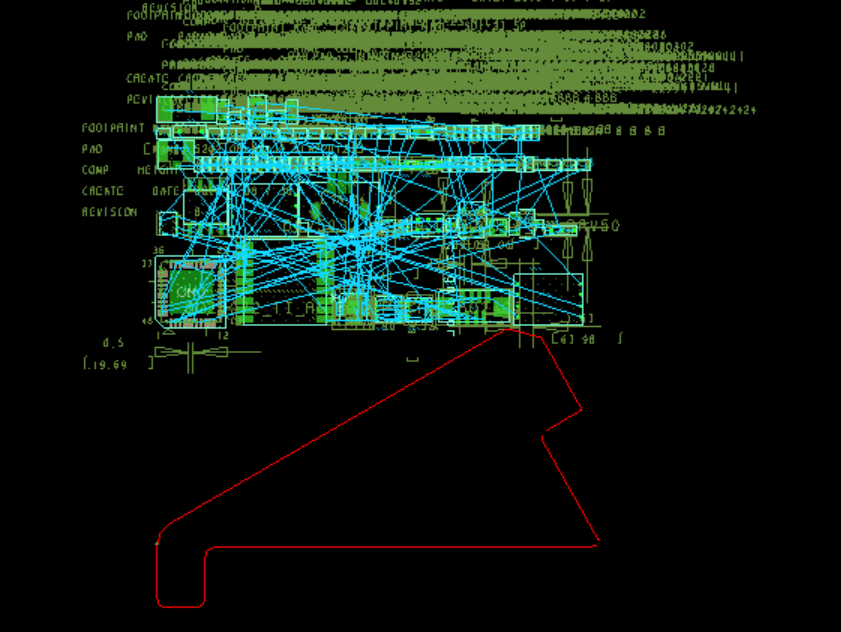

至此,导入网表到allegro的过程就完成了!在这里有两个常用的地方:一是如果原理图修改了,如何保证原有布局不变的情况下只更改变化的部分?二是原理图没有修改,只修改了某个元件封装,如何更新?

第一个的解决方法是在orcad中重新生成网表,这里重点要注意,Create or Update PCB Editor可以不勾选,如果勾选了那么output board file栏一定不能选择布局了元件封装的.brd文件,否则又会生成一个空白的新的.brd文件。

如下图所示:

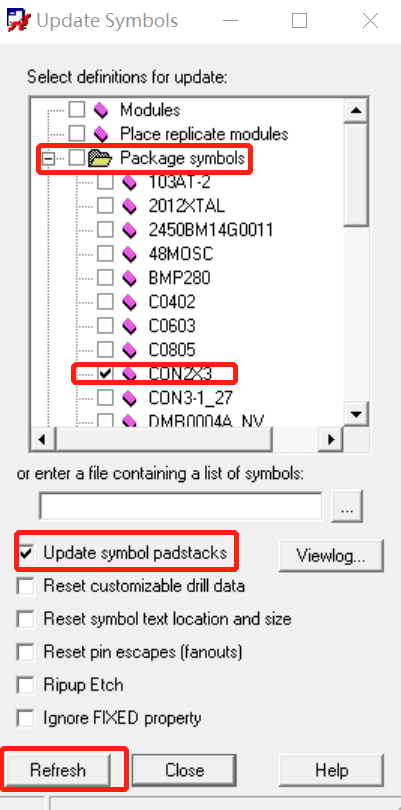

第二个解决办法是选择工具栏Place->Update symbols,选择需要更新的封装名称,如下图所示:

Update padstack一定要勾选,否则焊盘不会被更新!!!!

以上是关于从Orcad中导入网表到Allegro PCB Editor中的方法,如果想了解如何生成封装,可以看我的上一篇博文!

转发请注明来源,谢谢!