在高速、高密度PCB设计中一般提供一个完整的接地平面, 从而使每条信号线基本上只和它最近的信号线相互影响, 来自其它较远信号线的交叉耦合是可以忽略的。尽管如此, 在模拟系统中, 大功率信号穿过低电平输入信号或当信号电压较高的元件( 如 TTL) 与信号电压较低的元件( 如 ECL) 接近时, 都需要非常高的抗串扰能力。在PCB设计中, 如果不正确处理, 串扰对高速 PCB 的信号完整性主要有以下两种典型的影响。1 串扰引起的误触发

信号串扰是高速设计所面临的信号完整性问题中一个重要内容, 由串扰引起的数字电路功能错误是最常见的一种。

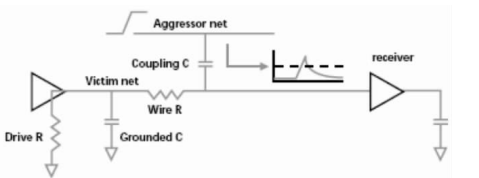

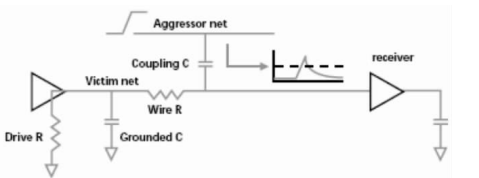

是一种典型的由串扰脉冲引起的相邻网络错误逻辑的传输。干扰源网络上传输的信号通过耦合电容, 在被干扰网络和接收端引起一个噪声脉冲,结果导致一个不希望的脉冲发送到接受端。如果这个脉冲强度超过了接收端的触发值, 就会产生无法控制的触发脉冲, 引起下一级网络的逻辑功能混乱。2 串扰引起的时序延时

是一种典型的由串扰脉冲引起的相邻网络错误逻辑的传输。干扰源网络上传输的信号通过耦合电容, 在被干扰网络和接收端引起一个噪声脉冲,结果导致一个不希望的脉冲发送到接受端。如果这个脉冲强度超过了接收端的触发值, 就会产生无法控制的触发脉冲, 引起下一级网络的逻辑功能混乱。2 串扰引起的时序延时

在数字设计中, 时序问题是一个重要考虑的问题。下图显示了由串扰噪声引起的时序问题。图下半部分是干扰源网络产生的两种噪声脉冲, 噪 声 脉 冲( helpfulglitch) 叠加到被干扰网络, 就引起被干扰网络信号传输延时减少; 同样, 当噪声脉冲( Unhelpful glitch)叠加到被干扰网络时, 就增加了被干扰网络正常传输信号的延时。尽管这种减少网络传输延时的串扰噪声对改善PCB时序是有帮助的, 但在实际PCB设计中, 由于干扰源网络的不确定性, 这种延时是无法控制的, 因而对这种串扰引起的延时必须要加以抑制。

串扰最小化:串扰在高速高密度的PCB设计中普遍存在, 串扰对系统的影响一般都是负面的。为减少串扰, 最基本的就是让干扰源网络与被干扰网络之间的耦合越小越好。在高密度复杂PCB设计中完全避免串扰是不可能的, 但在系统设计中设计者应该在考虑不影响系统其它性能的情况下, 选择适当的方法来力求串扰的最小化。结合上面的分析, 解决串扰问题主要从以下几个方面考虑:1) 在布线条件允许的条件下, 尽可能拉大传输线间的距离; 或者尽可能地减少相邻传输线间的平行长度( 累积平行长度) , 最好是在不同层间走线。

2) 相邻两层的信号层( 无平面层隔离) 走线方向因该垂直, 尽量避免平行走线以减少层间的串扰。

3) 在确保信号时序的情况下, 尽可能选择转换速度低的器件, 使电场与磁场的变化速率变慢, 从而降低串扰。

4) 在设计层叠时, 在满足特征阻抗的条件下,应使布线层与参考平面( 电源或地平面) 间的介质层尽可能薄, 因而加大了传输线与参考平面间的耦合度, 减少相邻传输线的耦合。

5) 由于表层只有一个参考平面, 表层布线的电场耦合比中间层的要强, 因而对串扰较敏感的信号线尽量布在内层。

6) 通过端接, 使传输线的远端和近端终端阻抗与传输线匹配, 可大大减小串扰的幅度。

资料来源:一牛网论坛关键词:PCB、PCB设计

信号串扰是高速设计所面临的信号完整性问题中一个重要内容, 由串扰引起的数字电路功能错误是最常见的一种。

是一种典型的由串扰脉冲引起的相邻网络错误逻辑的传输。干扰源网络上传输的信号通过耦合电容, 在被干扰网络和接收端引起一个噪声脉冲,结果导致一个不希望的脉冲发送到接受端。如果这个脉冲强度超过了接收端的触发值, 就会产生无法控制的触发脉冲, 引起下一级网络的逻辑功能混乱。2 串扰引起的时序延时

是一种典型的由串扰脉冲引起的相邻网络错误逻辑的传输。干扰源网络上传输的信号通过耦合电容, 在被干扰网络和接收端引起一个噪声脉冲,结果导致一个不希望的脉冲发送到接受端。如果这个脉冲强度超过了接收端的触发值, 就会产生无法控制的触发脉冲, 引起下一级网络的逻辑功能混乱。2 串扰引起的时序延时在数字设计中, 时序问题是一个重要考虑的问题。下图显示了由串扰噪声引起的时序问题。图下半部分是干扰源网络产生的两种噪声脉冲, 噪 声 脉 冲( helpfulglitch) 叠加到被干扰网络, 就引起被干扰网络信号传输延时减少; 同样, 当噪声脉冲( Unhelpful glitch)叠加到被干扰网络时, 就增加了被干扰网络正常传输信号的延时。尽管这种减少网络传输延时的串扰噪声对改善PCB时序是有帮助的, 但在实际PCB设计中, 由于干扰源网络的不确定性, 这种延时是无法控制的, 因而对这种串扰引起的延时必须要加以抑制。

串扰最小化:串扰在高速高密度的PCB设计中普遍存在, 串扰对系统的影响一般都是负面的。为减少串扰, 最基本的就是让干扰源网络与被干扰网络之间的耦合越小越好。在高密度复杂PCB设计中完全避免串扰是不可能的, 但在系统设计中设计者应该在考虑不影响系统其它性能的情况下, 选择适当的方法来力求串扰的最小化。结合上面的分析, 解决串扰问题主要从以下几个方面考虑:1) 在布线条件允许的条件下, 尽可能拉大传输线间的距离; 或者尽可能地减少相邻传输线间的平行长度( 累积平行长度) , 最好是在不同层间走线。

2) 相邻两层的信号层( 无平面层隔离) 走线方向因该垂直, 尽量避免平行走线以减少层间的串扰。

3) 在确保信号时序的情况下, 尽可能选择转换速度低的器件, 使电场与磁场的变化速率变慢, 从而降低串扰。

4) 在设计层叠时, 在满足特征阻抗的条件下,应使布线层与参考平面( 电源或地平面) 间的介质层尽可能薄, 因而加大了传输线与参考平面间的耦合度, 减少相邻传输线的耦合。

5) 由于表层只有一个参考平面, 表层布线的电场耦合比中间层的要强, 因而对串扰较敏感的信号线尽量布在内层。

6) 通过端接, 使传输线的远端和近端终端阻抗与传输线匹配, 可大大减小串扰的幅度。

资料来源:一牛网论坛关键词:PCB、PCB设计